Формирователь адресного сигнала для оперативного запоминающего устройства

Иллюстрации

Показать всеРеферат

1. ФОРМИРОВАТЕЛЬ АДРЕСНОГО СИГНАЛА ДЛЯ ОПЕРАТИВНОГО ЗАПОМИНАЮ1ЧЕГО УСТРОЙСТВА, содержащий первый адресный транзистор, транзистор свя зи, второй адресный транзистор, источник тока, первый и второй резисторы , первый вывод источника тока соединен с первой адресной шиной и коллектором первого адресного транзистора , эмиттер которого подключен к первому выводу первого резистора, база первого адресного.транзистора соединена с первым выводом второго резистора, эмиттер транзистора связи соединен с первым выводом второго резистора, коллектор подключен к шине источника питания, база тран зистора связи соединена с коллектором второго адресного транзистора, база второго адресного транзистора подключена к шине управления, а вторые выводы резисторов и источника тока подключены к общей итне, отличающийся тем, что, с целью уменьшения потребляемой мощности формирователя, он ссщержит дополнительный источник тока, первый вывод которого соединен с шиной управления , а второй вывод подключен к общей шине, эмиттер второго адресного транзистора соединен с второй адресной шиной. 2.Формирователь ло п. 1, отличающийся тем, что эмиттер транзистора связи подключен к шине источника питания, а коллектор к базе первого адресного транзистора ., 3.Формирователь по п. 1, о т ли ч ающийся тем, что коллектор транзистора связи подключен ко второй адресной шине. 4.Формирователь по п. 1, о тли чающийс я тем, что коллектор транзистора связи соединен с шиной управления. 5.Формирователь по пп. 1-4, отличающийся тем, что формирователь содержит дополнительнь1й источник питания в виде резистора, первый вывод которого соединен с шиной управления, а второй вывод с общей шиной. .

СОЮЗ СОВЕТСКИХ

CCIIW

РЕСПУБЛИК

3(5g . G 11 С-11 40

ОПИСАНИЕ ИЗОБРЕТЕНИ

К АВТОРСКОМУ СВИДЕТЕПЪСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРИТЗФ (21) 3350306/18-24 (22) 29.10.81 (46) 30.04.83. Вюл. 9 16 (72) Т.Я. Мамедов и А.И. Сухопаров (53) 681.327.6(088.8) (56) 1."IEEE Trans. Ee . Веч.", 1979, 9 6, с. 886-892.

2. "1$$СС 0>gest of JechnicaI

Papers", 1979, с. 108 (прототип). (54)(57) 1. ФОРМИРОВАТЕЛЬ АДРЕСНОГО

СИГНАЛА ДЛЯ ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА, содержащий первый адресный транзистор, транзистор связи, второй адресный транзистор, источник тока, первый и второй резисторы, первый вывод источника тока соединен с первой адресной шиной и коллектором первого адресного транзистора, эмиттер которого подключен к первому выводу первого резистора, база нервого адресного, транзистора соединена с первым выводом второго резистора, эмнттер транзистора связи соединен с первым выводом второго резистора, коллектор подключен к шине источника питания, база транзистора связи соединена с коллектором второго адресного транзистора, база второго адресного транзистора подключена к шине управления, а вторые выводы резисторов и источни..80„„ДДД439 А ка тока подключены к общей шине, отличающийся тем, что, с целью уменьшения потребляемой мощности формирователя, он содержит дополнительный источник тока, первый вывод которого соединен с шиной управления, а второй вывод подключен к общей шине, эмиттер второго адресного транзистора соединен с второй адресной шиной.

2. Формирователь по п. 1, о тл и ч а ю шийся тем, что эмиттер транзистора связи подключен к шине источника питания, а коллектор к базе первого адресного транзистора.

3. Формирователь по п. 1., о т - Я л и ч а ю шийся тем, что коллектор транзистора связи подключен ко второй адресной шине, 4. Формирователь по п. 1, о тл и ч а ю щ и и с я тем, что коллектор транзистора связи соединен с шиной управления.

5. Формирователь по пп. 1-4, о тл и ч а ю шийся тем, что фор- мирователь содержит дополнительный источник питания в виде резистора, первый вывод которого соединен с шиной управления, а второй вывод— с общей шиной.

1015439

Изобретение относится к интегральной схемотехнике, в частности к биполярным интегральным схемам памяти.

Известны формирователи сигнала адреса оперативного эапоминаюцего устройства (ОЗУ), включающие в себя помимо тока хранения источник точ, ка выборки, подсоединенный через развязываюцие диоды к одной из двух адресных шин каждой строки элементов памяти (ЭП) и обеспечивающий ускоренное понижение уровня напряжения на адресных шинах по окончании цикла обрацения к строке ЭП (1 ).

Недостаток данных схем заключает- 15 ся,либо в существенном замедлении процесса перевода строки ЭП в режим покоя начиная с момента достижения одинаковых уровней напряжения на адресных шинах ЭП, выбираемых в соседних циклах обращения, либо в недостаточной энергетической эффективности и большой площади, занимаемой ими на кристалле.

Наиболее близкой к предлагаемой по технической сущности является схема, которая содержит шину управления, первую и вторую адресные шины, генератор тока хранения, первый вывод которого подсоединен ко второй адресной шине, а второй — к отрицательному полюсу источника питания, первый п-р-п-транзистор, коллектор которого подсоединен ко второй адресной шине, а эмиттер и база — к первым выводам соответственно первого и второго резисторов, вторые выводы которых соединены с отрицательным полюсом источника питания, второй п-р-п-транзистор, коллектор которого подсоединен к положительно- 40 му полюсу источника питания, эмиттер — к базе первого транзистора, а база — к коллектору третьего п-р-птранзистора, база которого соединена с шиной управления, эмиттер — 45 с первым. выводом третьего резистора, коллектор — с первыми выводами четвертого резистора и первого конденсатора, а шина управления, в свою очередь, — с положительным полюсом источника опорного напряжения, второй конденсатор, первый вывод которого подсоединен к базе первого транзистора, а второй - к отрицательному потпосу источника опорного напряжения. Вторые вывОды первого конденсатора и четвертого резистора подсоединены к положительному полюсу источника, питания, а второй вывод третьего резистора — к отрица- ®, тельному полюсу источника питания(2). ® .Недостатками известной схЕма явля ютсг, потребление мощности в режиме покоя, что может приводить к суцественному увеличению мощности, потребляемой большой интегральной схе- 65 мой памяти, так как количество схем, формирователя сигнала адреса ОЗУ рав.но количеству строк в матрице ЭП, а также значительная площадь, занимаемая схемой на кристалле, что связано с наличием в ней реэистивноемкостных цепей с большими постоянными времени, обуславливающими задержку выключения тока, форсирующего понижение потенциала на адресной шине строки ЭП, которая выбиралась в цикле, предшествующем текущему циклу обр щения, величина постоянной времени RC-цепи контролируется номиналами резистора и конденсатора, выполняемого обычно в интегральных схемах в виде обратно смеценного р-и-перехода, которые пропорциональны плоцади соответствуюцих схемных элементов.

Цель изобретения — уменьшение мощности, потребляемой формирователем .. !

Поставленная цель достигается тем, что формирователь адресного сигнала для оперативного запоминающего устройства, содержащий первый адресный транзистор, транзистор связи, второй адресный транзистор, источник тока, первый и второй резисторы, первый вывод источника тока соединен с первой адресной шиной и коллектором первого адресного транзистора, эмиттер которого подключен к первому выводу первого резистора, база первого адресного транзистора соединена с первым выводом второго ,резистора, эмиттер транзистора свя зи соединен с первым выводом второго резистора, коллектор подклЮчен к шине источника питания, база транзис тора связи соединена с коллектором второго адресного транзистора, база второго адресного траэистора подключена к шине управления, а вторые выводы резисторов и источника тока подключены к обцей шине, содержит дополнительный источник тока, первый вывод которого соедичен с шиной управления, а второй вывод подключен к общей шине, эмиттер второго адресного транзистора соединен со второй адресной шиной.

Эмиттер транзистора связи подключен к шине источника питания, а коллектор - к базе первого адресноiго транзистора..

Коллектор транзистора связи подключен ко второй адресной шине.

Коллектор транзистора связи соединен с шиной управления, Формирователь содержит дополнительный источник питания в виде резистора, первый вывод которого соединен с шиной управления, а второй вывоц — с общей шиной.

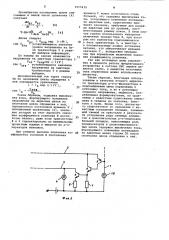

На фиг. 1 изображена электричес. кая схема устройства; на фиг. 2 1015439 и 3 - -формирователи сигнала адреса

ОЗУ.

Предлагаемая схема включает в себя шину 1 управления, первую 2 и вторую 3 адресные шины, основной источник 4 тока, первый вывод которого подсоединен ко второй адресной шине 3, а второй - к отрнцательйому полюсу источника питания, первый адресный транзистор 5, коллектор которого подсоединен ко второй адресной шине 3, а эмиттер и база - к первым выводам соответственно первого 6 и второго 7 резисторов, вторые выводы которых соединены с отрицательным полюсом источника питания, )5 транзистор связи 8, коллектор которого подсоединен к положительному полюсу источника питания, эмиттер— к базе .первого адресного транзистора 5, а база — к коллектору вто- д) рого адресного транзистора 9, база которого, в свою очередь, соединена с шиной 1 управления, эмиттер— с первой адресной шиной 2, шина 9 управления через дополнительный источник 10 тока соединена с отрицательным полюсом источника питания.

На фиг . 2 и 3 изображены форми-.. рователи сигнала адреса ОЗУ, в которых коллектор транзистора связи подсоединен соответственно к первой адресной шине и к базе второго . адресного транзистора.

Формирователь адресного сигнала

ОЗУ работает:ледующим образом.

Скорость нарастания потенциала на адресных шинах 2 и З,достаточно высока благодаря использованию эмиттерных повторителей или усили-. телей Дарлингтона (не показаны).

Для достижения высокой скорости спа- 40 да уровня напряжения на адресных шинах 2 и 3 после окончания цикла обращения используется дополнительный ток, протекающий через строку

ЭП в режиме выборки. Этот ток обес- 45 печивается транзистором 5. При выборке строки, т.е. при повышении уровня напряжения .на адресных шинах 2 и )В данной строки, ток источника 10 тока через шину 1 управления, являющуюся общей для всех строк накопителя,. поступает в базу транзистора 9, что приводит к повышению уровня напряжения на базах транзисторов 8 и 5, транзистор 5 переходит из режима отсечки в нормальный активный режим, увеличивая ток, протекающий через строку элементов памяти (не показаны), включенную между шинами 2 и 3.

При повйшении потенциала на адрес-60 ных шинах 2 н 3 строки, выбираемой в следующем цикле обращения, ток источника 10 тока начинает ответвляться в базу транзистора 9 данной строки. Однако дополнительный ток, про- i g5 текающий через строку ЭП, которая собиралась в предыдущем цикле обращения, выключается с задержкой, в результате чего сохраняется высокая скорость понижения уровня напряжения на. адресных шинах 2 и 3 строки. Процесс изменения потенциала на базах транзисторов 8 и 5 опи сывается системой дифференциальных уравнений

® Ье —. - 3%5» фъэв+ ъкв+ ъэв) ав + еъэ ъв = бй э — ,(В+1) й1

1 (1) auá — Вибо 8(+c +с +с 1 — "=

Ьзе 3% ЬэЕ .@ЗА Ьк5 01! З ; ..l, (2) аО аиде

Я (э) из уравнений (1), (2) и (3) получают

-t(1

- 6е е+ ек9)(8+ ) ею ьи+ ю1

ОЬ

R÷ (4) где R, величина оопро ивле ния резистора 7,э.

CA„ — усредненная емкость резистора 7;

СЬэ f СЬк УсреДненные емкости соответственно эмнттерного и коллекторного и коллекторного р-и-переходов транзистора 5

С, („Е- усредненные емкости соответственно эмиттерного и коллекторного р-п-переходов транзистора 8;

С5 9- усредненная емкос гь бк9 коллекторного р-иперехода транзисто-. ра 9

— коэффициент усиления транзистора 8.

Так как узел,,к которому подключена база транзистора 8, разряжается лишь базовым током этого тран-. зистора, величина которого мала, скорость изменения напряжения в этом узле определяет и скорость изменения напряжения на базе и эмнттере транзистора 5.

Таким образом, 1015439

Пренебрегая последними тремя слагаемыми в левой части уравнения (4) получают

65 65 . (5) С=<ЬВУ С +С >R (Ьф бК8 бК9) 1

Далее следует

ЦЫв ехр (- tW) где U - установйвшееся значение уровня напряжения на, базе транзистора 5 в режиме выборки информации.

По такому же закону изменяется напряжение на эмиттере транзистора 5

U.р5 = 0э ехр (- t/ь ) где U - установившееся значение напряжения на эмиттере транзистора 5 в режиме выборки.

Дополнительный ток через строку

ЭП по окончании цикла обращения к ней описывается уравнением

1 = 1> ехр (-t/ ),. где 1 э 5 з

s к

Таким дбразом, задержка выключения гока, форсирующего понижение напряжения на адресных шинах по окончании цикла обращения к ней, определяется постоянной времени с описываемой уравнением (6), значение которой за счет высокого значе ния коэффициента усиления В доста- . точно велико, даже если транзисторы

:8 и 9 спроектированы по минимальным

"проектным нормам и емкости их р-ппереходов невелики, При слишком высоких значениях ко-, эффициейта усиления В постоянная времени.Т может получиться. столь большой, что задержка выключения тока, ускоряющего понижение потенциала адресных шин, существенно превысит значение, требуемое для разряда адресных шин до уровней, соответствующих режиму покоя. В этом случае удобно испольэовать инверсное включение транзистора 8, при котором его коллектор подсоединяется

10 к базе транзистора 5, а эмиттер к положительному-полюсу источника питания, что обеспечивает меньшие значения Г, вследствие меньших чем при нормальном включении значе15 ний коэффициента усиления.

Так как потенциал шины управления в процессе работы предлагаемого устройства в составе БИС памяти меняется слабо, в качЕстве источниКа тока управления можно использовать резистор.

Таким образом, благодаря использованию в качестве второго адресного транзистора р-и-р-з ранзистора и ° подсоединению шины управления к источнику тока, а не к источнику опорного напряжения, мощность; потребляемая формирователем, по сравнению с известным существенно уменьшена и сведена до значения, близкого к нулю. Кроме того, достигнуто существенное по сравнению с известным сокращение площади, занимае-. мой схемой на кристалле в результате устранения ряда схемных элеменЗ5 тов и дополнительных p-n-переходов большой площади, выполняющих роль конденсаторов в резистивноемкостных цепях задержки выключения тока, форсирующего понижение потенциала

4р на адресных шинах строки ЭП после окончания цикла обращения к ней.

10154.39

Фие. 3

Составитель В. Теленков

Редактор Л. Пчелинская Техред X.Кастелевич Корректор .

Заказ:3224/49 Тираж 594 Подписное.

ВНИИПИ .Государственного комитета СССР по делам изобретений и открытий

113035, NocKBa, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4