Вычислительное устройство

Иллюстрации

Показать всеРеферат

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее блок умножения, сумматор, регистр аргумента и регистр промежуточного результата, отличающееся тем, что, с целью повышения быстродействия и расширения функциональных возможностей его путем обеспечения возможности вычисления h функций5- А-Х:ч В- м5„ Ц1л-Х, , в него введены первый и второй буферные регистры, первый и второй коммутаторы ;11рич м установочные входы первого и второго буферных регистров являются соответственно входами первого и второго коэффициентов устройства, управляющие входы первого и второго коммутаторов являются соответственно первым и вторым управляющими входами устройства, установочные входы регистра аргумента являются группой входов. apryMeMta устройства, выходы первого буферного регистра соединены с первой группой информационных входов первого коммутатора, выходы которого соединены с первой группой входов сумматора, вторая группа входов которого подключена к выходгил блока умножения , а выходу сумматора являются (Л группой выходов устройства, и соединены с установочньши входами регистра промежуточного результата, выходы которого соединены со вторыми группами входов первого и второго коммутаторов,причем первая группа входов второго коммутатора подключена к выходам второго буферного регистра, а выходы второго коммутатора соединены с первой группой входов блока умнокения, о: вторая группа входов которого подклю-. чена к выходам регистра аргумента. sj « со

(19) (11)

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

3(Я) G 06. F 7 38

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPGHOMY СВИДЕТЕЛЬСТВУ (21) 3368503/18-24 (22) 02.11.81 (46.) 07.05.83. Вюл. 9 17 (72) Л,В.Вариченко, В.И.Жабин, Э.Д.Коноплянко, В.И.Корнейчук, М.A.Раков, A.È.Cåëåçíåâ, В.П.Тарасенко и В.В.Ткаченко (7).) Киевский ордена Ленина политехнический институт имени 50-летия Великой Октябрьской социалистической революции (53) 681.325.66(088.8) (56) 1. Авторское свидетельство СССР

9 744559, кл. G 06 F 7/38, 1980.

2. Патент CtdA 9 4142242, кл. а 06 Г 7/38, опублик. 1979.

3 ° Патент Японии 9 53-24264, кл. 97(7), опублик. 1978 (прототип). (54)(57) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержашее блок умножения, сумматор, ррегистр аргумента и регистр промежуточного результата, о т л и ч а ю— щ е е с я тем, что, с целью повышения быстродействия и расширения функциональных возможностей его путем обеспечения возможности вычисления n

Функций5. =A.)(. +Â и S =) А.Х), s не

j j j n го введены первый и второй буферные

"регистры, первый и второй коммутаторы, причем установочные входы первого и второго буферных регистров являются соответственно входами первого и второго коэффициентов устройства, управляюшие входы первого и второго коммутаторов являются соответственно первым и вторым управлякщими входами устройства, установочные входы регистра аргумента являются группой входов. аргумента устройства,. выходы первого буферного регистра соединены с перввй группой информационных входов первого коммутатора, выходы которого соединены с первой группой входов сумматора, вторая группа входов кото. рого подключена к выходам блока умно-Е жения, а выходу суввлатора являются группой выходов устройства.и соедине ны с установочными входами регистра промежуточного результата, выходы которого соединены со вторыми группами входов первого и второго коммутато- Я ров,прнчем первая группа входов второго коммутатора подключена к выходам второго буферного регистра, а выходы ©) второго коммутатора соединены с первой группой входов блока умножения, вторая группа входов которого подклю- чена к выходам регистра аргумента. 3

1016779

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных маШинах и системах для .получения значеи .ний функций5;=Я Х.+8 5 = A Õ. и 5

1=1

Ы -В Х 1+В Хп 2+...+В„,ХП К+...+В „Х Вл .И:.

Известно устройство для вычисления значения полинома m-ой степени, со, держащее устройство управления, три 10 сдвигающих регистра, четыре элемента

И„ счетчик переносов и сумматор (1).

Недостатками известного устройст" ва являются невозможность вычисления

15 величины 5 =Z А,Х.,а также низкое и быстродействие при формировании значений полинома m"îé степени и выражения S„- =М; Х,-+В, Известно множительно-накопительное устройство содержащее блок умно" жения, приемные регистры операндов, накопитель и отклоняющий блок (2).

Такое устройство позволяет полу" и 25 чать значения =) . А.Х;.однако не

1=1

1 может быть использовано для вычисления значений полиномов и выражения

Б.=А„ Х„гв„, т.е. обладает узкими Функ- 3О циональными возможностями.

Наиболее близким к предлагаемому является устройство.для вычисления суммы степенного ряда, В схеме устройства имеется операционный блок для выполнения операций умножения и . суммирования, регистры аргумента и промежуточного результата, а также сдвигавая память для хранения значений коэффициентов А;(3).

Такое устройство характеризуется низким быстродействием, поскольку для вычисления полинома и-й степени сначала происходит формирование членов полинома, а затем выполняется их суммирование. для получения i-ro чле-45 на устройством вычисляется произведение Х " Х (где Х вЂ” аргумент), а за-. тем происходит умножение коэффициента A . íà i-ую степень аргумента, т.е, 1

Х. Время формирования результата в 50 этом случае 1= и4 +(иг1)1С где время умножения двух операндов, время сложения двух операндов.

Кроме того, прототип обладает узкими функциональными возможностями, 55 так как не позволяет вычислять значеп ния функций 5.- ., +й, и S = А Х.i 1 i 1 1 j

Цель изобретения — повышение быст- 6О родействия и расположение функцио" нальных возможностей путем обеспечения возможности вычисления функций

Ф и

S.=P,.Х,. В,. и S„= ß,.Õ, 65

Поставленная цель достигается тем, что в вычислительное устройство, содержащее блок умножения, сумматор, ;регистр аргумента и регистр промежуточного результата, введены первый и второй буферные регистры, первый и второй коммутаторы, причем установочные входы первого и второго буферных регистров являются соответственно входами первого и второго коэффи" циентов устройства, управляющие входы первого и второго коммутаторов являются соответственно первым и вторым управляющими входами устройства, установочные входы регистра аргумен.та являются группой входов аргумента устройства, выходы первого буферного регистра соединены с первой группой информационных входов первого коммутатора,выходы которого соединены с первой группой входов сумматора, вторая группа входов которого подключена к выходам блока умножения, а выходы сумматора являются группой выходов устройства и соединены с установочными входами регистра промежуточного результата, выходы которого соединены с вторыми группами входов первого и второго коммутаторов, причем первая группа входов второго коммутатора подключена к выходам второго буферного регистра, а выходы второго коммутатора соединены .с первой группой входов блока умножения, вторая группа входов которого подключена к выходам регистра аргумента.

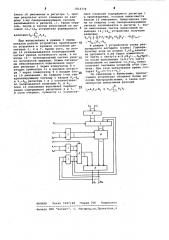

На чертеже представлена структурная схема устройства.

Вычислительное устройство содержит первый буферный регистр 1, регистр 2 аргумента и второй бу<(герный регистр 3. Входы 4„-4 первого коэффициента подключенй к установочным входам регистра 1, входы 5„-5. аргумента — к установочным входам регистра 2, а входы 61-6и,второго коэффициента — к установочным входам регистра 3, В состав устройства также входят регистр 7 промежуточного результата, первый коммутатор 8, второй коммутатор 9, блок 10 умножения и сумматор 11, выходы которого являют ся выходами 12 12,„ óñòðîéñòâà, и к ним подключены входы регистра 7. К управляющему входу коммутатора 8 подсоединен первый вход 13 управления, а к управляющему входу коммутатора

9 — второй вход 14 управления. Выходы регистра l соединены с первой группой входов коммутатора 8, выходы которого подключены к первой группе входов сумматора 11, вторая группа входов сумматора 11 соединена с выходами блока 10 умножения, первая группа входов которого подключена к выходам регистра 2, а вторая группа входов — к выходам коммутатора 9. Первая группа входов коммутатора 9 сое1 01.б-77 9 з динена с выходами регистра 3, а вторая группа входов -.c второй группой входов коммутатора 8 и вьиодами ре- гистра 7.

Блок 10 умножения предназначен для перемножения m-разрядных двоичных операндов. Сумматор 11 — это m-разрядный параллельный сумматор комбинационного типа °

Вычислительное устройство может работать в одном из трех режимов, зараваемых потенциальными логическими сигналами на входах 13 и 14. В каждом режиме вычисляется значение функции в соответствии с приводимой ниже таблицей режимов работы.

Регистры 1-, 2, 3 и 7 представляют собой m-разрядные регистры (где m-Разрядность поступающих операндов) .с параллельной записью и выдачей информации. Входы управления записью информации в эти регистры на чертеже услов-30 но не показаны.

Вычисляемая Функция

Вход

Режим работы

О

S. =A1х1+В1 и

Бп 1Х1+а2Х ...+A хо= Ъ.Х ° =1

s ((((О х1+в )х2+В2)ХХ

+В ° ) Х „+, . ° +В„„) Х +В ляется при каждом i-ом синхронизирующем сигнале, поступающем на входы разрешения записи информации регнстрой. После приема информации в регистры устройства блок 10 умножения Формирует произведение й;Х, старшие т разрядов которого постуйают на входы сумматора 11. Последний осуществляет вычисление суммы 5;=М;Х;+6;, которая в данном режиме является окончательным результатом и устанавливается на выходах 12-12 устройства.

Перед началом работы устройства в режиме 2 регистры 2,3 и 7 устанавливаются в нулевое состояние, а на вход

13 подается потенциальный сигнал уровня логической единицы, на входе 14 остается сигнал уровня логического руля. Сигнал логической единицы переключает коммутатор 8 таким образом, что выходы регистра 7 оказываются подключенными к входам сумматора 11.

Работа устройства в этом режиме начинается с момента поступления синхронизирукщих.сигналов на входы разрешения записи информации регистров 2,3 и 7. При этом в регистр 2 с входом 51-5„ поступает величина х;, а с входов б1-б,„в регистр 3 - величина и ° . После йриема величин в ре( гистры 2 и 3 блок 10 умножения осуществляет перемножение содержимого этих регистров и формирует на своих выходах. m-разрядный двоичный код величины А Х . Сумматор ll выполняет 4 j сложение двоичных кодов на выходах

В таблице приняты следующие обозначения1 S и S< — результат вычислений,.В; и A; — соответственно первый и втоРой коэффициенты, Х, — аРгУмент.

Кроме того, поскольку в режиме 3 реализуется алгоритм (схема) Горнера, устройством можно вычислять значения полинома следукщего вида (если-Х =

xz=...-=x =õ =õ);

П-1

40.Ь -Ь„)(+В X +.. +В Х +...Фь Х + и, +5 X+5 =W S. Xn-" .8-.1 П,,„

Рассмотрим работу вычислительного устройства последовательно во всех трех режимах.

Для задания режима 1 на входах 13 и .14 устанавливаются потенциальные 5О сигналы уровня логического нуля. Коммутаторы 8 и 9 по этим сигналам под-. ключают к выходам первые группы своих входов. Таким образом, выходы регистра 1 через коммутатор 8 подключаются к.первой группе входов сумматора .11, а выходы регистра 3 - к первой группе входов блока 10 множения через коммутатор 9. Регистры 1,2 и 3 устанавливаются в нулевое состояние.

На входы 41 —.4 „,51- 5п и 61-.б,„поступают двоичнйе кодй величийы соответственно первого коэффициента B аргумента Х; и второго коэффициен-. та A Запись укаэанных величин соответственно B регистры 1,2 и 3 осуществ- б5

1016779

ВНИИПИ Заказ 3387/48 Тираж 706 Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 блока 10 умножения и регистра 7, причем результат этого сложения по каж дому 1-му синхронизирующему сигналу записывается в регистр „7. Таким образом, после и тактов вычислений на выходах 121-12П1 устройства Формируется 5

l1 величина 5,=) Я,)(. и 1-1 i i

При вычислейиях в режиме 3 перед началом работы устройства производит- f() ся установка в нулевое состояние регистров 1, 2 и 7. Кроме того, на входе 13 устанавливается йотенциальный сигнал уровня логического нуля, а на входе 14 - потенциальный сигнал уров-15 ня логической единицы. Этими сигналами обеспечивается подключение выходов регистра 1 через коммутатор 8 к входам сумматора 11 и выходов регистра 7 через коммутатор 9 к входам бло- О ка 10 умножения, По каждому 1-му синхрониэирукицему сигналу с входов 41-4 и 51-5„, регистры 1 и 2 соответственно эапйсываются величины В,. и Х, Блок 10 умножения. выполняет перемножение содержимого регистров 2 и 7.

В свою очередь, сумматор 11 осуществляет сложение содержимого регистра 1 и произведения, которое вычисляется блоком 10 умножения. Вычисленная сумма по каждому i-му синхронизирующему сигналу записывается в регистр 7, После выполнения тактов вычислений на выходах 12 -12 устройства получаем

1 m величину

5„=Д..((О X„+5„)X +Ь )X +...+В;)Х,,„+...

В режиме 3 устройством также реализируется алгоритм (схема) Горнера.

Поэтому если на входах 5„+5„,величи" на аргумента Х;не будет изменяться от такта к такту (т, е. Х =Х =... Х,дХ„=Х), то после выполнения (n+1) -го такта вычислений на выходах 12„+12 будет получено значение полинома и-ой сте- . пени. При этом затраченное время составит t>>=(n1)(y++ )

По сравнению с известным, предлагаемое устройство обладает более вы-, соким быстродействием, а также возможностью вычисления функций fl

-,= .)(° + Ь. и Б =) А

1- 1