Устройство для вычитания

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (И) ЗСЮ С 06 F 7/50

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H ABTOPCHOMY СВИДЕ П.:ЛЬСТВ У (21) 3385778/18-24 (22) .29. 01. 82 (46) 07.05.83. Бюл.. В 17 (72) В.A. Горних (711 Институт технической кибернетики AH Белорусской ССР (53) 6Я1.325.5(088.8) (56) 1. Авторское свидетельство СССР

М 686029, кл. (06 F 7/50, 1977.

2. Авторское свидетельство СССР

Р 771668, кл. 6 06 F 7/50, 1979 (прототип ); (54)(57) УСТРОИСТВО ДЛЯ ВЫЧИТАНИЯ, содержащее генератор импульсов, первый и второй счетчики, триггер и первый элемент И, первый вход которого соединен с выходом генератора импульсов, а выход подключен к первым входам первого и второго счетчиков, прямой выход триггера подключен к знаковому выходу устройства, нулевой вход триггера и .установочные входы первого и второго счетчиков подключены к управляющему входу устройства, о т л и ч а— ю щ е е с я тем, что, с делью повышення быстродействия, в него введены компаратор, второй и третий элементы И и третий. счетчик, причем входы компаратора соединены с вы ходами разрядов первого и второго счетчиков, а выход — с единичньиа входом триггера, первый вход второго элемента И соединен с выходом младшего разряда первого счетчика, второй вход соединен с инверсным выходом триггера, а выход — с вто.рым входом второго счетчика, первый вход третьего элемента И соединен с выходом младшего разряда второго счетчика, второй вход соединен с ярявим выходом триггера, а выход -. с вторым входом первого счетчика, выходы младшего разряда первого и второго счетчиков соединены с входами старшего разряда первого и второго счетчиков соответственно, вход третьего счетчика соединен с выходом генератора импульсов, установочный вход — с установочным входом устройства, а выход — с BT0- . рым входом первого элемента И.

1016781

Изобретение относится к вычислительной технике и может быть использовано в системах обработки информации, в системах управления и контроля.

Известно устройство для вычитания, содержащее три счетчика, триггеры, элементы И и ИЛИ и генератор импульсов (1 .

Недостатком известного устройства является низкое быстродействие.

Известно также устройство для вычитания, содержащее два счетчика, триггер, генератор импульсов и элемент И. Первый вход элемента И соединен с выходом генератора импульсов, а выход подключен к входам счетчиков, выходы разрядов первого из которых соединены с информационными выходами устройства, прямой выход триггера подключен к знаковому выходу устройства, нулевой .вход триггера и установочные входы счетчиков подключены к управляющему.входу устройства, а также два дешифратора нуля, входы каждого из которых соединены .с выходами разрядов соответствующего счетчика, выход первого дешифратора нуля соединен с единичным входом триггера, прямой выход которого подключен к входу управления сложением, а инверсный выход — к входу упрамления вычитанием первого счетчика, инверсный выход второго дешифратора нуля подключен к второму входу элемента И.

Принцип действия этого устройства основан на последовательном вычитании единичных импульсов из двух регистров-счетчиков, в которых хранятся коды исходных чисел. Вычитание происходит до обнуления счетчика, в котором было записано вычитаемое. При этом, если первым обнулится счетчик Уменьшаемого, то

его режим работы переключится на сложение. Результат вычитания фиксируется всегда в прямом коде t.2 3.

Недостаток этого устройства состоит в невысоком быстродействии, обусловленном тем, что количество тактов работы устройства численно равно коду вычитаемого.

Цель изобретения — повышение быстродействия устройства для вычитания. . Указанная цель достигается тем, что устройство для вычитания, содержащее генератор импульсов, первый и второй счетчики, триггер и первый элемент И, второй вход которого соединен с выходом генератора импульсов, а выход подключен к первым входам первого и второго счетчиков, прямой выход триггера подключен к знаковому выходу устрой ства, нулевой вход триггера и уста30

65 новочные входы первого и второго счетчиков подключены к управляющему входу устройства, включает также компаратор, второй и третий элементы И и третий счетчик, причем входы компаратора соединены с выходами разрядов первого и второго счетчиков, а выход — с единичным входом триггера, первый вход второго элемента И соединен с выходом младшего разряда первого счетчика, второй вход связан с инверсным выходом триггера, а выход — с вторым входом второго счетчика, первый вход третьего элемента И соединен с выходом младшего разряда второго счетчика, второй вход связан с прямЫм выходом триггера, а выход — с вторым входом первого счетчика, выходы младшего разряда первого и второго счетчиков соединены с входами старшего разряда первого и второго счетчиков соответственно, вход третьего счетчика связан с выходом генератора импульсов, установочный вход — с установочным входом устройства, а выход — с вторым входом первого элемента И.

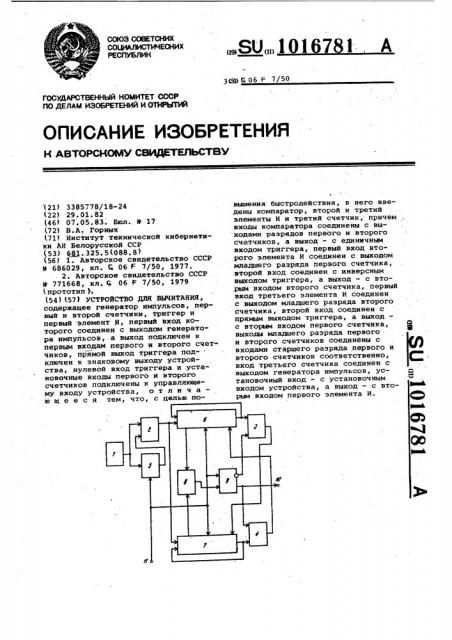

На чертеже представлена функциональная схема устройства.

Устройство для вычитания содержит генератор 1 импульсов, три двухвходовых элемента И 2-4, счетчики 5-7, компаратор 8, триггер 9, знаковый выход 10, установочный вход 11.

Устройство работает следующим образом.

Сигналом с установочного входа

11 вычитаемое заносится в счетчик б, уменьшаемое заносится в счетчик

7, счетчик 5 устанавливается в нулевое состояние. По этому же сигналу триггер 9 устанавливается в состояние, определяемое выходным сигналом компаратора 8. Схема начинает работать после снятия сигнала с установочного входа 11, причем состояние триггера 9 остается неизменным до конца вычитания.

Для случая, когда уменьшаемое больше вычитаемого, триггер 9 находится в нулевом состоянии. Нулевой знак разности фиксируется на знаковом выходе 10. С инверсного выхода триггера 9 поступает разрешающий сигнал на элемент И 3. На другой вход элемента И 3 поступает сигнал с выхода младшего разряда вычитаемого, находящегося в счетчике б. Если этот разряд находится в единичном состоянии, то из содержимого счетчика 7, т.е. Уменьшаемого, вычитается единица. Если младший разряд вычитаемого находится в нулевом состоянии, то содержимое счетчика 7 остается неизменным. После этого содержимое счет3

1016781

Составитель A. Степанов

Редактор Н.Безродная Техред Л.Пекарь, Корректор Е. Рошко

Заказ 3387/48 Тираж 706

ВНИИПИ Государственного комитета СССР

rio делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Филиал ППП "Патент", r. Ужгород, ул.,Проектная, 4 чиков б н 7 сдвигается на один раз« ряд вправо и выдвинутые младшие разряды помещаются на место старших разрядов этих же счетчиков. На этом заканчивается один такт работы устройства. Остальные такты выполняются аналогично вышеизложенному.

Процесс вычитания оканчивается, когда устройство совершит полный цикл., состоящий из количества так-. тов, равных числу разрядов счетчика б или 7, т.е. выдвинутый младший разряд вычитаемого вернется на свое исходное место. Конец цикла определяется счетчиком 5, который после отсчета необходимого количества импульсов снимает разрешающий потенциал с второго входа элемента

И 2. Результат вычитания в прямом коде будет находиться при этом в счетчике 7.

Для случая, когда уменьшаемое меньше вычитаемого, по сигналу компаратора 8 триггер 9 устанавливается в единичное состояние, указывая на знаковом выходе 10 знак разницы. Это состояние триггера 9 обеспечивает разрешающий потенциал на первом входе элемента И 4, вследствие чего иэ содержимого счетчика 6 будет вычитаться единица, если младший разряд счетчика 7 будет также равен единице. Элемент

И 3 при этом будет заблокирован низким уровнем с инверсного выхода триггера 9, в результате чего содержимое счетчика 7, т.е. уменьшаемое, будет только сдвигаться вправо

5 на один разряд в каждом такте. tIo концу цикла, также определяемому счетчиком 5, результат вычитания в прямом коде будет находиться в счетчике 6. В обоих случаях местово3Q ложение разности определяется по значению знакового выхода 10.

В связи с тем, что благодаря компаратору 8 в устройстве обеспечивается вычитание меньшего числа из большего или вычитание друг из друга двух одинаковых чисвл, вычитание единиц из счетчика 6 или 7 не оказывает влияния на значение мпадкях разрядов, находящихся в результате сдвига иа месте старших разрядов.

Таким образоМ, в предлагаемом устройстве обеспечивается повышение быстродействия эа счет того, что цикл вычисления определяется количеством разрядов обрабатываемых чисел, а не кодом вычитаемого, как в прототипе. Выигрьна по быстродействию по сравнению с прототипом

39 достигается в 2Л/2п раэ, где празрядность обрабатываемых чисел.