Устройство для программного управления

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ, содержащее блок управления, блок оперативной памяти , регистр адреса кс «анды, регистр адреса данных и регистр адреса памяти , причем выход регистра адреса па .М;яти-Соединенс адресным входом блока оперативной памяти, выход которого через числовую магистраль соединен с информационными входами реглйтра адреса данных и блока управления, информационные выходы блока управления через числовую магистраль соедиг йены с информационными входами ре-, гистра адреса команды, выходу регистров адреса команды и адреса данных соединены соответственно с первьши и вторыми информационными входами регистра адреса памяти, с первого по пятый выходы блока управления соединены с управляющими входами регистра адреса команды, регистра адреса данных , блока оперативной памяти и первым и вторым управляквдими входами регистра адреса памяти, отличающееся тем, что, с целью упрощения и повьнирния быстродействия устройства , введены операционный блок и шифратор, выход которого соединен с третьим информационным входом регистра адреса памяти, вход шифрато ра и третий управляющий вход регистра адреса памяти соединены с шестым выходом блока управления,информационный вход операционного блока через числовую магистраль соединен с выходами блока оперативной памяти, выход операционного блока: через числовую магистраль соединен с входом блока оперативной памяти и заходом блока управления , управляющий вход операционного блока соединен с седьмым выходсм блока управления. 2. Устройство по п.1, отличающееся тем, что операционный блок содержит п кана1лов, четыре элемента И, одвигатель и элемент НЕ, причем каждый канал состоит из регистра , четырех элементов И и элемента ИЛИ, первые входы первого и . j второго элементов И и элемента ИЛИ каждого канала соединены с соответ (Л ствувхцими выходами регистра, первый .и вторсй информационные входы которого соединены с выходами первого элемента И и эле /юнта ИЛИ своего канала, второй вход второго элементами каждо-5 го канала соединен с управляющим вхо.дом блока, а выход второго элемента И каждого канала соединен с управляющим входом блока, выход второго элемента и каждого канала - с выхоСП ) дом блока, втсфые входы первого эл леита И и элемента ИЛИ каждого 00 оо канала сое;1этнены соответственно с выходами третьего и четвертого элементов И своего канала, первые входы которых соединены с информационным входом блока, вторые входы третьего и четвертого элементов И и вход установки в нуль регистра каждого канала соединены с управляющим входом блока, вход и выход сдвигателя соединены соответственно с выходом . пёрвЪго и первым входом второго элемента И, вход и выход элемента НВ соединены соответственно с выходами третьего и первым четвертого элементов И, первые входы первого и третьего эл 4енто$ И соединены с

СОЮЗ СОЕЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

3(5g С, 06F 9 22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

М АВТОРСМОМУ С8ИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (21) 3365164/18-24 (22) 17 ° 12.81 (46) 07 ° 05.83. Бюл. Р 17 (72) В.И.Аблязов, В.Г.Колосов, Н.И.Колосова, В.С.Королев,И.Л.Туккель и И.Ф.Фельдман (53) 681.325 (088.8) (56) 1. Авторское свидетельство СССР

Р 444184, кл. C Об F 9/46, 1974.

2. Патент CLIA M 4040031, кл. G Об F 9/00, опублик. 1977 (прототип). (54)(57) 1. УСТРОЙСТВО ДЛЯ ПРОГРАИМНОГО УПРАВЛЕНИЯ, содержащее блок управления, блок оперативной памяти, регистр адреса команды, регистр адреса данных и регистр адреса памяти, причем выход регистра адреса памяти .соединен с адресным входом блока оперативной памяти, -выход которого через числовую магистраль соединен с информационными входами регистра адреса данных и блока управления, информационные выходы блока управления через числовую магистраль соеди.нены с информационными входами ре-. гистра адреса команды, выходы регистров адреса команды и адреса данных соединены соответственно с первьещ и вторыми информационными входами регистра адреса памяти, с первого по пятый выходы блока управления соединены с управляющими входами регистра адреса команды, регистра адреса дан.ных., блока оперативной памяти и первым и вторым управляющими входами регистра адреса памяти, о т л и ч аю щ е е с я тем, что, с целью упрощения и повыаения быстродействия устройства, введены операционный блок и шифратор, выход которого соединен с третьим информационным входом регистра адреса памяти, вход шифрато . ра и третий управляющий вход регистра адреса памяти соединены с шестым выходом блока управления, информационный ,.SU„„1016783 A вход операционного блока через числовую магистраль соединен с выходами блока оперативной памяти, выход операционного. блока через чйсловую магистраль соединен с входом блока оперативной памяти и выходом блока управления, управляющий вход операционного блока соединен с седьмым выходом блока управления.

2. Устройство по.п.l о т л и ч аю щ е е.с я тем, что ойерацнонный блок содержит ь каналов, четыре элемента И, адвигатель и элемент НЕ, причем каждый канал состоит из регистра, четырех элементов И и элемента HJIH, первые входы первого и . второго элементов И и элемента ИЛИ Е каждого каналавсоединены с соответствующими выходами регистра, первый и второй информационные входы которого соединены с выходами первого элемента И и элемента .ИЛИ caoего канала, второй вход второго элемента И каждо-го канала соединен с управляющим вхо; дом блока, а выход второго элемента

И каждого канала соединен с управляющим входом блока, выход второго элемента И каждого канала — с выхо,яом блока, вторые входы первого элемента И и элемента ИЛИ каждого канала соединены соответственно с выходами третьего и четвертого элементов И своего канала, первые входы которых соединены с информационным входом блока, вторые входы третьего и четвертого элементов И и вход установки в нуль регистра каждого канала соединены с управлякв им входом блока, вход и выход сдвигателя соединены соответственно с выходом первого и первым входом второго элемента И, вход и выход элемента НЕ соединены coo âåòñòâåíío с выходами третьего и первым t:õoäoì четвертого элементов И, первые входы первого и третьего элементов И соединены с

1016783 управляющим входом блока, а их вторые входы соединены с информационным входом блока, с информационным выходом которого соединены выходы втоИзобретение относится к вычислительной технике и может использоваться в цифровых вычислительных и управляющих машинах, работающих по программе, хранящейся в оперативной 5 памяти.

Известно устройство содержащее арифметическо-логический блок, буферный регистр, блок хранения данных, блок управления, блок ввода 10 и вывода и блок микропрограммного управления, происходит обработка данных, содержащихся в .блоке хранения данных, буферном регистре или же поступающих с блока ввода и вывода.

Для хранения промежуточных результатов обработки используются буферный. регистр и блок хранения данных. Выбор промежуточных результатов осуществляется отдельной командой, формируемой блоком микропрограммного 20 управления (13 .

Наиболее близким по технической сущности к изобретению является устройство, содержащее блок управления, блок оперативной памяти, ре- 25 гистр адреса команды, регистр адреса данных и регистр адреса памяти (23.

В данном устройстве результат записывается в память по адресу одного из операндов. При необходимости сох- 30 ранения операнда он пересылается в рабочую ячейку по специальной команде, что удлиняет программу.

Цель изобретения — упрощение устройства и повышение быстродействия. З5

Указанная цель достигается за счет того, что в устройство для программного управления, содержащее блок управления, блок оперативной памяти, регистр адреса команды, регистр адреса данных и регистр адреса памяти, причем выход регистра адреса памяти соединен с адресным входом блока оперативной памяти, выход которого через числовую магистраль соединен с информационными входами. регистра адреса данных и блока управления, информационные выходы блока управления через числовую магистраль соединены cинформационными вхо- . дами регистра адреса команды, выходы регистров адреса команды и адреса дан-. ных соединены соответственно с первы-, ми и вторыми информационными входами регистра адреса памяти,с первого по пярого и четвертого элементов И, с управляющим входом блока соединены вторые входы второго и четвертого элементов И.

2 тый выходы блока управления соединены с управляющими входами регистра адреса команды, регистра адреса данных, блока оперативной памяти и первым и вторым управляющими входами регистра адреса памяти, введены операционный блок и шифратор, выход которого соединен с третьим информационным входом регистра адреса памяти, вход шифратора и третий управляющий вход регистра адреса памяти соединены с шестым выходом блока управления, информационный вход операционного блока через числовую магистраль соединен с выходами блока оперативной памяти, выход операционного блока через числовую магистраль соединен с входом блока оперативной памяти и выходом блока управления, управляющий вход операционного блока соединен с седьмым выходом блока управления.

Кроме того, операционный блок содержит и каналов, четыре элемента

И, сдвигатель и элемент НЕ, причем каждый канал состоит из регистра, четырех элементов И и элемента ИЛИ, первые входы первого и второго элементов И и элемента ИЛИ каждого канала соединены с соответствующими выходами регистра, первый и второй информационные входы которого соединены с выходами первого элемента И и элемента ИЛИ своего канала, второй вход. второго элемента И каждого канала соединен с управляющим входом блока, а выход второго элемента И каждого канала соединен с управляющим входом блока, выход второго элемента И каждого канала — с выходом блока, вторые входы первого элемента И и элемента ИЛИ каждого канала соединены соответственно с выходами третьего и четвертого элементов И своего канала, первые входы которых соединены с информационным входом блока, вторые входы третьего и четвертого элементов И и вход установки в нуль регистра каждого канала соединены с управляющим входом блока, вход и выход сдвигателя соединены соответственно с выходом первого и первым входом второго элементов И, вход и выход элемента НЕ соединены соответственно с выходами третьего и первым входом четвертого элементов И, первые входы первого и тре1016783 тьего элементов И соединены с управляющим входом блока, а нх вторые входы соединены с информационным входом блока, с информационным выходом которого соединены также выходы, второго и четвертого элементов И, с управляющим входом блока соединены вторые входы второго и четвертого элементов И.

Таким образом, появляется возможность записи результата, вырабатываемого операционным блоком в фик сированную ячейку оперативной памяти без указания в выполняемой команде адреса фиксированной ячейки.

Обращение к ней осуществляется обычным способом через регистр адреса. памяти, т.е. результат, записанный в фиксированную ячейку, может в дальнейшем использоваться любой командой основного формата.

В данном устройстве сокращаются объем и время выполнения программ, поскольку результат выполнения команды записывается в оперативную память, а операнды сохраняются без предварительного размножения.

В данном устройстве сокращается объем и время выполнения программ за счет исключения команд передачи результата из регистра в память и обратно.

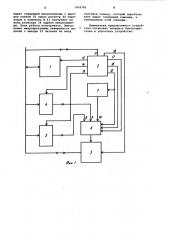

На фиг.l представлена структурная схема устройства1 на Фиг.2 — струк-. турная схема операционного блока; на фиг.3 †возможное выполнение структурной схемы блока управления, построенного по принципу автомата с программируемой логикой работы.

Устройство (фиг.l) содержит операционный.блок 1, блок 2 управления, блок 3 оперативной памяти, регистр

4 адреса команды, регистр 5 адреса данных, регистр б адреса памяти, шифратор 7, информационные входы 8-10 регистра б, вход — выход ll блока 2, выходы 12-18 блока 2.

Операционный блок (фиг.2) содержит каналы 19, сдвигатель 20 и элемент НЕ 21, элементы И 22-25, причем каналы 19 состоят из регистра

26, элемента ИЛИ 27, элементов И 2831.

Блок 2 содержит выходы 32-33 шифратора микрооперации, регистр 34 адреса микрокоманды, дешифратор 35 адреса микрокаманды, память 36, дешифратор 37 кода микрокоманды, шиф-. ратор 38 микрооперации, тактовое -. устройство 39, регистр 40 переходов, элементы И 41, счетчик 42 команд.

Устройство работает следующим образом.

По сигналу с выхода 13 блока 2 управления адрес очередной команды, поступающий с выхода регистра 4 ад-, реса команды на вход ll регистра б адреса памяти, записывается в этот регистр. Команда считывается из бло= ка 3 оперативной памяти, адреса операндов записываются в регистр 5 адреса данных, а код операций поступает в блок 2 управления. Блок 2 управления вырабатывает сигналы, обеспечивающие поступление операндов из блока 3 оперативной памяти в операционный блок 1, где в соответствии с заданным кодом операции форми10 руется результат. Код операции определяет также куда должен быть поМе- щен результат..Если нет указания., на использование фиксированного адреса, то результат записываетсн в

15 блок 3 оперативной памяти по адресу одного из операндов, находящемуся в регистре б адреса памяти. Если результат должен быть помещен в фикси-. рованную ячейку памяти, то блок 2 управления со своего выхода 12 выдает сигнал на вход шифратора 7 и третий управляющий вход регистра 6 адреса памяти. Шифратор 7 вырабатывает адрес фиксированной ячейки огеративной памяти, который поступает на третий информационный вход 10 регистра б адреса памяти и записывается в этот регистр. Далее под действием сигналов с выходов 13 и 16 блока 2 управления операционный блок

1 выдает, а блок 3 оперативной.памяти записывает результат выполнения команды в фиксированную ячейку, адрес которой находится в регистре б адреса памяти. Блок 2 управления через числовую магистраль передает адрес следующей команды в регистр 4 адреса команды. На этом заканчивается цикл работы устройства.

Операционный блок в зависимости

40 от управляющих сигналов, приходящих на выход 13, выполняет логические и арифметические операции над сатерандами,,поступающими в блок с числовой магистрали. Элементы ИЛИ 27 обеспе45 чивают запись в регистр 26 или дизьюнкцию операндов и промежуточных результатов, элемента И- 30 — конъюнкцию, И 28 — выдачу, НЕ .21 — инверсию, а сдвигатель 20: — сдвиг. Результат операции из регистра 26 через числовую магистраль поступает на входы блока 3. Операционный блок l вырабатывает результат в соответствии с заданным кодом операции.

Работа блока управления происходит следующим образом.:

Код операции с числовой магистрали поступает на регистр 34 адреса микрокоманды в качестве адреса первой микрокоманды.Этот адрес дешифрируется

60 дешифратором 35 и их памяти Зб считывается микрокоманда. Код микрокоманды .дешифрируется дешифратором 37 када микрокоманды,шифратор.38 микроопераций вырабатывает набор управляющих

65 сигналов, поступающих на выходы блока. ОМ В3

Адрес следующей микрокоманды с выходов памяти 36 через регистр 40 переходов и элементы И 41 поступает на вход регистра 34 адреса микрокоманды. Цикл работы повторяется. Выполнение микропрограммы завершается выдачей с выхода 33 сигнала на вход счетчика команд, который вырабатывает адрес следующей команды, и считыванием этой команды.

Применение предлагаемого устройства позволяет повысить быстродействие и упростить устройство.

1016783

1016783

Составитель Г. Пономарева

Редактор Ю.Середа ТехредЖ.Кастелевич Корректор Е.Рошко

Заказ 3387/48. Тираж 706 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открнтий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП Патент, г„ужгород, ул.Проектная,4