Устройство дискретного фазирования

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДИСКРЕТНОГО ФАЗИРОВАНИЯ , содержащее задающий генератор , выход которого подключен к вхо дам дешифратора через делитель частоты , а также реверсивный счетчик и элементы И, отличающееся тем, что, с целью повышения точности фазирования при воздействии случай- . ных помех, искажающих фронты сигналов , в него введены элемент 2-И-ИЛИ и триггеры, при этом выхода| задгиоще го генератора и дешифратора через элемент 2-И-ИЛИ подключены к первым входам первого и второго элементов И, выходы котсфых подключены соответственно к вычитающему и суммирующбму входам реверсивного счетчика, выходы разрядов которого подключены к установочным входам делителя частоты, прямой и инверсный выходы старшего разряда которого подключены соответственно к установочным входгич первого и второго триггеров, инверсные выходы которых подключены к второму и третьему входам первого элемента И, прямой выход второго триггера подключен к второму входу второго элемента И, а инверсный выход первого j триггера через элемент И подсл ключен к входу сброс реверсивного счетчика, который объединен с выходом дешифратора и с соответствующими входами первого и второго триггеров, стробйрующие входы которых и S ход третьего элемента И объединены мёлоду собой и подключены к формирователя фронта сигнала. Р5 00 4 Ч

СОКИ СОВЕТСКИХ

СОМ}4АЛИСТИЧЕСКИХ

РЕСПУБЛИК

3ДР Н 04 4 7 00

j

Р 1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

AO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ "(21) 2913172/18-09 (22) 17.04.80 (4P) 07.05.83. Бюл. Р 17 (72) Л. М. Скоморовский (71) Государственное союзное конст-. рукторско-технологическое бюро по проектированию счетных машин и Опытный завод (53) 621.394.бб2 (088.8) (56) 1. Авторское свидетельство СССР

9 403096, кл. 804 4 7/00, 1974.

2. Авторское свидетельство СССР

М 319095, кл. Н 04 4 7/00, 1972 (приохотил.)., (54) (57) УСТРОЙСТВО ДИСКРЕТНОГО ФАЗИРОВАНИЯ, содержащее задающий генераторрвыход которого подключен к вхо. дам .дешифратора через делитель частоты, а также реверсивный счетчик и элементы И, о т л и ч а ю щ е е с я тем, что, с целью повышения точности фазирования при воздействии случайных помех, искажающих фронты сигналов, в него введены элемент 2-И-ИЛИ и триггеры, при этом выходы задающеSUÄÄ1()16 4 А! го генератора и дешифратора через элемент 2-И-ИЛИ подключены к первым входам первого и второго элементов И, выходы которых подключены соответственно к вычитающему и суммирующему входам реверсивного счетчика, выходы разрядов которого подключены к установочным входам делителя частоты, прямой и инверсный выходы старшего разряда которого подключены соответственно к установочным входам перво- го и второго триггеров, инверсные выходы которых подключены к второму и третьему входам первого элемента И, прямой выход второго триггера подключен к второму входу второго элемента И, а инверсный выход первого pg триггера через третий элемент И подключен к входу "сброс"- реверсивного счетчика, который объединен с выходом дешифратора и с соответствующими входами первого и второго триггеров, стробирующие входы которых и.другой вход третьего элемента И объединены между собой и подключены к выходу формирователя фронта сигнала.

1016847

Изобретение относится к переда,че данных и может быть использовано; ,в аппаратуре синхронной передачи дан ных, в частности, при многоточечном подключении устройств передачи данных к-линии связи, например, в системе коллективного пользования ЭВМ.

Известно устройство дискретного фазирования с переменным коррекционным эффектом, содержащее генератор, делитель частоты, к которому подклю- 30 чен формирователь коррекционного эффекта через логические блоки. В данном устройстве переменный коррекционный эффект достигается за счет использования узлов добавления и j5 Исключения импульсов в тактовой цепи генератора на входе делителя, дейст.вующих в соответствии с сигналами, подаваемыми от формирователя коррекционного эффекта (1 ).

Недостатком устройства является сложная техническая реализация узлов добавления и исключения импульсов.

Наиболее близким по технической сущности к предлагаемому является устройство дискретного фазирований, содержащее генератор с rn-разрядным управляемым делителем, к Ъыходам которого подключен дешифратор конечного состояния, а к входамт-. цепей с выходов рреобразователя кода. Выход дешифратора подключен к входу, стробирующему выходные цепи преобразователя кода. Ло стробирующему сигналу дешифратор в момент корректирования фазы сигнала с выходов преобразова- 35 теля кода устанавливает делитель в нужное положение: сдвиг вперед или назад относительно фронтов принимаемой

;последовательности до совпадения Фрон. тов. К входам преобразователя ко а подключено и цепей (n >en) характеризуI ющих величину и знак рассогласования фазы колебаний местного генератора и принимаемых. сигналов. Цепи подаются . от формирователя коррекционного эффек- «5

- та, на вход которого подключен выход, .узла выделения фронтов (2(.

Недостаток устройства состоит в том, что оно не обеспечивает защиты от случайного расфазирования иэ-за воздействия случайных помех, искажа ющих. Фронты сигналов, что снижает точность фазирования.

Цель изобретения - повышение точности фаэирования при воздействии слу чайных помех, искажающих фронты сигналов.

Для достижения поставленной цели в устройство дискретного фазирования, содержащее задающий. генератор, выход которого подключен к входам дешифра- 60 тора через делитель частоты, а также реверсивный счетчик и элементы И, введены элемент 2-И-ИЛИ и триггеры, ! при этом вИходы задающего генератора и дешифратора через элемент 2-И-ИМЛИ 65 подключены к первым входам первого и второго элементов И, выходы которых подключены соответственно к вычитаЫщему и суммирующему входам реверсивного счетчика, выходы разрядов кото-.. рого подключены к установочным входам делителя частоты, прямой и инверсный выходы старшего разряда которого подключены соответственно к установочным входам первого и второго триггеров, инверсные выходы которых подключены к второму и третьему входам первого элемента И, прямой выход второго триггера подключен ко второму входу второго элемента И, а инверсный выход первого триггера через. третий элемент И подключен к входу "сброс" реверсивногс счетчика, который объединен с выходом дешифратора и с соответствующими входами первого и втор4го триггеров, бтробирующие входы ко торых и другой вход третьего элемента И объединены между собой и подключены к вйходу формирователя фронта сигнала..

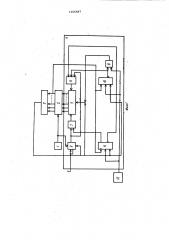

На фиг. 1 представлена структурная . электрическая схема устройства диск" ретного фазирования на фиг. 2 временные диаграммы, поясняющие работу устройства.

Устройство содержит задающий генератор 1, делитель 2 частоты дешифратор 3 и формирователь 4 корректирующей комбинации, состоящий из реверсивного счетчика 5, элементов И 6, 7 и 8, элемента 2-И-ИЛИ 9, триггеров 10 и 11 и формирователь 12 фронта сигнала.

Такты задающего генератора 1 (фиг. 2 a) поступают на делитель частоты 2 и одновременно через элемент

2-И-ИЛИ 9 на входы элементов И 6 и 7.

В исходном состоянии инверсный сиг.нал с выхода триггера 10 разрешает прохождение тактов через, элемент И 6 на вычитающий вход реверсивного счетчика 5, В момент времени, соответствуу ий завершению периода работы делителя частоты, срабатывает дешифратор 3, сигнал с выхода которого (фиг. 2 в, е, и, м) разрешает установку делителя 2 частоты по щ входам в положе-! ние, соответствующее сигналам, подаваемым с реверсивного счетчика-5.

После этого сигнал с выхода дешифратора 3 устанавливает в исходноесостояние триггеры 10 и 11 и реверсивный счетчик 5. После полной синфазности делитель 2 частоты и реверсивный счетчик 5 продвигаются синфазно и в моменты переписи состояние делите.ля 2 частоты не изменяются.

Рассмотрим режимы корректирования опережения и отставания.

На фиг. 2 б, г и ж за опережение задающего генератора принято попадание фронта принимаемого сигнала в первую половину периода работы

1016847

3 делителя 2 частоты (сигнал на выхо- единичное состояние устанавль вается де старшего разряда делителя равен триггер 10, а на реверсивном -, .тчинулю),а за отставание - попадание ке 5 фиксируется определенна.. велиэтого фронта во вторую половину пв- чина опережения. Во второй половине риода работы, делителя: 2 частоты периода устанавливается в единичное (сигнал на выходе старшего разряда 5 положение триггер 11, элемент И 8 в делителя равен единице). В случае этом случае не срабатывает и элемент опережения реверсивный счетчик 5 так- H 7 начинает отсчитывать отставание. же продвигается в обратном направ- Если преобладания симметричны, таклении тактами с элемента И б, но ты с элемента И 7 к моменту опроса лишь до момента выявления фронта сиг- 10 компенсируют такты с элеМента И б и

:нала. фронт сигнала, поступающий с . состояние делителя 2 частоты не корформирователя 12 фронта сигнала, ректируется. В случае несимметричных стробирует единичный. сигнал (инвер- преобладаний корректировка произвосия нулевого сигнала с выхода стар- дится в соответствии с предыдущим шего разряда делителя 2 частоты) на 15 описанием в зависимости от того, опевходе триггера 10, который устанав- режение или отставание фиксирует реливается в единичное. состояние, версивный счетчик, как результат слоблокируя элемент И -6 (фиг. 2д). Ре" жения двух тактовых последовательноверсивный счетчик 5 фиксирует сос- стей с элементов И б и 7 (фиг. 2 л) ° тояние, соответствующее опережению, о После вхождения в синфазность которое выражается двоичным числом устройство переходит в режим подстройР большим чем полпериода делителя ки синфазности, когда уже не требует:"Р> 2 2=2 . В момент срабатывания ся подстраивать делитель частоты под

1 деиифратора 3 это состояние заносит- . каждый фронт поступающего сигнала. .ся .в делитель 2 частоты, после чего 25 При этом на элемент 2-И-ИЛИ 9 поступа триггеры 10 и 11 и реверсивный счет- ет сигнал управления, блокирующий прочик сбрасываются. Теперь такты гене- хождение тактов от задающего генераратора 1 должны сначала довести де- тора 1 и разрешающий подачу сигнала с литель 2 частоты до состояния 2, что выхода дешифратора 3. В этом случае компенсирует опережение, а затем от- весь механизм корректирования фазы считать новый период работы. сохраняется, но при расфазировании в

B случае отставания фронт сигнала, каждом периоде реверсивный счетчик 5 попадающий во вторую половину пери- сдвигается в прямом или обратном на ода, совпадает с единичным сигналом равлении лишь на один шаг, что соот на входе триггера 11, устанавливая ветствует режиму постройки устройства.

его в единичное состояние, элемент

И б при этом блокируется и разблоки- Предлагаемое устройство может руется элемент И 7. Сигнал с элемен- использоваться в сетях синхронной та И 8 сбрасывает реверсивный счет- передачи данных, в особенности там, :чик 5, который до выявления фронта где не требуется высокая скорость сигнала продвигался в обратном нап- 40 вхождения в сивхронизм, например:на равлении. Элемент И 7. начинает выда- многоточечных сетях передачи данных

;вать такты в прямом направлении на где из-за большого числа абонентов .счетный вход реверсивного счетчика 5 требуется минимально сократить (фиг. 2 з). В момент сброса от дешиф- вспомогательные операции. ратора 3 в делитель 2 частоты будет, 4g Испытания показали, что в УСловизаписано число Р, меньшее чем полпе- ях отсутствия помех или при единичриода рабаты делителя частоты ных помехах устройство обеспечивает что сокращает следующий, вхождение в синфазиость уже со второнта принимаемого соответствующую величину, компенсИ- сигнала, а по отставшимся фронтам руя таким образом отставание. -. обеспечивается проверка правильности

В случае приема посылок с искаже- фазирования. йиями типа преобладаний (фиг. 2 к) Использование изобретения позвовыделяются оба фронта, как в первой,- лит сократить объем устройства и так и во второй половинах периода. повысить надежность его функциониПри. этом в первой половине периода в. рования.

1016847

1016847

4 Составитель В. Евдокимова

Редактор О. Сопко Техред В.Далекорей

Корректор А. Ференц

Заказ 3399/51 Тираж 677

BHHHGH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская. наб., д. 4/5

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4