Выходной узел тестера для контроля логических схем

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

\ °

РЕСПУБЛИК

g G01Н 1 28

ОПИСАНИЕ ИЗОБРЕТЕН

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3389507/18-21 (22) 28.01.82 (46) 15.05.83 Бюл. В 18 (72) E.Ô. Иокаин, С. И. Еремин, О.А. Нилова и Б.А. Ящук

53) 681.322 (088.8)

<56) 1. Патент CIA и 3792292, кл. 307-29, 1971.

2. Авторское свидетельство СССР и 651274, кл.. 6 01 и 31/28, 1977 (прототип ) . (54)(57) ВЫХОДНОЙ УЗЕЛ ТЕСТЕРА ДЛЯ

КОНТРОЛЯ ЛОГИЧЕСКИХ СХЕИ, содержащий первый и второй ключи, первый и второй вентили и D-триггер, C-вход которого соединен с первым входом вы модного узла, соединенного вторым входом с первыми входами первого и второго вентилей, третьим входом— с вторыми входами первого и второго вентилей и 8-входом триггера, сое,SUÄÄ;1 018064 А динного выходом с третьими входами первого и второго вентилей, соединен-, ных выходами соответственно с первыми входами первого и второго ключей, выходы которых соединены с выходом выходного узла, о т л и ч а ю щ и йс я тем, что, с целью повышения надежности выходного узла,в него введены первый и второй резисторы, первый и второй компараторы, первый и второй источники опорного напряжения и элемент ИЛИ, соединенный выходом с

g-входом триггера, первым и вторым входами " соответственно с выходами первого и второго компараторов, соединенных первыми входами соответственно с выходами первого и второго источников опорного напряжения, вто" рыми .входами через первый и второй резисторы-соответственно с четвертым и пятым входами выходного узла, а .непосредственно - с вторыми входами первого и второго ключей.

1018064

Изобретение относится к контрольно-измерительной технике и может быть использовано в аппаратуре контроля логических схем.

Известно устройство для контроля логических схем, содержащее входной .вентиль, вентиль запрета, буферный каскад, ключ уровня логической единицы, ключ уровня логического нуля 11

Недостатком данного. устройства является отсутствие защиты ключей от перегрузки, а также отсутствие защиты выходов проверяемой схемы от перегрузки.

Наиболее близким по технической сущности к предлагаемому изобретению является выходной узел тестера для контроля логических схем, содержащий первый и второй ключи, первый и вто-; рой вентили, триггер и элемент сравнения 2 ) .

Недостатком известного устройства является отсутствие защиты выходов проверяемой схемы и выходного узла от токов, превышающих допустимые зна. чения, что может привести к выходу иэ строя выходного узла или к снижению его надежности. Протекание недоI пустимых токов через. вь1ходы выходно-1 го узла в процессе контроля может произойти в тех случаях, если к тестеру ошибочно подключена не та логическая схема, на контроль которой настроен тестер, если в проверяемой схеме в процессе ее изготовления ошибочно выходы микросхем подсоединены к входным контактам узла, если в случае неправильной работы тестера, в результате чего тестер задает входные сигналы на выходы проверяемой логической схемы. Во всех этих случаях выходы формирователей тестера и выходы микросхем проверяемого узла оказываются соединенными между собою, что приводит при разных логических состояниях на них к протеканию недопустимо больших токов.

Цель изобретения - повышение надежности.

Поставленная цель достигается тем, что s выходной узел тестера для контроля логических схем, содержащий первый и второй ключи, первый и втор и вентили и 3-триггер, С -вход которого соединен с первым входом выходного узла, соединенного вторым входом с первыми входами первого и второго вентилей, третьим входом с вторыми входами первого vi второго вентилей и 5 -входом триггера, соединенного выходом с третьими входами первого и второго вентилей, соединенных выходами соответственно с пер5 выми входами первого и второго ключей, выходы которых соединены с выходом выходного узла, введены первый и второй резисторы, первый и второй компараторы, первый и второй !

О источники опорного напряжения и weмент ИЛИ, соединенный выходом с -входом триггера, первым и вторым входами соответственно с выходами первого и второго компараторов, соединенных первыми входами соответственно с выходами первого и второго источников опорного напряжения, вторыми входами через первый и второй резисторы соответственно с четвертым и пятым

20 входами выходного узла, а непосредственно - c вторыми входами первого и второго ключей.

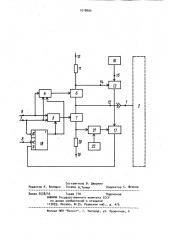

На чертеже представлена функциональная схема выходного узла тесте25 ра.

Выходной узел содержит контакт 1 проверяемой схемы, проверяемую логическую схему 2, второй вход 3, первый вентиль 4,.который выполнен, 30 например, на логическом элементе

И НЕ, второй вентиль 5, выполненЦ нйи, например, на логическом элементе запрета, первый ключ 6 второй ключ 7, первый вход 8, третий вход

9, четвертый вход 10, первый резистор

11, выход 12, первый компаратор 13 с входами 14 и 15, первый источник

16 опорного напряжения, элемент ИЛИ

17, Э-триггер !8, пятый вход 19, 40 второй реэистор 20, второй компаратор 21, второй источник 22 опорного напряжения.

Выходной узел тестера работает следующим образом.

45 В том случае, если контакт 1 проверяемой схемы 2 является ее выходом, на вход 3 подается уровень логичес.кого нуля и на выходах вентилей 4 и

5 устанавливаются нулевые логические уровни, которые обеспечивают непроводящее состояние ключей 6 и 7. В этом состоянии устройство имеет высокое выходное сопротивление. Если контакт

1 является входом проверяемой схемы

2, на вход 3 подается уровень логической единицы, а на вход 8 - синхроимпульс. При подаче на вхоа 9 уровня логической. единицы на выходе вентиля

4 устанавливается уровень логической

64 4 на выходе триггера 18, что приводит к переходу ключа 6 в непроеодящее состояние. Аналогично при подаче на вход 9 уровня логического нуля уровень логической единицы появляется на выходе вентиля 5. Ключ .7 переходит в проводящее -состояние, и напряжение логического нуля с входа 19 через резистор 20 попадает на выход

12 и далее иа вход 1 схемы 2. Если в этом случае ток через ключ 7 превышает допустимое значение, то напряженце на резисторе 20 вызывает

- срабатывание компаратора 21, на другой вход которого подается напряжение от источника 22 опорного напряжения. Появляющийся при этом на выходе компаратора 21 уровень логического нуля попадает через элемент ИЛИ 17 на вход З триггера 18. Появляющийся при этом уровень логического нуля на выходе триггера 18 вызывает з пирание ключа 7. Иэ-за высокой чувствительности компаратора 21 величина сопротивления резистора 20 составляет едини цы Ом и практически не влияет на величину напряжения логическрго нуля, формируемого выходным узлом.

Предлагаемое устройство эа счет. введения эЛементов 11, 13, 16, 17, 21 и 22 обеспечивает надежную защиту от недопустииюх токов не только выходного узла тестера, но и выходов микросхем проверяемого логического узла. Это позволяет уменьшить расходы на ремонт выходного узла, повысить его надежность и срок службы.

3 10180 единицы, а на выходе вентиля 5 - -уровень логического нуля, ключ 7 устанав-» ливается в непроводящее состояние, а ключ 6 -. в проводящее, и напряжение уровня логической единицы с входа

10 через резистор 11 поступает на выход 12 и на вход 1 проверяемой схемы 2. Если при этом схема 2 неисправна или по какой-либо другой причине ток через клоч 6 превышает до- IO пустимое значение, то появляющееся при этом напряжение на резисторе 11 вызывает срабатывание компаратора

13. Это.напряжение подается на вход

14 компаратора 13; на другой вход

15 которого подается напряжение с регулируемого источника 16 опорного напряжения. Изменяя напряжение источника 16 опорного напряжения, можно устанавливать срабатывание компарато- 20 ра при заданном токе через ключ 6.

Учитывая высокую чувствительность современных компараторов (например, микросхем 521СА1), составляющих единицы милливольт, величина сопротив .ленияреэистора II составляет единицы

Ом и практически не влияет на величину напряжения логической единицы, формируемой выходным узлом тестера.

При превышении напряжения на вхо- Зв де 14 напряжения на входе 15 компаратора 13 он срабатывает и уровень логического нуля, появляющийся на его выходе, через элемент 17 ИЛИ попадает на вход D триггера 18. 4e- реэ время задержки, определяемое периодом следования синхроимпульсов, уровень логического нуля появляется

1018064

Составитель В. Дворкин

Редактор К. Волощук Техред м,Тепер . Корректор С 1 екмар

Заказ 3538/45 Тираж 7.10 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент", r. Ужгород, ул. Проектная, 4