Преобразователь время-код

Иллюстрации

Показать всеРеферат

ПРЕОБРАЗОВАТЕЛЬ ВРЕМЯ - КОД, содержащий блок совпадения, первый вход которого соединен с выходом первого, блока задержки, второй вход соединен с выходом элемента ИЛИ и с входом первого блока задержки, а выход соединен с входом второго блока задержки, выход котгсдоого подключен к первому входу элемента ИЛИ, а также счетчик, отличающийс я тем, что, с целью расширения функциональных возможностей преобра зователя , в него дополнительно введены два блока задержки, два блока сов-, падения, блок сравнения кодов и счетчик , причем первый вход, первотчэ дополнительного блока совпадения соединен с выходом основного блока совпадения и с входами первого и второго дополнительного блока задержки, второй его вход соединен с выходом первого дополнительного блока задержки, а выход соединен с входом основного счетчика, выходы которого подключены к первым Bxojct .блока сравнения кодов, а выход второго дополнительного блока задержки соединен с входом допол- § г йительного счетчика, выходы которого, подключены к вторым входам блока ера в--; нения кодов, выход которого соединен с первым входом второго дополнительного блока совпадения, второй вход которого подключен к выходу элемента S ИЛИ. Ob о

СОЮЗ COBETCHHX

ОЗЮ ЯЮ

РЕСПУБЛИК

М5В С 04 F" 16 04

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ASTOPCK(MIV OBHggTEllbCTRV . (21) 3355366/18 «21 (22) 06.11.81 (46) 15.05.83.. Бюл; 1 18 (72) Г. Н. Абрамов (71) Ульяновский политехнический институт (53) .621.317(088.8) (56) 1. Авторское свидетельство СССР

В 241295, кл. G 04 F 10/00, 1969 °

2. Карпов И. Р. Рециркулярный измерительный преобразователь коротких интервалов в код. ПТЭ, 1980, Ю 2, с. 101-.1б3, рис. 1. (54)(57) ПРЕОБРАЗОВАТЕЛЬ ВРЕИИ вЂ” КОД, содержащий блок совпадения, первый вход которого соединен с выходом первого блока задержки, второй вход соединен с выходом элемента ИЛИ и с входом первого блока задержки, а выход соединен с входом второго блока задержки, выход которого подключен к первому входу элемента ИЛИ, а также счетчик, о т л и ч а ю щ и й„.SU„„1018101 А с я тем, что, с целью расширения функциональных воэможностей преобра- . ,.зователя, в него дополнительно введены два блока задержки, два блока сов-. падения, блок сравнения кодов и счетчик, причем первый вход. первого дополнительного блока совпадения соединен с выходом основного блока совпадения и -с входами первого и второго дополнительного блока задержки, второй его вход соединен с выходом первого дополнительного блока задержки, а выход соединен с входом основного счетчика, выходы которого подключены к первым входам блока сравнения кодов, а выход второго дополнительного блока задержки соединен с входом допол- I нительного счетчика, выходы которого. подключены к вторым входам блока срав-. нения кодов, выход которого соединен с первым входом второго дополнительного блока совпадения, второй вход которого подключен к выходу элемента Я

ИЛИ.

1018101

Изобретение относится к электроизмерительной технике и может быть использовано для измерения коротких (наносекундных) по длительности импульсов.

Известен преобразователь время— код, сОдержащий каскады грубого и точного отсчета, каждый из которых выполнен в виде ряда блоков задержки, подключенных своими выходами параллельно через соответствующие схе- 10 мы совпадения к общему. запоминающему устройству P1).

Недостатком указанного преобразователя является большой объем аппара- турных затрат, возрастающий с увели- 15 чением точности преобразователя.

Известен также преобразователь, содержащий схему совпадения, первый ,блок задержки, схему ИЛИ, счетчик и второй блок задержки f2).

Однако рассмотренный преобразователь обладает низким быстродействием.

Одним из путей повыаения быстродействия преобразования является переход к последовательно-параллельным структурам построения преобразователей время; — код, содержащим несколько однотипных каскадов, включенных последовательно.

25 дения, второй вход которого подключен к выходу элемента ИЛИ. 65

Цель изобретения — расширение 30 функциональных возможностей преобразователя для возможности его использования в каскаде последовательнопараллельного преобразователя времякод.

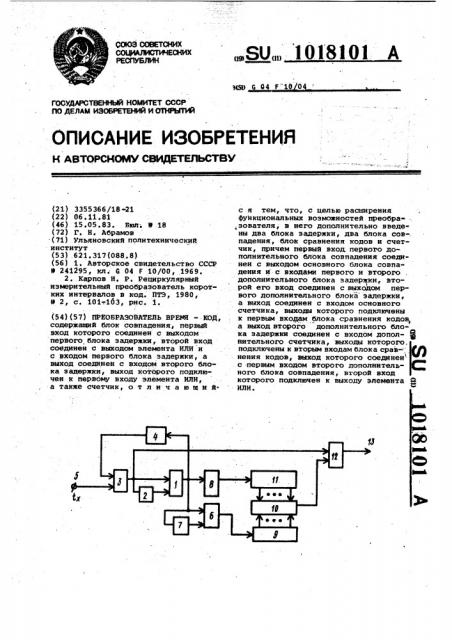

Поставленная цель достигается тем, что в преобразователь время — код, содержащий блок совпадения, первый вход которого соединен с выходом первого блока задержки, второй вход . соединен с выходом элемента ИЛИ и 40 с входом первого блока задержки, а выход соединен с входом второго блока задержки, выход которого подключен к первому входу элемента ИЛИ, а также счетчик, дополнительно вве- 45 дены два блока задержки, два блока совпадения, блок сравнения кодов и счетчик, причем первый вход первого дополнительного блока совпадения, соединен с выходом основного блока совпадения и с входами первого и второго дополнительного блока задержки, второй его вход соединен с выходом первого дополнительного блока задерж. ки, а выход соединен с.входом основного счетчика, выходы которого подключены к первым входам. блока сравнения кодов, а выход второго дополнительного блока задержки соединен с входом дополнительного счетчика, выходы которого подключены к вторым, 60 входам блока сравнения кодов, выход которого соединен с первым входом второго дополнительного блока совпаНа чертеже приведена функциональная схема предложенного преобразователя время - код.

Преобразователь состоит иэ блока 1 совпадения, блока 2 задержки, эле мента ИЛИ 3, блока 4 задержки, входа

5 преобразователя, блоков: 6 совпадения, 7 и 8 задержки, счетчика 9, блока 10 сравнения кодов, счетчика

11, блока 12 совпадения, выхода 13 преобразователя.

Преобразователь время - код работает следующим образом.

Перед началом измерения в счетчик

9 записывается "1", а счетчик 11 устанавливается в состояние "0". На вход 5 преобразователя подают одиноч" ный импульс, длительность tх которого подлежит измерению. Через элемент ИЛИ 3 он подается на второй вход блока 1 совпадения, на выходе которого вырабатывается импульс . длительностью b.е „ t - 3, где время задержки первого блока 2 задержки (это время выбирается исходя из требуемой точности преобразования).

Импульс длительностью at X подается на вход второго блока 2 задержки (время его задержки в должно превышать максимальную длительность преобразуемых импульсов) и на первый вход дополнительного блока 6 совпадения.

С его выхода снимается импульс длительностью дt x = htx - ty, где typ e время задержки дополнительного блока 7 задержки, причем t> t „. Этот импульс фиксируется в счетчике 9.

Одновременно импульс длительностью

Ьс, после задержки в блоке 8 задержки йа время t>> t> + tññü (где время задержки дополнительного блока 6 совпадения) фиксируется в счетчике 11. Блок 8 задержки введен для синхронной работы счетчиков.

После задержки во втором блоке 4 задержки, который должен обеспечить минимальйые искажения импульса, импульс tg через элемент ИЛИ 3 поступает на второй вход блока 1 совпадения, на выходе которого вырабатывается импульс. длительностью Ьй =htX< "

2, который также фиксируется в счетчике 11. В счетчике 9 также происходит фиксация, если с выхода первого дополнительного блока б совпадения снимается импульс длительностью дtx<= ье (Указанный процесс продолжается до тех пор, пока код, зафиксированный в счетчике 9, не равен коду, зафиксированному s счетчике. 11. В момент равенства кодов блок 10 сравнения кодов вырабатывайт сйгнал управления, который открыет дополнительный блок

12 совпадения и импульс длительностью

0 AX tg< с выхода элемента ИЛИ 3 проходит на выходе 13 преобразова1-018101 теля. Полученный таким образом им- После пятого такта блок 10 сравнепульс длительностью Atg> . поступает ния кодов вырабатывает сигнал управлена вход аналогичной - схема последу- ния на блок 12 совпадения, который ющего каскада. А циФровой результат через время the+ щ„(ецио„- время задержпреобразования W каскада может очи- ки элемента ИЛИ 3) появляется на вытываться с выходов любого из счетчи- ходе 13 преобразователя и может по5 ков. При этом блок 2 задержки:и до- даваться на последующий каскад преобполнительный блок 7 задержки должны р зователя. обеспечивать минимальные искажения при задержке импульсов. При этом циФровой. результат преобПример. Пусть ек 5,5 мкс, о разования рассмотренного каскада

t g, = 1 мкс, Емкость счетчиков - 4 бит. W (10101 = (5) с ° йачало измерения в счетчике 9 Приведем проверку: при правильном (СТ9,)-100, в счетчике 11 (СТ11)-0000; Функционировании должно быть tX н

1 такт: ate 4,5 мкс, СТ 9-0100; Wty„+ Мх. = 5,1 + 0,5. = 5,5 (мкс).

,СТ11-1000; - 15

11 такт, 3,5 мкс, СТ9-1100, . Таким образом, предлагаемы преСТ-0100; обраэователь в отличие от прототипа,.

1I! такт: дс .= 2,5 мкс, СТ9-0010; вырабатывает аналоговый сигнал bty< СТ11-1100, . t g - Wtyq, являющийся входным для

l× такт:=-it < 1,5 мкс, СТ9-1010; ;у,последующего каскада, т.е. возможно построение преобразователей время1

V такт: at = 0,5 мкс, СТ9-1010 код при высокой точности с небольшими так как at c ез,); СТ11-1010.,аппаратурными затратами.

Составитель Н. Муляр

Редактор М.Келемеш Техред Т.Фанта Корректор E. Рошко

Заказ 3542/47 Тираж 411 Подписное

RHHHPN Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. ужгород, ул. Проектная, 4