Устройство для обнаружения и исправления ошибок в блоках памяти

Иллюстрации

Показать всеРеферат

ае а) ССК)3 СОВЕТСКИХ

: ICINIIII

РЕСПУБЛИК (.ССУДАРОТЩКНЫЙ КОМИТЕТ СССР

FO ДЕЛАМ ИЗО6РЕТЦ1ИЙ,,И ОТНРЦТЗФ

ОПИСАНИЕ ИЗОБРЕТ н автеснаа свЮЮв ьстеу

J (21) 3354581/18-.24 - .. дешифратаров подключены соответствен(.22) 20,11.81 .. но к -одним из вкодов элементов ИЛИ, . (46) 15,05.83.- Бюл.918 : о т л и ч а ю щ е е с я тем, что, (72) А.В. Иаркарян и Л.M. Чахоян с целью повъкаения -быстродействия (53); 681.327(088.8) . устройства, в него"введены.третий (56) 1. Патент Qi® В. 4064483, ... и четвертый преобразователи кодов, кл. 340-146.1АЬ, опублик. 1977, .третий дещифратор и сумматоры, причем

2. Патент CRT 9 4030067, кл.340- . ..входы- Третьего преобразователя: кодов

146.1AL,- опублик. 1977 (прототип). соединены с другими вйходами формнроЗ,Берлекэмп. S..Àïãåáðàa÷ecêàÿтеорйя-. 1вателя контрольных сигналов, один крдирования. И., ".Мир", 1971, с.134, -, из.выходов которого является унрав135,150,151.,:: ляющим, выходы третьего преобразова4. Мак-Вйльямс Теория кодов, ис- теля кодов-шщключены к одним из ахоправлякщих сиаибки. И., "Связь", 1979, дов первого сумматора,.другие входы с,91. . :: которого соединены.с выходами первого (54)(57) УСТФОИСТВО.:ДЛЯ ОБНАРУЖЕНИИ- нреобразователя кодов и одними из

И .ИСПРАВЛЕНИЙ ОШИБОК: В ESlOKAX ПИЛИ, входов втоРого сУиматоРа, дРУгие g . содержащее блок управления, блок кор- нкоды которого подключены к выходам рекцин, Формирователь контрольных второго преобразователя кодов, а высигналов,:первый и второй предобра =" -. ходы - к- одним из входов первого зователи кодов,:дещйфраторы, .элемен- дещнфратора и третьего .сумматора,. выты ИЛИ и элемейты .И, причем один as хоДы которого соедииены с одним нз .входов блока коррекции являются входов второго деюнфратора, а дру- о входаий устройства, другие входи : .. гие входы - с выходами четвертого блока, коррекции подключены соответст- преобразователя кодов, входы которог венно к выходу блока управления и к соединены с выходами первого суммавыходам элементов ИЛИ, а выходы - —, тора, входавэю второго преобразоватеtc входам формирователя контрольных -: . ля кодов .и другиваю входами элементов сигналов, одни из выходов которого . И,.другой выход которых подключен соединены соответственно с входами -:к другим входам. первого и второго ..первого преобразователя кодов и .с .. деаифраторов и одним йз входов. третье-" однйми нз входов элементов И, один из го деанФратора, другие входы котовыходов которых. соединей с входом:рого соединены с входами первого блока.управления и является выходом . преобразователя кодов, а выходы— устройства; выходы первого и второго с другими входами -элементов или, 1018151

Изобретение относится к запоминающим устройствам и может быть использовано для контроля оперативных и постоянных запоминающих устройств.

Известно устройство для обнаружения и исправления ошибок в блоках памяти, в котором используется блок возведения в куб для коррекции двойных ошибок и принцип последовательного перебора со сравнением соответствующих значений для обнаружения места ошибочного бита информации (1).

Недостатком этого устройства является,низкое быстродействие.

Наиболее блиэкйм к изобретению является устройство для обнаружения 15 исправления ошибок в блоках памяти, содержащее блок управления, регистр информации, генератор контрольного сигнала, два блока умножения, два преобразователя кода, два дешиф- 2О ратора, элементы ИЛИ и И, причем первые входы регистра информации подключены к входам устройства, вторые — к выходам элемента ИЛИ, третий вход — к выходу блока управления а выходы — к входам генератора контрольного сигнала, первые выходы которого подключены к входам первого преобразователя кода, третий выход— к входу элемента И, первый выход которого йодключен к первому входу блока управления и к выходу устройства, выходы первого и второго дешифраторов подключены к входам элемента ИЛИ f21.

Недостатком этого устройства яв« ляется низкое быстродействие вследствие того, что время исправления одиночных и двойных ошибок в регистре информации одинаково.а скорость исправления двойных и обнаружения 4О тройных ошибок обусловлейа использованием двух медленно действующих блоков умножения.

Цель изобретения — повышение 45 быстродействия устройства.

Поставленная цель достигается тем, что в устройство для обнаружения и исправления ошибок в блоках памяти, содержащее блок управления, блок коррекции, формирователь контрольных сигналов, первый и второй преобразователи кодов, дешифраторы, элементы

ИЛИ и элементы И, причем одни из входод блока коррекции являются входами устройетва, другие входы блока коррекции подключены соответственно к выходу блока управления и к выходам элементов ИЛИ, а выходы — к входам формирователя контрольных сигналов, одни из выходов бО которого соединены соответственно с входами первого преобразователя кодов и с одними из входов элементов И, один из выходов которых соединен с входом блока управления и у является выходом устройства, выходы первого и второго дешифраторов подключены соответственно к одним нз входов элементов ИЛИ, введены третий и четвертый преобразователи кодов, третий дешифратор и сумматоры, причем входы третьего преобразователя кодов соединены с другими выходами формирователя контрольных сигналов, один из выходов которого является управляющим, выходы третьего преобразователя кодов подключены к одним из входов первого сумматора, другие вхо- ды которого соединены с выходами первого преобразователя кодов и одними иэ входов второго сумматора, другие входы которого подключены к выходам второго преобразователя кодов, а выходы - к одним из входов первого дешифратора и третьего сумматора, выходы которого соединены с одним из входов второго дешифратора, а другие входы — с выходами четвертого преобразователя кодов, входы которого соединены с выходами первого сумматора, входами второго преобразователя кодов и другими входами элементов И, другой выход которых подключен к другим входам первого и второго дешифраторов и одним из входов третьего дешифратора, другие входы которого соединены с входами первого преобразователя кодов, а выходы - с другими входами элементов

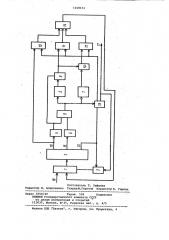

ИЛИ, На чертеже изображена функциональная схема предложенного устройства. устройство содержит блок 1 коррекции, формирователь 2 контрольных сигналов, блок 3 управления, первый 4 второй 5, третий 6 и четвертый 7 нреобразователи кодов, первый 8, второй 9 и третий 10 сумматоры, первый 11, второй 12 и третий

13 дешифраторы, элементы HJIH 14 и элементы И 15. На чертеже обозначены входы 16 и один из выходов 17 устройства, выходы 18, 19 и 20 формирователя контрольных сигналов.

Устройство работает следующим образом.

С входа 16 поступает(I(+1) -разрядный код (где К - целое число в параллельной форме на запись в блок 1, с выхода которого этот код поступает в формирователь 2.В случае одиночной ошибки а (k+1 - разрядном коде на выходах 18 формирователя 2 вырабатывается код коррекции ошибки 5„, а на выходе 20 - сигнал нечетной ошибки, который поступает на второй вход блока 3. Код коррекции ошибки поступает на первые входы дешифратора 13, который через элементы NIH 14 на входы блока 1 выдает код, указывакщий неисправный разряд в блоке 1, одновременно с выхода блока 3 на вход блока 1 поступает

1018151 сигнал, разрешающий коррекцию. В ре= зультате в блоке 1 корректируется .поступивший в него код.

В случае двойной ошибки в (К +1)разрядном коде на выходах 18 и 19 формирователя вырабатываются соот- 5 ветственно коды коррекции ошибок

5 и, а на выходе 20 сигнал не-. четной ошибки отсутствует. Коды 5 и S< соответственно поступают на входы преобразователей 4 и б. Пре- 10 образователь 4 выдает на входы сумматоров 8 и 9 Ь (к+1)- разрядный код p > а преобразователь б выдает на другие входы сумматора 8йоф (к+1)разрядный код .ф . С выхода суммато- 5 ра 8 на входы преобразователей 5 и 7 и элементов И 15 поступает результат суммы(р+ф)МО по ñ3К . При(р+ )Ф О и отсутствии сигнала нечетной ошибки на выходе 20-с выходов элементов 20

И 15 на вход дешифратора 13 выдается сигнал блокировки, а на входы дешифраторов 11 .и 12 - сигналы разблокировки. Преобразователь 5.выдает на другие входы суьвюатора.98)(rp+13 - . разрядный код. С выходов сумматора 9код и< поступает: на, одни иэ входов дешифратора-и на входы сумматора 10, на другие входы которого поступает

0ОЩ(к+12- разрядный. код X. Реэультаг сложения этих кодов с выходов суякатора 10 поступает на одни из выходов дешйфратора 12. Дешифраторы 11 и 12 через элементы ИЛИ 14 .на входы блока

1 выдают код, указывающий неисправные разряды в блоке 1, на вход которого с вйхода блока 3 одновременно поступает сигнал, разрешающий коррекцию. В результате код в блоке 1 кор;ректируется.

В случае тройной ошибки в(К+1) - 40 разрядном коде на входе 1б в отличие от двойной при(Р+ ) ФО и наличии сигI нала нечетной ошибки на выходе 20 формирователя 2 на выход 17 элементов И 15 и на первый вход блока 3 выдается сигнал тройной ошибки, а с других .выходов элементов И 15 на вход дешифратора 13 поступает сигнал раэблокировки, а на входы дешифраторов

11 и 12 — сигнал блокировки.

При этом. коррекция информации в блоке 1 производится дважды: сначала по сигналу нечетной ошибки в соответ.ствии с кодом S осуществляется коррекция в блоке 1 так же, как и р случае одиночной ошибки в поступив-. шем на вход 16 коде, а затем блок

3 по сигналу тройной ошибки, выдает сигнал, разрешающий коррекцию также в соответствии с кодом 3„ . Таким образом, информация в блоке 1 восq7àíàâëèâàåòñÿ, а на выход 17 выдается сигнал тройной ошибкн.

В случае отсутствия ошибки в пос- тупившем на вход 16 коде формирователем 2 вырабатываются нулевые коды

Я„. и S а сигнал нечетной ошибки отсутствует. В результате информация в блоке 1 остается без изменения.

Коррекция информации.в блоке 1 осуществляется в соответствии с алгоритмами f 3) и (4).

Таким образам, в предложенном устройстве в отличие от-прототипа вместо медленно действующих блоков умножения использованы быстродействующие сумматоры, а коррекция одиночной ошибки производится по максимально укороченному пути, что позволяет значительно сократйть время коррекций,одиночных, двойных и обнаружения тройных ошибок.

Технико-экономическое преимущест-.

so предложенного устройства заключается в его более высоком быстродействии по сравнению с прототипом.

1018151

Составитель Т. Зайцева

Редактор Л. Алексеенко ТехредМ.Гергель Корректор В. Гирняк

Заказ 3550/49 Тираж 594 Подписное

ВНИИПИ Государственного комитета СССР о по делам изобретений и открытий

113035, Москва, Ж-35 Раушская наб., д. 4/5

Филиал ППП Патент" r. Ужгород, ул. Проектная, 4