Резервированное запоминающее устройство

Иллюстрации

Показать всеРеферат

РЕЗЕРВИРОВАННОЕ ЗАПСШ НАЮЩЕЕ УСТРОЙСТВО, содержащее накопитель, входы которого подключены к выходам дешифратора, выход накопителя подключен к входу блока контроля и является информационнш1 выходом устройства, сумматор, выходы которого подключены к информационным входам первого per гистра, адресный регистр, входы которого являются адресными входами устройства , второй регистр, отличающееся тем, что, с целью повышения надежности устройства, оно содержит группы элементов И, элементы ИЛИ, генератор и элемент И, выход которого подключен ю первому управля-. кшему входу первого регистра и является управляющим выходом устройства, выход генератора подключен к вторым управляющим входам первого регистра, одни выходы которого подключены к первым входам элементов И первой группы и к одним входам эл и1ейта И, одни выходы адресного регистра подключены к одним эходам сумматора и к вторым входам элементов И первой группы, выходы которых подключены к первым входам элементов ИЛИ« другие выходы первого регистра подключены к первым входам элементов И второй группы, вто рые входы которых подключены к другим выходам адресного регистра, выхо-fj Яы элементов И второй rpynntS прдклю- 1 чены к вторым входам эл0 ентов ИЛИ, |С// выходы которых подключены к входам дешифратора, выход блока контроля подключен к другому вхсщу элемента И, другие входы сумматора подключены к S выхоДсил второго регистра., входы которого являются Управляющими входами устройства.

,SU„„1018152 А

COOS СОВЕТСКИХ

NWNINI

РЕСПУБЛИК (511 G 11 С 29/00

ГОСУДАРСТЯЕНКЫЙ КОМИТЕТ СССР

f}O ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

1 т б . (-,: .. ; :.; а

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (21 ) 3 35654 2/18-24 (22) 20.08.81 (46) 15.05.83. Вюл. 9. 18 (72) П.И.Луговцов и Н.Г.Луговцова (53) 681,327 о б{088.8) (56) 1.. Авторское свидетельство СССР

В 720539, кл. G 11. С 29/00, 1978.

2. Авторское .свидетельство СССР

В 640375, кл. G 11 С 29/ОЬ, 1977 (прототи ) ° (54 } (57) РЕЗЕРВИРОВАННОЕ ЗАПОИИНИОЩЕЕ

УСТРОЙСТВО, содержащее накопитель, входы которого подключены к выходам деши4ратора, выход накопителя подключен к входу блока контроля и является информационным выходом устройства, сумматор, выходы которого подключены к информационным входам первого ре-. гистра, адресный регистр, входы которого являются адресными входами устройства,.второй регистр, о т л ич а ю щ е е с я тем, что, с целью повышения надежности устройства, оно содержит группы элементов И, элементы ИЛИ, генератор и элемент И, выход которого подключен к. первому управляющему входу первого регистра н является управляющим выходом устройства, выход генератора подключен к вторым управлякщим входам первого регистра, одни выходы которого подключены к первым входам элементов И первой группы и к одним входам элемента И, одни вы-. ходы адресного регистра подключены е к одним Входам сумматора и к вторым входам элементов И первой группы, выходы которых подключены к первым входам элементов ИЛИ,;другие выходы первого регистра подключены к первым входам элементов И второй группы, вто рые входы которых подключены к друФ гим выходам адресного регистра, выхо-9

Жи элементов И второй группы подключены к вторым входам элементов ИЛИ, выходы которых подключены к входам деши4ратора, выход блока контроля подключен к другому входу элемента И, другие входы сумматора подкл1очены к я выходам второго регистра, входы которого являются управлякщнми входами устройства. М®

1018152

Изобретение относится к запоминаю. щим устройствам (ЗУ).

Известно резервированное запоминающее устройство, содержащее основ,ные и резервные блоки памяти, числовые регистры, информационные входы которых соединены с соответствующими выходами основных блоков памяти, блоки управления и контроля, регистры тказов и контроля, сумматоры по моулю два, элементы И, НЕ и ИЛИ, при- 10 ем одноименные выходы основных и резервного блоков памяти соединены с входами сумматоров по модулю два, выходы которых соединены с первыми входами первых элементов И, выходы кото-15 рых соеДинены с входами регистра конт роля и через элемент ИЛИ с входом блока контроля, выходы блока контроля соединены.с первыми входами блока управления, вторые входы которого соединены с выходами регистра контроля, выходы блока управления соединены с входами регистров отказов, одноименные выходы которых соединены с вторым, третьим и четвертым входами соответствующих первых элементов И, выход .первого и второго регистров отказов через элементы НЕ соединены с первыми входами вторых элементов И, вторые входы которых соединены с вы- . ходами соответствующих сумматоров по модулю два, выходы вторых элементов

И подключены к управляющим входам числовых регистров (1).

Недостатками устройства являются его значительная аппаратурйая избыточ.35 ность и низкая эффективность использования емкости ЗУ в случае наличия в нем свободных ячеек (адресов памя. ти), что:.снижает надежность запоминающего устройства. 40

Наиболее близким к предлагаемому является резервированное запоминающее устройство, содержащее регистр числа, регистр адреса, выходы которого подключены к входам рабочих и 45 резервного блоков памяти, коммутаторы, блок контроля, дополнительный регистр и сумматор, входы которого подключены соответственно к выходам резервного блока памяти и первого коммутатора, а выход соединен с входом дополнительного регистра, выходы рабочих блоков памяти и один из выходов регистра адреса подключены соответственно к входам первого коммутатора и второго, коммутатора, выход ко 55 торого соединен с входом регистра числа, входы третьего коммутатора подключены соответственно.к выходам регистра числа дополнительного регистра и блока контроля, вход которого 60 соединен с выходом регистра числа (2), Недостатком, этого устройства является низкая эффективность использова" ния емкости ЗУ в случае наличия в вем свободных ячеек (адресов) памяти,.65 что снижает надежность запоминающего устройства.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что в резервированное запоминающее устройство, содержащее накопитель, входы которого подключены н выходам дешифратора, выход накопителя подключен к входу блока контроля и является информационным выходом устройства; сумматор, выходы которого подключены к информационным входам первого региСтра, адресный регистр, входы которого являются адресными входами устройства,второй регистр, введены группы. элементов .И,элементы ИЛИ,генератор и элемент.И,выход которого подключен к первому управляющему входу первого регистра и является управлякщим выходом . устройства, выход генератора подключен к вторым управляксцим входам первого регистра, одни выходы которого подключены к первым входам элементов И первой группы и к одним входам элемента И, одни выходы адресного регистра подключены к одним входам сумматора и к вторым входам элементов

И первой группы, выходы которых подключены к первым входам элементов

ИЛИ другие выходы первого регистра подключены к первым входам элементов

И второй группы, вторые входы которых подключены к другим выходам адресного регистра, выходы элементов И второй группы подключены к вторым входам элементов ИЛИ, выходы которых подключены к входам дешифратора, выход блока контроля подключен к другому входу элемента И, другие входы сумматора подключены к выходам второго регистра, входы которого являются управлякхцими входами устройства.

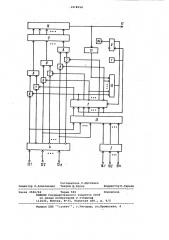

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит генератор 1, регистр 2, регистр 3, адресный регистр 4, триггер 5, группу элементов

И 6, группу элементов И 7, элементы

ИЛИ 8, дешифратор 9 накопитель 10, блок 11 контроля, элемент И 12, сумматор 13, элемент 14 индикации, адресные входы 15 управляющие входы 16 и информационный выход 17.

В основу работы устройства положен способ преобразавания кода адреса, поступакшего от устройства — потребителя ЗУ, в специальный корректирующий код, с помощью которого производится переадресация обращения к другой ячейке для исключения выборки отказавшей ячейки накопителя. Применение метода переадресации ие влияет на совместную работу Зу (например, оперативного запоминающего устройства или буферного запоминающего устройства) с устройством потребителя, так как переадресация производится непос1018152 редственно в ЗУ и потребителю в общем безразлично, к какой ячейке накопителя производится обращение по указанному им адресу.

Устройство работает следукщим образом. 5

После подачи питающих напряжений генератор 1 вырабатывает одиночный импульс, который устанавливает пер" вый регистр. 2 и триггер 5 в нулевое состояние. Во второй регистр 3 любым 10 известным способом записывается код . исправной свободной ячейки (адреса) .

Выборка адреса-в режимах записи или считывания производится следующим образом. 15

Адрес ячейки, к которой необходимо обратиться, записывается в. адрес- ный регистр 4. Код адреса с регистра. .4 через открытые элементы И 6 и элементы ИЛИ 8 поступает на вход двшифратора 9, нри этом возбуждается одна из выходных шин дешифратора, соответствукМая ячейке накопителя 10, в которую необходимо записать или из которой необходимо считать информа" цию е

При работе устройства при отсутст. вии отказавших ячеек накопителя 10 код адреса, поступающий на адресные . шины устройства, не подвергается прв-ЗО образованию перед подачей его на -вход дешифратора 9.

В случае появлейия ошибки в считанной информации на выходе блока 11 контроля формируется импульс, которыйЗ5 через элемент И 12 поступает на Вход .регистра 2, разрешая запись текущего кода с выхода сумматора 13 в регистр

2. Сумматор 13 служит для сложения текущего кода адреса исправной -cso- -40 бодной ячейки (адреса), записанного в регистр 3. После занесения в регистр 2 кода с выхода сумматора 13 закрывается элемент И 12, блокируя в вго от дальнейшего приема информации 45 с выхода сумматора 13. Таким образом, в регистре 2 фиксируется результат сложения, кодов отказавшей рабочей и исправной свободной (резервной). ячеек накопителя 10.

После обнаружения неисправной ячей ки устройство работает следукщим образом.

В.регистр 4 записывается код адреса, который перед подачей его на вход

/ дешифратора 9 подвергается автоматическому преобразованию s корректирующий код. Преобразователь входного кода адреса и корректирукщий осуществляется следукнцим образом. Под воздействием сигналов высокого уровня с нулевых и единичных выходов регистра 2 открываются соответствующие элементы

И 6 и 7, в результате чего входы дешифратора 9 поразрядно коммутируются с нулевыми и единичными выходами регистра 4. Таким образом, на вход .дешифратора 9 вместо входного кода ад" реса поступает корректирукиций код, под действием которого возбуждается одна из выходных шин дешифратора, со:ответствующая ячейке накопителя 10, в которую записывается или из которой считывается информация. При этом при обращении к отказавшей ячейке накопителя происходит выборка свободной (резервной) ячейки, код которой записан в регистре 3. Прй обращении к любой исправной ячейке йроисходит выборка соответствующей ей другой ис правной ячейки.

Корректирующий ксд образуется путем сложения по модулю два текущего кода вдреса с фиксированным кодом, записанным в регистре 2.

Сложение по модулю два текущего кода адреса и фиксированного в регистре 2 кода производится элементаМи И б и 7 и элементами ИЛИ 8.

Триггер 5 и элемент индикации служат для визуального контроля режима работы устройства. До включения резервной ячейки вместо отказавшей триггер 5 переключается в единичное состояние, о чем свидетельствует воэ бужденне элемента 14. индикации.

Изобретение имеет более высокую эффективность использования емкости

ЗУ в случае наличия в нем свободных ячеек (адресов) памяти, которые ис- . пользуются -в качестве резервных для замещения отказавших рабочих ячеек (адресов), что позволяе повыоить надежность эапоминакщего устройства.

В устройстве обеспечивается замещение любой отказавшей ячейки накопителя резервной. Поиск неисправной ячейки и включение вместо ее резервной производится автоматически, что значительно снижает время ремонтно-восстановительных работ при эксплуатации устройства;,101а1Ы

Составитель С.Шустенко

Редактор Л.Алексеенко Техред М.Тепер

Корректор В. Гирняк

Под пис ное

Филиал ППП l.àòåíò, г.ужгород, ул.Проектная, 4

Заказ 3550/49 Тираж 594

ВНИИПИ Государственного комитета СССР по делам изобретений и открыти

113035, Москва, Ж-35, Рауыская наб., д. 4/5