Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ , содержащий сравнивающее устройство, узел суммирования напряжения , первый преобразователь кода в напряжение, регистр триггеров с узлом переноса единицы, элементы совпадения , распределитель тактовых импульсов , дополнительные элементы совпадения младших разрядов, второй преобразователь кода в напряжение, тактовый генератор, через который вход запуска соединен с входом распределителя тактовых импульсов, первый выход которого соединен с входом включения разрядов второго преобразователя кода в напряжение и входом установки единицы триггера старшего разряда . регистра с узлом переноса .единицы триггеров, последующие выходы распределителя тактовых импульсов соединены с входами установки единицы следующих триггеров регистра триггеров с узлом переноса ёди(Гицы и через элементы совпадения , с входами установки нуля предыдущих триггеров регистра триггеров с узлом переноса единицы, а выходы распределителя тактовых импульсов, управляющие коррекцией, соединены с первыми входами дополнительных элементов совпадения младших разрядов , вторые входы которых и управляющие входвд элементов сов падения подключены к выходу сравнивающего устройства,, выходы регистра триггеров с узлом переноса единицы соединены с соответствующими входами первого преобразователя кода в напряжение, выход которого соединен с первым входом узла суммирования напряжений, второй вход котррого соединен с выходом второго преобразователя кода в напряжение, а I выход - с первым входом сравнивающего устройства, второй вход которого СО соединен с шиной преобразуемого напряжения , о тли ч а ю щ и йся тем, что, с целью уменьшения динамической погрешности, в него введены дополнительные элементы ИЛИ, узе.л коррекции и триггеры, входы которых соединены с выхоцами соответствуквдих дополнительных элементов совпадения, а выходы - с входами узла коррекции и через дополнительные элементы ИЛИ 00 tvD с входами второго преобразователя кода в напряжение, вторые входы дополнительных элементов ИЛИ соединены to с соответствующими выходами распределителя тактовых импульсов, управ J ляющих коррекцией, дополнительный выход которого соединен с управляющим входом узла коррекции, выходы которого соединены с соответствукиинми входами переноса регистра триггеров с узлом переноса единицы.

союз советсних

С и /ЮЛИ

РЕСПУБЛИК э(Я) Н 03 К 13/

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ОО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМ У СВИДЕТЕЛЬСТВУ (21 ) 3279959/1 8-21 .(22 ) 29. 04. 81 (46) 15.05. 83. Вюл. Р 18 (72) B.È. Матвиив, И.Д. Козицкий, В.В. Островерхов и. Е.М. Шевчук (53) б81..325 (088.8 ) (.56) 1. Островерхов В.В.. Динамические погрешности АЦП. 1975, с. 138149.

2. Авторское свидетельство СССР

9 330538, кл. Н 03 К 13/17, 1970 (прототип).. (54)(57).АНАЛОГО-ЦИФРОВОИ ПРЕОБРАЗОВАТЕЛЬ, содержащий сравнивающее устройство, узел суммирования напряжения, .первый преобразователь кода в напряжение, регистр триггеров с узлом переноса единицы, элементы совпадения, распределителььтактовых импульсов, дополнительные элементы совпадения младших разрядов, второй преобразователь кода в напряжение, тактовый генератор, через который вход .запуска соединен с входом распределителя тактовых импульсов, первый выход которого соединен с входом включения разрядов второго преобразователя кода в напряжение и входом устаиовки единицы триггера старшего разряда. регистра с узлом переноса .единицы триггеров, последующие выходы распределителя тактовых импульсов соединены с входами установки единицы следующих триггеров регистра триггеров с узлом переноса единицы и через элементы совпадения с входамк установки нуля предыдущих триггеров регистра триггеров с узлом переноса единицы, а выходы,„SU„„1018227 А распределителя тактовых импульсов, управляющие коррекцией, соединены с первыми входами дополнительных элементов совпадения младших разрядов, вторые входы которых и управляющие входы элементов сов падения подключены к выходу сравнивающего устройства, выходы регистра триггеров с узлом переноса единицы соединены с соответствующими входами первого преобразователя кода в напряжение, выход которого соединен с первым входом узла суммирования напряжений, второй вход которого соединен с выходом второго преобразователя кода в напряжение, а выход — с первым входом сравнивающе- I го устройства, второй вход которого соединен с шиной преобразуемого напряжения, отличающийся тем, что, с целью уменьшения динамической погрешности, в него введены дополнительные элементы ИЛИ, узел коррекции и триггеры,. входы которых соединены с выходами соответствующих М® дополнительных элементов совпадения, а выходы — с входами узла коррекции и через дополнительные элементы ИЛИ с. входами второго преобразователя Я© кода в напряжение, вторые входы дополнительных элементов ИЛИ соединены Ьа) с соответствующими выходами распре- фф делителя тактовых импульсов, управляющих коррекцией, дополнительный выход которого соединен с управляющим входом узла коррекции, выходы которого соединены с соответствующими входами переноса регистра триггеров,фЬ с узлом переноса единицы.

1018227

Изобретение относится к электроизмерительной и вычислительной технике.

Известны аналого-цифровые преобразователи с коррекцией динамических погрешностей (1 g. 5

Известен аналого-цифровой преобразователь, содержащий сравнивающее устройство, узел суммирования напряжений, первый преобразователь кода н напряжение, регистр триггеров с узлом переноса единицы, элементы совпадения, распределитель тактовых импульсов, дополнительные элементы совпадения младших разрядов, второй преобразователь кода в напряжение, тактовый генератор через который вход запуска соединен с входом распределителя тактовых импульсон, первый выход которого соединен с входом включения разрядов второго преобразователя кода в напряжение и 20 входом установки единицы триггера старшего разряда регистра триггеров с узлом переноса единицы, следующие выходы распределителя тактовых им-. пульсов соединены с входами уста- 25 нонки единицы последующих триггеров регистра триггеров с узлом переноса единицы и через элементы совпадения с входами установки нуля предыдущих триггеров регистра триггеров З0 с узлом переноса единицы, а выходы распределителя тактовых импульсов, управляющие коррекцией, соединены с первыми входами дополнительных элементов совпадений младших разрядов, вторые входы которых и управляющие входы элементов совпадения подключены к выходу сравнивающего устройства, выходы регистра триггеров с узлом переноса единицы соединены с соответствующими входами 40 первого преобразователя кода в напряжение, выход которого соединен с первым входом узла суммирования напряжений, второй вход которого соединен .с выходом второго преобразовате- 45 ля кода в напряжение, а выход - с первым входом сравнивающего устройства, второй вход которого соединен с шиной преобразуемого напряжения

С2 3.

Недостатком известного устройства . является наличие динамической пог решности за счет больших скачков напряжения на входе сравнивающего устройства, возникающих н процессе переноса единицы в тактах коррекции по разрядам регистра триггеров, которые последовательно включают и выключают разряды первого преобразователя кода в напряжение. При боль- 60 шом разбалансе напряжений сравнивающее устройство входит в насыщение и в результате этого на следующем такте сравнения увеличивается время восстановления. 65 целью изобретения является умень шение динамической погрешности.

Указанная цель достигается тем, что в аналого-цифровой преобразователь, содержащий сравнивающее устройство, узел суммирования напряжений, первый преобразователь кода в напряжение, регистр триггеров с узлом переноса единицы, элементы совпадения, распределитель тактовых импульсов, дополнительные элементы совпадения младших разрядов, второй преобразователь кода в напряжение, тактовый генератор, через котоРый вход запуска соединен с входом распределителя тактовых импульсов, первый.ныход которого соединен с входом включения разрядов второго преобра зонателя кода в напряжение и входом установки единицы триггера старшего разряда регистра триггеров с узлом переноса единицы, последующие выходы распределителя тактовых импульсов соединены с входами установки единицы следующих триггеров регистра триггеров с узлом переноса единицы и через элементы совпадения с входами установки нуля предыдущих триггеров регистра триггеров с узлом переноса единицы, а выходы распределителя тактовых импульсов, упранляющие коррекцией, соединены с первыми входами дополнительных элементов совпадения младших разрядов, вторые входы которых н управляющие входы элементов совпадения подключены к выходу сравнивающего устройства, выходы регистра триггеров с узлом переноса единицы с соответствующими входами первого преобразователя кода н напряжение, выход которого соединен с первым входом узла суммирования напряжений, второй вход которого соединен с выходом второго преобразователя кода н напряжение, а выход — с первым входом сравнивающего устройства, второй вход которого соединен с шиной преобразуемого напряжения, введены дополнительные элементы ИЛИ, узел коррекции и триггеры, входы которых соединены с выходами соответствующих дополнительных элементов совпадения, а выходы — с входами узла коррекции и через дополнительные элементы

ИЛИ вЂ” с входами второго преобразователя кода в напряжение, вторые входы дополнительных элементов ИЛИ соединены с соответствующими выходами распределителя тактовых импульсов, управляющих коррекцией, дополнительный выход которого соединен с управляющим входом узла коррекции, выходы которого соединены с соответствующими входами переноса регистра триггеров с узлом переноса единицы.

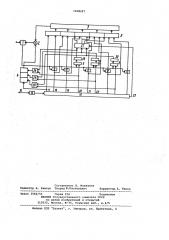

На чертеже приведена схема предлагаемого аналого-цифрового преобраэонателя.

1018227

S0

Устройство содержит сравнивающее устройство 1, узел 2 суммирования напряжений, преобразователи 3 и 4 кода в напряжения (ИКН), регистр 5 триггеров с учетом переноса единицы, элементы 6-13 совпадения, тактовый генератор 14 распределитель 15 тактовых импульсов, вход 16 и выходы

17-23, дополнительные элементы 2426 ИЛЙ, узел 27 коррекции и триггеры 28-30.

Аналого-цифровой преобразователь работает следующим образом.

По сигналу запуска на входе 16 с тактового генератора 14 поступают импульсы на распределитель 15, который первым импульсом формирует на выходе 17 импульс,при этом включаются все разряды второго преобразоваи теля 4 кода. в напряжение U =) U к -1 К и старший разряд преобразователя 3 кода в напряжение U. ii.Uö..

Выходные напряжения преобразователей 3 и 4 поступают на узел суммирования 2, а затем на один из входов сравнивающего устройства 1, на второй вход которого поступает преобразуемое напряжение. С приходом второго импульса с тактового ге.нератора 14 на вход распределителя

15 заканчивается импульс на выходе

17 и формируется следующий импульс на выходе 18, передним фронтом которого производится опрос сравниваи ющего устройства 1. Ilp ig + » U, >U р „к1 х на. выходе сравнивающего устройства ,.1 формируется сигнал логической

"1" и сигнал с выхода 18, через элемент 9 совпадения, устанавлива.ет триггер старшего разряда регистГ ра 5 в нулевое состояние. При этом старший разряд преобразователя 3 кода э напряжение выключается. и

E äôÖ + U . < 0 на выходе сравниО,, Къ

i= 1 эающего устройства 1 формируется сигнал логического нуля и сигнал с выхода 18 .распределителя 15 через элемент 9 совпадения не проходит и триггер старшего разряда регистра 5 остается в единичном состоянии, и следовательно, старший разряд преобразователя 3 остается во включенном состоянии.

Передним фронтом. импульса с выхода 18 также устанавливается э единичное состояние триггер второго разряда регистра 5 и соответственно включается второй разряд преобразователя 3, опрос которого происходит аналогично первому разряду передним фронтом импульса с выхода 19, который одновременно включает s единичное состояние триггер третьего разряда регистра 5. При этом включается третий разряд преобразователя 3, вес которого равен .старшему разряду второго преобразователя 4.

Если в результате сравнения измеряемого О„. и набранного значения U+> сравнивающее устройство выдает сигнал "1"(О, „ (О„, то при совпадении единичных. сигналов с выхода 20 распределителя 15 и с выхода сравнивающего устройства 1, элемент 6 совпадения устанавливает триггер 28 .в единичное состояние. При этом выход. ной сигнал триггера 28 через элемент

24 ИЛИ удерживает включенный старший разряд второго преобразователя 4..

Если со сравнивающего устройства поступает "0", то триггер 28 в единичное состояние не устанавливается и разряд коррекции выключается.

По командам распределителя 15 на следующих тактах с выходов 21 и 22 аналогичным образом осуществляется опрос и коррекция остальных разрядов АЦП.

После окончания уравновешивания с дополнительного выхода 23 распределителя 15 поступает сигнал на вход узла 27 коррекции, который производит последовательно перенос "1" из триггеров 28-30 в регистр 5 ° После этого выходной код регистра 5 соответствует преобразуемому напряжению.

-Так как коррекций кода s регистре триггера производится после процесса уравновешивания, то скачки, возникающие на входе сравнивающего устройства в результате переключения разрядов ПКН при переносе

"1" в регистре триггеров, не влияют на результат преобразования.

В результате использования предлагаемого устройства уменьшается динамическая погрешность, возникающая за счет входа в режим насыщения сравнивающего устройства.

101ВгЛЗ

Составитель В. Махнанов

Редактор A. Химчук Техред Ж.Кастелевич Корректор,А. Тяско

Заказ 3560/53 Тираж 936 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ПГН "Патент", г. Ужгород, ул. Проектная, 4