Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ , СОСТОЯЩИЙ из;двух ступеней, : каждая из которых содержит компараторы и ИСТОЧНИК эталонных напряжений, выходы последних подключены к первым входам компараторов сО1Этветствующей ступени, вторые входы компараторов первой ступени подключены к ВХОДНОЙ iiffiне, а выходы соединены с входами блока формирования выходного кода, о т л и ч а ю ад и и -с я тем, что/ с целью повышения точности и расширения функциональных возможностей , во вторую ступень введены дополнительные йомпараторы, ключи, блок управления ключами, блок управления и блок совпадения, выходы ко-; торого подключены к входам блока формирования выходного кода, вход управления Соединен с входом блока формирования выходного кода, а через блок управления с выходами вторых и (п - 1)- X основных и дополнительных компараторов второй ступени , информационные входы пОдключёны к выходам основных и.дополнительных компараторов второй ступени, при этом первые входа основных KOMnkраторов подключены к вторым входам дополнительных компараторов второй ступени, вторые входы основных компараторов второй ступени подключены к выходам нечетных ключей, а вторые входы дополнительных компараторов to подключены к выходам чётных ключей, аналоговые входы ключей соединены с е соответствующими выходами источника, эталонных напряжений первой ступени, управляющие вхОды ключей через блок управления ключами подключены к . выходам компараторов первой ступени, причем вход источника эталонньрс напряжений второй ступени Соеди нен с входной шияой.. Ob IsD 00 «4

СОЮЗ СОВЕТСКИХ (& ВИШНЕ

РЕСПУБЛИК

)(6Р Н 0.3 X 13/175

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ЯСУД4РОТВЕННЫЙ КОМИТЕТ СССР

6ВIShel ХВЮа ВНЮЪУ н АВТ0и:Й0мУ сбиДеп льстВУ (21) 3355562/18-21

{2г). 13.11. Е . .(46.) 15. 05. 83. 5юл. 9. 18 . (72) И.Н . Дворецкий, и.И..Ефимчик, .В.В. Лавров, О.П. Наэаров .:и А.З. Ходоровсиий (53) 681.325(088.8) (56) 1 ° Авторское свидетельство СССР

Р 226975., кл. Н 03 К .13/03; 1968.

2. Авторское свидетельство СССР

9 67709.7," кл.. Н ОЗ .К 13/03, 06.05.77. (54)(57) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗО- .

ВА1БЛЪ, состоявший иэ двух ступеней,. каждая из которых содержит компараторы .и источник: эталонных напряжений, выходы последйих подключены к первым входам компараторов соответствующей ступени, вторые входы комйараторов первой ступени подключены к входной ныне, а выходы соединены с входами блока формирования выходного кода, о т л и ч а ю щ и й.,с.я тем, что с целью повышения точности и расширенйя функциональных воэможностей,. во .вторую ступень введены до-. . полнительные компараторы, ключи, .блок управления ключами, блок управ„„SU „„. 1 018234 A ления и блок совпадения, выходы которого подключены к входам блока формирования выходного кода,. вход управления соединен с входом блока формирования выходного кода, а через блок управления с выходами вто.рых и (п - 1)- х основных и допблйительных компараторов:второй ступени, информационные входы подключе-ны к выходам основных а дополнительных компараторов второй ступени, прн этом первые входы основных компараторов подключены к вторым. входам дополнительных компараторов второй ступени, вторйе входы основных компараторов второй ступени подключены к выходам нечетных ключей, а вторые Q входы дополнительных компараторов подключены к выходам четных ключей, аналоговые входы ключей соединены с соответствующими выходами источника. эталонных напряжений. первой ступени., управляющие входы ключей череэ блок управления ключами подключены к выходам компараторов первой ступени, причем вход источника эталонных напряжений второй ступени соединен с входной шиной.

1018234

Изобретение относится к вычислительной технике и может быть использовано в информациойно-измерительных системах.

Известен асинхронный аналого-ggyровой преобразователь с поразрядным распространением сигнала, состоящий иэ ряда идентичных ступеней число которых равно числу двоичных разрядов в выходном коде преобразователя, каждая ступень содержит компаратор, подключенный одним из входов к

Входной шине преобразователя, а дру-. гим — К выходу цифро-аналогового преобразователя данкой ступени, выходы компараторов соединены с управляющими входами цифро-аналоговых преобразователей последующих ступеней преобразователя 1 J.

Недостатком этого устройства является большое время преобразова- 20 ния, определяемое временем, затрачи:ваемым на последовательное уравнове- . шивание входного сигнала всеми ступенями преобразователя, Наиболее близким к предлагаемому 25 ао технической сущности является аналого-цифровой преобразователь считывания, состоящий из ряда ступеней, каждая .из которых содержит компараторь1, количество компараторов в ли- 30 нейке определяется выбранной системой счисления и числом разрядов выходного кода, формируемых по сос- . тояниям компараторов данной ступени, один из входов каждого компаратора соединен с входной шиной преобразователя, а другой - c соответствующими выходами источника эталонных напряжений данной ступени,включенно:го между выходами двух цифроаналоговых преобразователей, управляемых

1 выходными сигналами компараторов предшествукицих ступеней, выходы ком,параторов подключены также к входам Кедоэого РегистРа, последовательно 45 соединенного с блоком накопления и отображения данных. Сокращение вре меии преобразования в этом устройстве. достигается за счет использования нескольких компараторов в каждой ступени 1.2g. 50

Недостатками известного преобразователя являются низкая точность преобразевания обусловленная наличием в характеристиках реальных ком-. параторов зоны неопределенности, внутри ко.орой компараторы с некоторой вероятностью могут находиться как в единичном, так и в нулевом состояниях и невозможность использова- 60 ния преобразователя в следящем режиме ..

Целью изобретения является повышение точности преобраэования и рас-, ширение функциональньх воэможностей. g5

Поставленная цель достигается тем, что в аналого-цифровой преобразователь, состоящий из двух ступеней, каждая из которых содержит компараторы и источник эталонных напряжений,,выходы последних подключены к первым входам компараторов соответствующей .ступени, вторые входы компараторов первой ступени подключены к входной шине, а выходы соединены с входами блока формирования выходкого кода, во вторую ступень введены дополнительные компараторы, ключи, блок управления ключами, блок управления и блок совпадения, выходы которого подключены к входам блока формирования выходного кода, вход управления соединен с входом блока формирования выходного кода, а через блок управления " с выходами вторых и (п — 1) — х основных и дополнительных компараторов второй ступени, информационные входы подключены к выходам основных и дополнительных компараторов второй ступени, при этом первые входы основных компараторов соответственно подключены к вторым входам дополнительных компараторов второй ступени, вторые входы основных компараторов второй ступени подключены к выходам нечетных ключей, а вторые входы дополнительных компара-. торов подключены к выходам четных ключей, аналоговые входы ключей соединены с соответствующими выходами источника эталонных напряжений первой ступени, управляющие входы клю! чей через блок управления ключами подключены к выходам компараторов первой ступени, .причем вход источ-! ника эталонных напряжений второй ступени соединен с входной шиной.

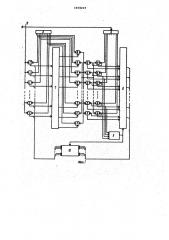

На фиг. 1 представлена функциональная схема предлагаемого аналогоцифрового преобразователя; на фиг.2функциональная схема управления ключами; на. фиг. 3 — функциональная схема блока управления и блока совпадения; на фиг. 4 — диаграмма эталонных напряжений, формируемых в процессе работы преобразователя.

Аналого-цифровой преобразователь (фиг. 1) содержит компараторы 1 и источник 2 эталонных напряжений первой ступени, основные компараторы 3, дополнительные компараторы 4, источник 5 эталонных напряжений второй ступени, ключи б, блок 7 управления ключами, блок 8 совпадения, блок 9 управления.

Устройство работает следующим образом.

При подаче входного сигнала на входную шину 11 компараторы первой

1018234 ступени изменяют свое состояние в соответствии с выражением:

1, при х(t) ор х

j о, при x(t) (х где а выход (-ro .компаратора.

Одйовременно. эталонные напряжения на вторых входах компараторов второй ступени образуют равномерную шкалу, середина которой совпадает с входным сигналом. По состояниям компараторов первой ступени блок 7 управления ключами с помощью ключей б подключагт к первым входам основных и дополнительных компараторов второй ступени два соседних эталонных напряжения шкалы первой ступе- (5 ни, ограничивающих участок диапазона, внутри которого находится .входной сигнал. При этом к первым входам основных компараторов второй ступени подключается эталонное напряжение, равное минимальному входному сигна,лу х., если 6. = 1, или эталонное напряжение, равное максимальному входному сигналу х, если a „ „=1, во всех остальных случаях, когда 25 входной сигнал попадает между двумя соседними эталонными напряжениями нечетных компараторов первой ступе(а>„

2к к первым входам дополнительных компараторов второй ступени подключается эталонное напряжение х при

ag = 1 р или х, при 6 n> = 1 или р,г ПРи О 2х-2 R Я . Блок 9 управления элементами совпадения производит выбор линейки

0 компараторов второй ступени, по сос- 4О тояниям компараторов которой формируются младшие разряды выходного кода. -Формирование младших разрядов производится по состояниям основных компараторов, если эталонное напряжение поданное на первые входы ком- 45 параторов этой линейки оказывается между напряжениями, поданньвеи на вторые входы второго и (2" -1)-го

1l а компараторов этой линейки щ о о

В остальных случаях в формировании выходного кода участвует линейка дополнительных компараторов. Для устранения неопределенности в выборе компараторов в случае попадания входного сигнала в зону неопределеннос-. ти одного иэ компараторов первой ступени блок 9 управления элементами совпадения выполняется в виде двух трехвходовых элементов И с двумя запрещающими входами .(фиг. 3). Выходные данные преобразователя представляются в коде Грея. Формирование старших разрядов выходного кода блоком 10 производится непосредственно по состояниям компараторов первой ступени,. а формирование младших разрядов выходного кода производится по состояниям линейки компараторов второй ступени, подключенных в данный момент к входам блока 10 .в соответствии с сигналом бл6ка 9 . !

После получения выходного кода преобразователь автоматически переводится в следящий режим работы. При этом в каждый момент времени непос . редственное участие в процессе преобразования принимает лишь одна иэ двух линеек (основная или дополнительная) компараторов второй ступени.

Вторая в это же время следит эа изменением входного сигнала путем подключения соответствующих эталонных напряжений к первым входам компараторов этой линейки.

Таким образом, в предложенном преобразователе исключаются ошибки при считывании информации и обеспечивается воэможность преобразования в следящем режиме.

1018234

1018234 г" -га ключа (8" -I)- zn клю ,fZлi Р) tp ключу

Е-го ключа @и

1-га ключа к уараРлвожии дидам (Г л -1) -го клюю

1018234

Ф

Х -М

Составитель Л. Беляева

Техред Ж. Кастелевич Корректор Е- Рококо

Редактор А. Химчук

Заказ 3560/53

Филиал ППП Патент ., г. Ужгород, ул. Проектная, 4 l

t

I

1

Qt Хф

Ьф

XE4I &УД1 » 4 .(ф

Щю/

f) Тираж 936 Подписное

BHHHIIH Государственного комИтета СССР по делам изобретений и открытий

ll3035, Москва, Ж-35, Раушская наб., д. 4/5

I

1 .!

f