Цифровой кодирующий преобразователь

Иллюстрации

Показать всеРеферат

9351 А

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И)

y g 6 01 В 23/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ -::=:::::::.-;==:.: 1.

H ABT0PGHOMV СВИДЕТЕЛЬСТВУ (21) 3383250/18-21 (22) 21.01.82 (46) 23.05 83. Бюл И 19 (72) В.Э.Штейнберг и Ю.Л.Востряков. (53) 621 317(088.8} (56) 1. Авторское свидетельство СССР

N 525031, кл. С 01.R 23/00, 1976.

2. Авторское свидетельство СССР

И 573766, кл. С 01 К 23/02, 1977 (прототип) . (54)(57) ЦИФРОВОЙ КОДИРУЮЩИЙ ПРЕОБРАЗОВАТЕЯЬ, содержащий последовательно соединенные блок пуска, вентиль, делител,шага квантования, элемент задержки, счетчик шага квантования, основной регистр, первый управляемый делитель и основной вычитающий счетчик, генератор опорной частоты, второй управляемый делитель, первый формирователь, а также последовательно соединенные второй формирователь, триггер, элемент И и счетчик, второй вход которого соединен с вторым входом триггера и выходом первого формирователя, второй вход элемента И подключен к выходу вентиля и входу второго управляемого делителя, выход которого соединен с вторым входом первого управляемого делителя, выход делителя шага квантования подключен к второму входу основного регистра, первый вход которого соединен с вторым входом второго управляемого делителя, о т л и ч а ю. шийся тем, что, с целью расширения функциональных возможностей, в него введены последовательно соединенные дополнительный регистр, двоичный умножитель и дополнительный вычитающий счетчик, а также сумматор кодов, вход которого соединен с выходом элемента И, выход сумматора кодов подключен к второму входу дополнительного счетчика, третий вход которого соединен с выходом второго формирователя и первым входом дополнительного регистра,- второй вход последнего подключен к выходу счетчика, при этом второй вход двоичного умножителя соединен с выходом первого управляемого делителя.

1019391

Изобретение относится к электроизмерительной технике.

Известно устройство для измерения частоты и сдвига фаз, содержащее цифровой частотомер, управляемый делитель, ключи, схему умножения, делитель с дробными коэффициентами деления(1 j.

Недостатком устройства являются ограниченные функциональные возмож- !О ности, так как оно функционирует в два такта и требует измерения вспомогательной частоты, пропорциональной измеряемому параметру в эталонном интервале времени. 15

Наиболее близким к изобретению является устройство для измерения частоты повторения импульсов, содержащее генератор опорной частоты „ формирог ватель, делители, элемент задержки, 20 счетчик, регистр хранения и вычитающий счетчик. Устройство обладает вы" соким быстродействием, так как обеспечивает кодирующее преобразование практически за время поступления одно-25 го или нескольких периодов $2) .

Недостатком устройства является невозможность определения сдвига фаз, что существенно ограничивает либо область использования устройства, либо эффективность использования оборудования.

Цель изобретения " расширение функциональных возможностей устройства одновременное определение частоты и сдвига фазы.

Поставленная цель достигается тем, что в.цифровой кодирующий преобразователь, содержащий последовательно соединенные блок пуска, вентиль, делитель шага квантования, элемент задержки, счетчик шага квантования, основной регистр, первый управляемый делитель и основной вычитающий счетчик„ генератор опорной частоты, вто45 рой управляемый делитель, первый форми ро вател ь, а .та кже последовател ьно соединенные второй формирователь, триггер, элемент И и счетчик, второй вход которого. соединен с вторым входом триггера и выходом первого формирователя, второй вход элемента И подключен к выходу вентиля и входу второго. управляемого делителя, выход которого соединен с вторым входом первого управляемого делителя, выход .делителя шага квантования подключен к второму входу основного регистра, первый вход которого соединен с вторым входом второго управляемого делителя, введены последовательно соединенные дополнительный регистр, двоичный умножитель и дополнительный вычитающий счетчик, а также сумматор кодов, вход которого соединен с выходом элемента И, выход сумматора кодов подключен к второму входу дополнительного счетчика, третий вход которого соединен с выходом второго формирователя и первым входом дополнительного регистра, второй вход последнего подключен к выходу счетчика, при этом второй вход двоичного умножителя соединен с выходом первого управляемого делителя.

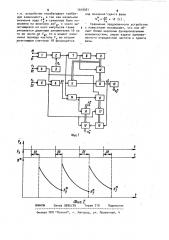

На фиг.1 приведена структурная схема устройства, на фиг.2 - диаграмма его работы.

Устройство содержит блок 1 пуска, вентиль 2, генератор 3 опорной частоты, первый формирователь 4, второй формирователь 5, триггер 6, делитель

7 шага квантования, элемент 8 задержки, счетчик 9 шага квантования, регистр 10, управляемые делители 11 и

12, вычитающий счетчик 13, элемент И 14, счетчик 15, сумматор 16 кодов, регистр

17, вычитающий счетчик 18, двоичный ум" ножитель 19, шину 20 пуска, шину 21 останова, шину 22 эталонной частоты и шину 23 входной частоты.

На диаграмме (фиг.2) приведены сигналы эталонной частоты F входной частоты Г„ и изменение кода и в вычитающем счетчике 13.

Процесс кодирующего преобразования входной информации в код сдвига фазы организуется с помощью следующего алгоритма функционирования. 8 течение временного сдвига д между периодами

;уалонного сигнала F > и контролируемой частоты F (фиг.2) производится квантование ийтервала дй импульсами опорной частоты Г, число которых подсчитывается в счетчике 15 (фиг.1).

Одновременно осуществляется формиро"., вание вспомогательной величины (at-F0 F ) путем суммирования значения F в сумматоре 16 кодов (Dt FJ раз и затем переписывается данный код в начале каждого периода контролируемой частоты F во второй вычитающий счетчик. Затем в интервале времени периода контролируемой частоты Г, осуществляется определение отношения

М/Тх, представляющего собой исходную величину сдвига фазы, путем нелинейного кодирования Тх импульсами убываю3 1019

v щеи по величине частоты, которые вычитаются из- числа (дй F0 F,)» во втором вычитаащем счетчике 18. Данная операция поясняется зависимостью

at

9 Д= — =at F -gt F (F - И ) (1)

=T< х о где N - число импульсов, прошедшее в течение периода Т с выхо да второго управляемого делителя 12 на двоичный умножи10 тель 19, причем

"г Й6т) где д и - величина шага квантования,, I

15 формируемая делителем 7; и и (n-1j -коэффициенты деления управляемых делителей 11 и 12 соответственно.

В формуле (1) первый член зависимости формируется -в интервале времени квантования промежутка дГ, а второй член, одновременно с выполняемой операцией вычитания, - в интервале пе риода Т„ следующим образом. С помощью делителя 7 осуществляется отсчет .ш гаьй квантования временного аргумен-!.25 мента нелинейной функции, описывающей процесс изменения формируемых им-. пульсов, а в счетчике 9 подсчитывается число и шагов. С помощью управляемых делителей 11 и 12 осуществляется формирование импульсов с убывающей частотой путем деления опорной частотй Р. на коэффициенты и и {n-1),коды которых подаются с выходов счетчика 9 и регистра 10 хранения. Число импуль- 5 сов, поступившее с выхода управляемого делителя 12, умножается в двоичном умножителе 19 на код {ай ° F )+, „0 которыи записывается во второй регистр 17 хранения из счетчика 15 в 40 момент окончания интервала Ю . Импульсы, поступающие с выхода двоичного умножителя 19, подаются на второй вычитающий счетчик 18. Одновременно импульсы с выхода управляемого дели- 45 теля 12 поступают на первый вычитающий счетчик 13. Таким образом в момент окончания периода Т в первом

Х вычитающем счетчике 13 фиксируется цифровой код и контролируемой час- .50 тоты, а во втором вычитающем сметчике 18 фиксируется цифровой код N< сдвига фазы, т.е. результат код рующего преобрззования.

С учетом изложенного устройство работает следующим образом.

На шины 22 и 23 устройства подаютая соответственно эталонная F и

351 4 контролиРУемая F частоты (фиг.2) С началом периода частоты F с .выхода э первого формирователя 4 поступает импульс на установочный вход счетчика 15 и на первый вход триггера 6.

По команде "Пуск" с шины 20 блок 1 пуска разрешает прохождение импульсов генератора 3 опорной частоты через вентиль 2 на делитель 7 шага квантования, первый управляемый делитель 11 и элемент И 14. При .наличии разрешающего- сигнала с триггера 6 в течение времени at элемент И 14 пропус" кает импульсы опорной частоты F на счетчик 15, где Фиксируется код

О 3 (at Г, ) -, и на разрешающий вход сумматора 16 кодов, в результате чего код значения частоты F+ с каждым имэ пульсом суммируется (ht F ) раз в

О сумматоре 16. С началом периода час" тоты Гх с выхода второго формирователя 5 поступает импульс, который устанавливает в исходное состояние делитель..7 шага квантования, счетчик

9 шага квантования, управляемые делители 11 и 12, первый вычитающий счетчик {все эти связи на схеме не показаны), записывает во второй регистр 17 хранения число из счетчика 15, а также поступает на установоч" ный вход второго вычитающего счетчика 18, записывает в него код { и F F ) из сумматора 16 кодов. о э

Так как для нелинеййЬго кодирования периода требуется воспроизве- дение гиперболического закона изменения кода в сумматоре 16, а устрой" ство, в силу структуры, реализует полигональную аппроксимацию данного закона, то на каждом из участков аппроксимации должны обеспечиваться угловые . коэффициенты, соответствующие гиперболической функции, а именно д1 1;г; (2)

Так как каждое из приращений dNg

Ят формируется путем деления числа дй F

9 импульсов на коэффициенты и и {и-1) с помощью делителей 11 и 12, то К у, равно к= м и и-1дс Fo

С другой стороны, применяя разност-, ный оператор к гиперболической функции, получим

ap)= „-()-s„„(t)= — „,„- 1

Фиг.1

Фиг. Г

ВНИИПИ Заказ 3695/39 Тираж 710 Подписное филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

5 10 т.е. устройство отрабатывает требуемую зависимость, а так как начальное значение кода F+ в сумматоре было поэ множено на величину htF и число вы.читающихся из него импульсов также умножается двоичным умножителем 19 на то же число дй Г, то в момент окончания периода частоты F во втором вычитающем счетчике 18 фиксируется

19351 6 код значения сдвига фазы и = — " -y()

Х

Сравнение предложенного устройства с известными показывает, что оно облает более широкими функциональными возможностями, решая задачу одновременного определения частоты и сдвига фазы.