Устройство для вывода информации

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

3(S9 G 06 F 3 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

AO ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPbITHA

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (.21) 3304724/18-24 (22) 22.06.81 (46) 23.05.83. Бюл. В 19 (72) В.М. Балыбин, Б.С. Егоров, й.A. Козлов и Ю.В. Незнамов .(53) 681.327.11(088.8) .(56) 1. Авторское свидетельство СССР

9 507865, кл. G 06 F 3/00, 1974 (поототип). .(54)(57) 1. УСТРОЙСТВО ДЛЯ ВЫВОДА

ИНФОРМАЦИИ, содержащее каналы связи, выходы которых являются выходами устройства, .и последовательно соединенные формирователь импульсов и блок

SU„„A памяти, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности и упрощения устройства, оно содержит коммутатор, один вход которого является первым входом устройства, а входы группы соединены с выходами распределителя импульсов и входами блока памяти, один иэ входов которого является вторым входом устройства, выходы блока памяти и коммутатора соединены с соответствукщими входами каждого из каналов связи, а вход распределителя импульсов является треть. им входом устройства.

1О19424

2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что каждый иэ каналов связи содержит поляризованные и первое и второе управляющее реле, диоды и параллельно соединенные резистор и конденсатор, вход обмотки питания одного управлякйцего реле является первым входом канала связи, вход обмотки питания другого управляющего реле соединен с одними выводами параллельно соединенных резистора и конденсатора, другие выводы которых являются вторым входом канала связи, выходы обмоток питания первого и второго управляющих реле соединены с шиной, нулевого потенциала, входы первых обмоток питания

Изобретение относится к вычислительной технике, в частности к устройствам обмена, и может быть использовано при построении систем авто матического управления. 5

Известно устройство для вывода информации, содержащее каналы связи, выходы которых являются выходами уст ройства, и последовательно соединенные формирователь импульсов и блок памяти (1).

Недостатками этого устройства являются его сложность и низкая надеж.ность, Цель изобретения — повьпаение надежности и упрощение устройства.

Цель достигается тем, что в устройство, содержащее каналы связи, выходы которых являются выходами устройства, и последовательно соединенные формирователь импульсов и блок памяти, введены коммутатор, один вход, которого является первым входом устройства, а входы группы соединены с выходами распределителя импульсов, и входами блока памяти, один из входов которого является вторым входом, устройства, выходы блока памяти и коммутатора соединены с соответствующими входами каждого иэ каналов связи„ а вход распределителя импульсов яв- ЗО ляется третьим входом устройства..

Кроме того, каждый из каналов связи содержит поляризованные и первое и второе управлякяцие реле, диоды и параллельно соединенные ре- 35 эистор и конденсатор, вход обмотки питания одного управляющего реле является первым входом канала связи, вход обмотки питания другого управля . ющего реле соединен с одними вывода- щ ми параллельно соединенных резистора поляризованных реле соединены .с одним из выводов первого управляющего реле, другой вывод которого соединен с шиной нулевого потенциала, выходы первых обмоток питания поляризованных реле соединены с шиной положительного потенциала, входы вторых обмоток питания поляризованных реле соединены с одними выводами диодов, другие выводы которых являются входами группы канала связи, выходы вторых обмоток питания поляризованных реле соединены с одним из выводов второго управляющего реле, другой вывод которого соединен с . одним из выводов . первого управляющего реле.

2 и конденсатора, другие выводы которых . являются вторым входом канала связи, выходы обмоток питания первого и второго управляющих реле соединены с шиной нулевого потенциала, входы первых обмоток питания поляризованных реле соединены с одним из выводов первого управляющего реле, другой вывод которого соединен с шиной нулевого потенциала, выходы первых обмоток питания поляризованных реле соединены с шиной положительного потенциала, входы вторых обмоток питания поляризованных реле соединены с .одними выводами диодов, другие выводы которых являются входами груп. пы канала связи, выходы вторых обмоток питания поляризованных реле соединены с одним из выводов второго управляющего реле, другой вывод которого соединен с одним из выводов первого управляющего реле.

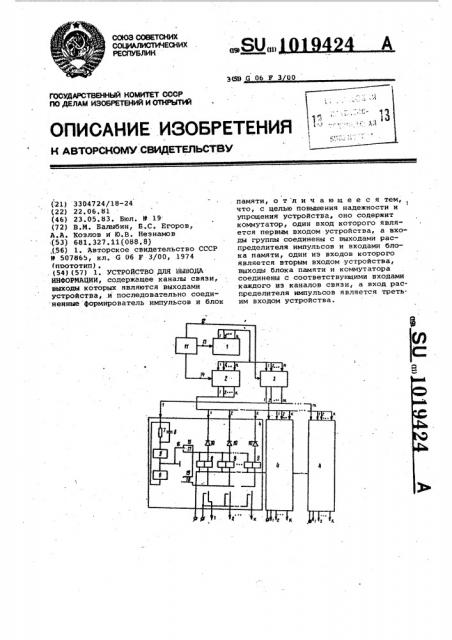

На чертеже приведена схема предлагаемого устройства.

Устройство содержит распределитель 1 импульсов, выходы которого подключены к соответствующим входам блока 2 памяти и коммутатора 3,.и каналы 4 связи. Каждый канал связи содержит управляющие реле 5 и б, резистор 7 и конденсатор 8, а также поляризованные реле 9 по числу разрядов выводимого кода, входы которых через диоды 10 подключены к соответ ствующим выходам блока 2 памяти, Выходы коммутатора 3 подключены к входам обмоток питания управляющих реле соответствующего канала. Выходы обмоток питания этих реле подключены к корпусу источника питания.

Управляющие входы распределителя 1, коммутатора 3 и информационный вход 1019424

Составитель В. Верховский

Техред И.Гайду Корректор Г. Решетник

Редактор A. Козориэ

Заказ 3704/42 1ираж 706 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 блока 2 памяти подключены к формирователю Il импульсов через входные шины 12-14 и контакты 15-19 реле.

Устройство работает следующим об разом.

Подлежащие выводу из формирователя 5

ll коды по шине 14 переписываются по соответствующим адресам блока 2 памяти. После этого сигналом, поступающим по шине 13, запускается распределитель 1 импульсов. Первый выход- 10 ной импульс распределителя считывает информацию, записанную по первому адресу блока 2 памяти, и одновременно поступает на первый вход xOIe4yтатора 3. Считанный иэ блока памяти 15 код в виде импульсов тока поступает. через диоды 10 на входы поляризованных реле всех каналов 4 связи. Диоды необходимы для развязки обмоток реле одноименных разрядов всех каналов.

Коьз4утатор 3 позволяет подключать любой иэ и выходов распределителя на любой иэ In выходов коммутатора(где.

Inm) и тем самым переслать информацию записанную по любому адресу блока 2 памяти,. в любой канал связи. Это по- зволяет, в свою очередь, иметь резервные объекты управления и посредством коьеиутатора 3 оперативно подключать их к соответствующим адресам блока памяти взамен вышедших из строя что повышает надежность устройства.

Импульс с выхода коммутатора поступает на обмотки питания реле 5 и 6 соответствующего канала. При этом замыкаются контакты 16 и 17 реле 5 и контакты 19 и 18 реле 6; Через первые обмотки питания поляризованных реле начинает протекать ток по цепи: клемма источника питания, обмотка реле, замкнутые контакты 16 и 17 ре- 40 ле 5, корпус источника питания, и происходит размыкание контактов всех поляризованных реле 9. Вторые обмотки реле 9 в это время обесточены, так как контакты 15 и 16 реле 5 разомкнуты, Величина емкости конденсатора 8 выбрана таким образм, чтобы его заряд происходил в течение первой половины длительности импульса на выходе коммутатора. По окончании заряда конденсатора 8 реле 5 обесточивается, его контакты 16 и 17 развыкаются, а контакты 16 и 15 замыкаются.

Резистор 7 служит для разряда конденсатора, ток; протеканщий через aего, недостаточен для срабатывания реле 5.

При этом виходЫ первых обмоток ре пе 9 отключаются от общей шины (корпуса) источника питания, а выходы вторых обмоток этих реле подключаются,. к ней через замкнутые контакты 19 и

18 реле 6 и контакты 16 и 15 реле 5.

Через обмотки питания реле 9, на которые поступают импульсы с соответствующих выходов блока. 2 памяти через диоды 10,начинает протекать ток.

При этом замыкаются контакты соответствующих реле 9, и считанная из блока памяти информации поступает на объект управления. По окончании действия импульса с выхода коммутатора

3 обесточивается реле 6 и разьыкает контакты 19 и 18. После этого обмотки питания всех реле данного канала

4 связи обесточены. Второй выходной импульс распределителя 1 считывает информацию, записанную по второму ад, ресу блока памяти, и посредством коммутатора 3 выдает ее в другой канал 4 связи и т.д.