Устройство для вычисления зависимости @ = @ + @ + @

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДНЯ 8ШИСЛ НИЯ зАв«стобти у -у)ф.х|+х ч ji, содержащее ахоэ«: cs ittiaTop, о т л и ч а ю ai е ес л те, что, с и«лыо повыишния быст|хэдв теия, в него введены h-t бгкжое И, где ft - разрядность юессдашого значения, (п-1) мно- roexof|(rei«x сумматоров и п дешифратрро&-шйф:1аторов , причем -ый блок элем той . ,..,, п-1, содершт t групп элементов И, выходы j-erfi групры f-ro втока, j-t,2,...,f, элементов И соединены с j-bw входом }-го нжм-овходового сумматора, (+1)-ый вход которого coeflvmeH с первым выходом tто дешифратора-шифратора, первый вход которого соединен с выходом f-fX) многовходового сумматора, BiitxoA k-ro многовходового сумматора, kpl, 2,...,п«2, соединен с (Ы-З)-ым входе ()-ro многовхпдового сумматора , выход «тереноса k-ro многовходового сумматора соединен с вторым входом () -го дешифратора-и «|)ратеч в, третий вход (второго соединен с вторым выходом k-ro дешифратора-шифратора, вход 1-го разряда, ,2,...,й-1, устройства соединен с йервшш $хода ми элементр и Й-ой группы каедого блока, вторые входа, элементов И Е-го блока соединены с входом (Е+1)-гс разряда устройства, первый и второй входы входного сумматора соединены; соответственно с входом /первого разряда устройства и входом нуля устроиства, выход входного сумматора соединен с третьим входом первого многовходового сумматора, выход переноса входного сумматора соединен с вторым входом первого дешифратора-шифратора, выход переноса (л-1)-го многоВходо вого сумматора соединен с первым входом пго дешифратора-шифратора, второй 1вход которого соединен с вторым выходом (п-1)-го дешифратора-шифратора .

1019446

Изобретение относится к вычислительной технике и может быть применено в качестве спецпроцессора е комплексе с цифровой вычислительной машиной или в специализированных вы" числительных устройствах для оперативного вычисления корня квардратного из суммы квадратов трех чисел.

Известно устройство для вычисления функции, содержащее регистр первого операнда, счетчик второго операнда, два счетчика порядка, блок управления и дешифратор, входы которого подключены к разрядным входам первого счетчика порядка, а выходк разрядным входам счетчика второго операнда, выход переполнения которого подключен к входу первого счетчика порядка 1 j .

Недостатками этого устройства является ограниченные функциональные возможности из-за того, что в уст5

20 ройстве вычисляется корень квадратный только двух чисел, и относительно низкое быстродействие, определяемое тем, что s устройстве организован последовательный вычислительный процесс на основе число-импульсного представления операндов.

Наиболее близким .по технической ЗО сущности к предлагаемому является устройство, содержащее регистры первого и второго операндов >сумматор, регистр сдвига, группы элементов И, ИЛМ и распределитель импульсов, выходы которого с первого по восьмой подключены соответственно к входу обнуления сумматора, к «упрввляющйм, входам элементов И первой и второй групп сумматоров, элементов И третьей 40 гРуппы регистру сдвига и-элементов

И четвертой и пятой групп 2 .! .

Недостатком известного устройства яаляются ограниченные функциональные

Возможности Определяемые тем что B 45 устройстве. вычисляется корень квадратный суммы только двух операндов, и низкое быстродействие благодаря последовательной организации вычислительного процесса..

Цель изобретения - повышение быстродействия.

Поставленная цель достигается тем, что в устройство для вычисления за55 висимости y = содержащее входной сумматор дополнительно введены и-1 блоков элементов И, где и - разрядность выходного значения, (и-1) многовходовых сумматоров и и дешифраторов-шифраторов, причем I-ый блок элементов И, 1-1,2,...,n-l, содержит групп элементов И, выходы

j-ой группы I-ro блока, j 1,2,...,I элементов И соединены с j-ым входом

1-го многоаходового сумматора, {i+1)-ый вход которого соединен с первым выходом I-го дешифратора"шифратора, первый вход которого соединен. с выходом I-го многовходового сумматора, выход k-го многовходового сумматора, k 1,2,...,n-2, соединен с (k+3)-ым входом (k+1)-ro многовходового сумматора, выход переноса

k-го многоаходового сумматора соедйнен с вторым входом (k+1)-ro де- . шифратора-шифратора, третий вход которого соединен с вторым выходом

k-го дешифратора-шифратора, вход

Ьго разряда, 11,2,...,n-I, устройства соединен с первыми входами элементов И g-ой группы каждого блока, вторые входы элементов И Е-го блока соединены с входом (2+1)-го разряда устройства, первый и второй входы входного сумматора соединены соответственно с входом первого разряда устройства и входом нуля устройства, выход входного сумматора соедииеи с третьим входом первого многовходового сумматора, выход переноса входного сумматора соединен с вторым входом пеpsono дешифратора-шифратора, выход переноса (n-!)-ro многовходового сумматора соединен с первым входом n-ro дешифратора-шифратора, второй вход которого соединен с вторым. выходом (n-1)-го дешифратора-шифратора.

На фиг.! показана блок"схема предлагаемого устройства (для случая

n=5); íà фиг.2 - функциональная схема устройства; на Фиг.3- - элементы сумматора; на фиг.6 - группа элементов И; на Фиг.7 - Функциональная схема дешифратора-шифратора.

Устройство для вычисления заеисимости у=

i з содержит входной

Li сумматор, блоки элементов И, состоящие из групп 2, многоаходовые сумматоры 3, дешмфраторы-шиФраторы 4,которые выполнены на однотипных логических элементах 5, группы элементов И 2 в виде групп.б, входы 7-9 и выход 10.

Сумматоры 1 и 3 выполнены как сумматоры-вычитатели, причем сумматор-вычитатель 1 выполнен, например, в виде однотипного двухразрядного сумЭ 101944 жатора-вычитателя 11, а каждый (Р)-ыйЬ1,2... „и многовходовый сумматор 3 т выполнен, например, из последователь- р ио соединенных одноразрядного сумма- фо тора-вычитателя 12 старшего разряда, -

М одноразрядных сумматоров-вычитатеей 13 последующих разрядов и одно-. ипного двухразрядного сумматоравычитателя 11, подключенного своим выходом переноса к входу переноса щ (2+1)-го одноразрядного сумматора- . вычитателя 13. Группы элементов И 6. выполнены, например, в виде- матрицы, каждый k-ый столбец которой (Ь 1,.

2,...,п-1} содержит tc. групп элемен- ц тов И.

На фиг.3 представлен первый разряд каждого (5-го сумматора-вычитателя, выполненного, например, в виде двух одноразрядных сумматоров М, двух элементов ИЛИ 15, двух элементов

И 16 и сумматора 17 по модулю два.

На фиг.4 представлен i-ый разряд

R-.ãî сумматора 3, выполненный, например» в виде двух ОдиОразрядных сумма уз торов 18, двух элементов ИЛИ 19, четырех элементов И 20 и сумматора 21 по модулю два.

На фиг.5 представлен однотипный двухразрядный сумматор-вычитатель 11, выполненный, напримев, в виде одноразрядного сумматора 22 на три входа, подключенного своим выходом и выходам переноса к первым входам последовательно соединвйных первого и второго.одноразрядных сумматоров 23.

Каждая группа. элементов И 6 (фиг.6) выполнена, например, в виде трех двухвжщовых элементов И 24,,каждый; однотигюый логический элемент g (фиг.7} - в виде .четырех элементов O х„=.г 5

ХЗХ1 +

13

"э"з

Z 22 Э :14. 2 2 Э 1 4 2т-зги х +хг ф 1х1 + х2+х2х +х х хЭ з 3 3 Э

-g-kaL-И 0 .

1 Г 2 1 12 х„+ х„х„+ х + х х2

6 ф

И 2, трех элементов ИЛИ 26, суммаора 27 по модулю два и полусумматоа 28. Цифрами, расположенными у инрмационных входов блоков, обозначены соответственно входы (цифры без скобок) и выходы (цифры в скобках) .

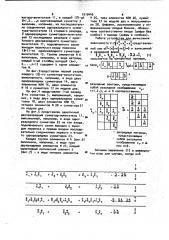

Работа устрой вычисления. зависимости м = представленэ ой как аР(х +х2+х2)О и записаннои

1 2 Э в разрядной формеЙ М + М М + Щ -3 et<; (t) поясйяется на конкретной. примере, Разрядные векторы, предстааляющие собой разрядное изображение х ., г1,2,3, et. и 0 соответственно;

- разрядные матрицы, И представляющие собой разрядное изображение х и d, при w3.

Запишем выражение (1} в разверну © том виде для случая, когда я4

101 446 э 4

42+х2Х2,8

4 4 х> а х2 +

Обозначим в выражении (2) векто(1) ры Х =(О Дк

1 15 ч(2) 1z 2 t б(ъ) . 13 33 3 хх д x; x = хх хх Ох г 1 г

) 12 22 е-1е О х .-(1) О 1(.

Х = хХ хх ... Х Х Х Ы

d,(2) А Ь {3) А и й 1 Ф ч(Р) 1 г Е Е=1

Каждый К-ый разряд et, (Ь 1,2...,n) искомого вектора eL определяется по выражению: е 1

t 30 где f - значение переноса иэ старше", го разряда вектора Рв), определяемого на основании выражения ч(1) .чИ) У И) 11) (1) хчЮ= "х И) + g 2>+ "х() +"„(2) 2уо) чх(3) = М(2)в+2-9(чхй) +МИ) +чхО)) (ЕЙ (1)(4)

2 3 ч(ву ч(Е4) 2-(Е-а()((Е)+ 1Е)+)(СЕ)) ч1е),1Е-Е)

1 2 3 40 (2,3,...,n.

C" величина, принимающая значения

Фф) () 2-! е) 1Е-" .1 (g)

Вж - «2(Ю"ри у{е-1).0, р.2, 45

3 ф ° ° ° ° n °

При реализации вычислений в соответствии с выражениями (3-5) возможен также один из двух случаев.

C л у ч а и 1. Если при Р-ой реали.30 зации выражения (4) окажется,.что .) =О, а при последующей реализации е выражения (4) (т.е. Ъ В+1) значение переноса из старшего разряда вектора фЬ1)ч (е),, -(Е-)) (Ч)Р11.„1Е+1)+ч(Е1 ) ) х„ авно единице, то принимается, что 1, и вычислительный процесс продолжается аналогично (3-5).

6 х 3+"3" 3

3 Э 4 Э 3 4

С л у ч а и 2. Если в результате

В"го вычисления по выражениею (4) 1, а при последующем (7+1)-ом вые числении по выражению (4) вектор дЕ+1). ge) +2-(e-1)(ч{Е ),лц 2)+

УЕ "> > 12 ч (Е 1) ай-1)), (6) то далее выражение „(4) реализуется с удвоенным вектором oL1 1 значение считается равным нулю, а к значению

a(=) добавляется еще единица. Критерием выполнения первого случая при

В-ой реализации выражения (4) является Q 0, а значение переноса из е старшего разряда вектора 3(Е+ ") должно быть равно единице. В основу критерия выполнения второго случая при (0+1) -ой реализации выражения (3} положено следующее: К 1, а также любой старший разряд (начиная с первого) равен единице (m),2,..., е) при равенстве единице m-го разряда вектора 1(Е+").

Работа устройства для случая п 5 происходит следующим образом.

При подаче íà перауе 7, вторую 8 ! и третью 9 входные шины значений разе е е, ч рядов х,,х2 и х . векторов Х1, Х2 и

1 Ф после окончания переходного процесса в устройстве на выходе входного сумматора 1 по выраженйю (Я I Ф. ()1 образуется вектор х, который поступает на сумматор 3, а на выходе переноса сумматора 1 по выражению (3) образуется значение старшего разряда oL искомого вектора oL, которое поступает через дешифратор-шифратор 4 на выход старшего разряда.

Далее на вход первого сумматора 3 в . ф2) vx(2) х(2)

v(Ь 0 и 0), в котором по выражению (4) образуется вектор х, а на выходе переноса старшего его разряданулевой или единичный сигнал, который мость у= определяется

7 10 через второй дешифратор 4 поступает на второй выходной разряд. Аналогично на входы второго, третьего и четвертого сумматоров 3 поступают соответственно векторы чщ ч(Ъ) ч(31 )г(31 ф(31(1((3}t ч(4) х1 ° 3 X ™1ф ч(4) "(4} (4) (Z) ч(41 ч(5} ч (5) х ° х э е Я 1 х 1 х .1 1 х

3((51 ф (5) g(3)

При этом в соответствии с выражениями (3-5) на выходах переносов старших разрядов второго, третьего и, четвертого сумматоров и, соответственно, на третьем, четвертом и пятом разрядах выходной шины образуются последующие значения aL, Й, gL искомого вектора Ф .

Использование новых элементов (n-1} однотипных логических элементов и и сумматоров-вычитателей, а также новых связей между ними, выгодно отличает предлагаемое устройство от известного, так как в предлагаемом устройстве существенно расширены функциональные возможности. 8 извест(g1)}16 8 ном устройстве вычисляется только корень квадратный из суммы двух чисел, в предлагаемом " корень квадратный суммы квадратов трех чисел.

Кроме того, в предлагаемом устроистве существенно увеличено быстродействие в отличие от известного, в ко" тором вычислительный процесс организован в виде последовательности шагов.

16 В ПРЕДЛаГаЕМОМ УстРойстве ЗавиСИза время переходного процесса 8 схе1$ ме благодаря тому, что устройство является комбинационным, т.е. практически за один такт.

Предлагаемое устройство может применяться в вычислительных систеz() мах, реализующих вычислительный про. цесс в натуральном масштабе времени, например управление технологическими процессами или динамическими объектами в режиме их нормального функр ционирования.

10)944б

1019446

Составитель А.Зорин

Редактор А.Козориз Техред О.Неце корректор В.Гирняк

Заказ 3705/43 Тираж 706 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 13035, Иосква, 3-35, Рауаская наб., д. 4/5 ееюв велчев филиал ППП "Патент", r. Ужгород, ул. Проектная, 4