Устройство для определения четности информации

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ОПРЕДБЛЕНИЯ ЧЕТНОСТИ ИНФОРМАЦИИ, соафжащбе рвпкпгр, nefmiift в второй аа мёпггЫ ИЛИ, первый я вторс Г1штЕрь1, j группу апементов И группу ИЛИ, пртпсм еяявтш е входы хая цого рваряоа релкяра об|равуюг грушу вхоаов устройства, мыхоц первого эявмевн те ИЛИ соесшвен со сметным вхоаом первого триггера, выхоц которого яв« мшвтся вых;оЕЕс « ycrpoflcrata, ешоэтяый выхов к 1жабп раз{ЖЕ|а регистра соеш не с соогвотсугоуюпшм вхощомг BTopidro ИЛИ, выхоц которого coeoifiieR с ешшвшодм вхоаом второго трэттера я у1фааляюищм вхоаом первого трнггё- paj ууя&мЛ вхоа Трвгг(фа я яяется у1фавлякшшм вхоаом устройства, еютвчвый кыход квкаого раоряпа регист ра соейвиен с 1Юрвым входом соогвет ству1гаюч} И группы, а выхоц кажаого элемпгга И rffymat соеовнен с соответстцгкмикм вхоцом первого эц ммЕта ИЛИ, : вулмдам tatow соответи. ствунжюто разрхаа рогкстра в входом соогвётстфующего алемднта ИЛИ грулом, иул9кЛ выхоа второго .1рвгг«ра сОд ошен с сОонФетствуюшнмв вхоаамв всех ап«мевт « ИЛИ группы в с BXOQOM первого элемента И грушш, выхоа 4 -го элемента ИЛИ груцаы (гае (и..1), а щ -коюяество рафяаоЁ регистра) соесжвев с вйвв1Х BbtM кодом (Ч4-1)нго пе} |Гента Игруп иы, о т л в ч а ю ш е ее тш, «сто, с ашЕЬю ущх ще«вя устройства, выхоп каждого i-i-ro 9пви&пл ШМ группы, кроме ( i «iO ro coeeiflaReB о codinMiw ст)Едпощдал вхоаом (| апёмента ИЛИ грушпд, еавиичш 1й ш1хо(| квжаого i нго : раврясса регвстра сое1Швея с роотвепу : OTByiotsHM вхоаом алшдента ИПИ , группы.сл 60

СОКИ COBETCHHX

М Н У

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТ

ГОСУДАРСТВЕННЬф НОМИ ТЕТ СССР

AO ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHP}iff Ô (21) 3372841/1824 (22.) 13.11.81 (46) 23 05.83, Бима. 34 19 (72) Н. Ф. Моровов и В. Q, урусов (71) Институт технической кибериетм. ки AH Белорусской GCP . (53) 681.3 (088.8) (56) 1. Авторское свинетельство СССР, М 767769, кл. 606 F ll/08, 1978.

2. Авторское свнветельство СССР Ин 767769, In. ООВ F 11/08, 197Â (протолкни). (64) (57) УС ГРОЙСТИО ДЛЯ ОПРЕДЕ

ЛЕНИЯ ЧЕТНОСТИ ИНФОРМАЦИИ, со вержааее репистр, первый н второй элементы ИЛИ, первый и второй i, группу элементов И и группу элвмеи » тов ИЛИ, причт ещпиниые вховы хамного раеряца регистра обравувт - грунпувхоцов .устройства эыхщ первого элем4нь та ИЛИ соевинен со счетнйм. входом первого триггера, . выкои aoroyoa ив лиетса выхоиом устройства, еаииичный выхоа кажвого разрища регистра соевое» нен с соответствующим .вхоцом вщзя6 9 элемента ИЛИ, выхов которого сэещаеи о еаиничным аховом второго триггера„.SU„„11 5: А и уиравляюакм аховом первого тригге ра, нулевой вкоа второго. триггера яв елииичиый выход ка кдого paepaia регист ра соелииен .с .первым входном cooraer ствующего элемента И груаиы, а выхов каащого элемента И грузшы соепинеи с аоответствуюакм вховом первого эле мента ИЛИ,.с нулевым иковом cocesem ствупйцего раэриаа. регистра н вховом соответствующего элемента ИЛИ груд пыр зц левой выхо5. второго триггера сое

arsis с соответствуюшими вхоаами всех элементов ИЛИ группы и с инверсным входом первого элемента И группы, выхов 4 -re элемента ИЛИ группы е (гве 1- 1 (VI- 1), а 9 ксщичество разрядов регистра) соеаииеи с иивероным иковом (i+1)wo элемента И грув» пы, о т л и ч а ю а е е с -и тем, что, с целью упрощения -yatpeaeraa„aasaog кажного 4 го элеиента ИЛИ грузи3ы, кроме (i Й)-го,соединен с соочвев»

" стщчощнм вхсщом (4 ч4) го- элемента ИЛИ групп, единичный выкеи ивищого i го реарда регистра соепинаж с соответ

: ствралим вховом -го элемента ИПИ, группы

f019453

45

55

Изобретение относится к вычисли тельной технике и может быть испопьзовано цпя проверки на четность ипи в цекоцируюшик устройствах цля опрецепения веса в кодовых комбинациях корректирующих коцов, принимаемык в параплельном коде.

Известно асинхронное устройство для определения четности информации, соцержашее регистр, элемент ИЛИ, триггер со счетным вхоцом, пороговый блок, группу элементов ИЛИ и группу элементов И (1) .

Нецостаток этого устройства заключает- 5 ся в цовопьно бопьшом объеме оборуцо вания порогового блока, который ввзрастает с увеличением числа разрядов регистра. Тактовые импупьсы, OIIpaIIIIIaaIo шие состояние регистра, прохоцят по сравнительно цдинной цепочке последовательно соециненных элементов И, вносящих зацержку особенно при бопь шик значениях разряцности информационного кОца и высОкОй частоте поступления информации. Без дополнительного оборуцования невозможен поцсчет числа единиц в регистре.

Наибопее близким техническим решением к предлагаемому является устройство цчя определения четности информации, содержащее регистр.. элементы ИЛИ, счетный триггер, группу, элеменгов И группу элементов ИЛИ, причем выход кажцого элемента И грут

35 пы соецинен с нулевым вхоцом соотвеъствуюшего разряца регистра и с соответствуюшим вхоцом элемента ИЛИ. Выхоц каждого j -го элемента И группы соецинен с соответствуюшим вхоцом всех элементов ИЛИ группы от 1 -го цо (и -1)-го { 2 3 °

Недостатком этого устройства яв ляется то, что число вхоцов элементов ИЛИ группы возрастает цо закону арифметической прогрессии и приводит к увеличению количества и типов инте» грапьных микросхем. Из-за ограничения на количество вхоцов микросхем при увеличении разряцности регистра возникает необхоцимость выполнения элементов группы ИЛИ в вице каскадного соецинения микросхем, что увеличивает количество оборуцования и снижает быстродействие. При увеличении разряцности регистра возрастает нагрузка элементов И группы, что вынужцает при И +1 YN (гце ю -цпина информационного кода, Al - нагрузочная cIIo» собность элемента И группы) дублировать элементы И группы. Это также увеличивает количество оборуцования.

В этом устройстве независимо от соцержимого разряца регистра (1 или

«О,), сигнал прохоцит по оцинаковой цепи ИЛИ-И, что снижает быстродействие.

Цель изобретения - упрощение усч ройства и повышение быстроцействия.

Поставленная цель достигается тем, что в устройство цпя определения чу» ности информации, содержашее регистр, первый и второй элементы ИЛИ, первый и второй триггеры, группу элементов И и группу элементов ИЛИ, причем ециничные вхоцы каждого разряца регистра образуют группу вкоцов устройства, выхоц первого элемента ИЛИ соецинен со счетным вхоцом первого триггера, выхоц которого является выхоцом уст ройства, ециничный выхоц кажцого разряца регистра соединен с cooraeT ствуюшим вкоцом второго элемента ИЛИ, abIxoQ которого соединен с ециничным вхоцом второго триггера и с управляюшим вхоцом первого триггера, нулевой вход второго триггера является управпякм шим вхоцом устройства, ециничный выхоц каждого разряца регистра соецинен с первым вхоцом соответствующего элемента И группы, а выхоц кажцого эпемента И группы соецинен с соответствуюшим вхоцом первого элемента ИЛИ, с нулевым вхоцом соответствующего, разряца регистра и axoIIoM cooraerma щего элемента ИЛИ группы нулевой abIxoII второго триггера соецинен с соответствующими вхоцами всех элементов ИЛИ группы и с инверсным входом первого элемента И группы, выхоц 1 -го эпемента ИЛИ группы, где 1- 1 (й-1), a n -количество разряцов регистра, соединен с инверсным вхоцом (1+1)-го эдемента И группы, выхоц кажцого i -ro элемента ИЛИ группы, кроме (p -1)-ro соецинен с соответствуюшим входом ( (1+1) — ro элемента ИЛИ группы, единичный выкоц 1 -ro разряца регистра соединен с соответствующим вхоцом i -ro элемента ИЛИ группы.

В связи с тем, что число вхоцов элементов ИЛИ группы не возрастает по закону арифметической прогрессии, структура устройства приобретает oIIнороцность и упрощается, а быстродействие йовышается из-за сокрашения дпины логических цепей опроса состояний нулевых разряцов, регистра, Прь1019453 4 первого триггера 6. Сигнал с выхода элемента И 2.1 по цепи обратной свя зи также осуществляет стирание 1 в первом разряце регистра и поццержи вает запрещающий единичный сигнал на выходе элемента ИЛИ 3.1 после стирания 1 в первом разряце регистр ра цо тех пор, пока на выхоце элемента И 2,1 появится "О".

После этого на всех вхоцах элемента ИЛИ 3.1 установится О, и разре шаюший нулевой сигнал.разрешит опрос слецуюшего разряца регистра. Если же в первом разряце регистра записан

15 О, то после подачи разрешающего нулевого сигнала с выхода второго триггера выхоц элемента ИЛИ 3.1. устано»вится в "0", разрешая тем.самым опрос следующего разряца регистра.

Э имушества прецлагаемого устройства тем выше, чем чем больше число разрядов регистра.

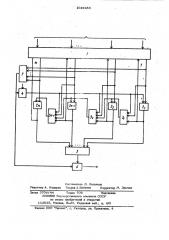

На чертеже.лрецставлена структурная схема прецлагаемого устройства.

Устройство соцержит регистр 1 с выхоцами разрядов, соецйненных с соответствуюцжми элементами И 2.1-2Р груп пы и ИЛИ 3.1-3. (И -1) группы, 1 -ы элемент ИЛИ 3.1-3. (И1) группы соединен с инверсным вхоцом (1 +1)-го элемента И 2.1-2.. и группы и с соответствующим вхоцом (1+1) -ro элемента ИЛИ 3.1-3. (n -1) группы, второй триггер 4, элемент ИЛИ 5, вхоцы которого соединены с выхоцом coorseT ствуюшего элемента И 2.1-2. И груп» пы, вхоцами соответствующих разряцов регистре и элементов ИЛИ 3,1-3. (Игруппы, первый триггер 6 и второй щ0 элемент ИЛИ 7.

Устройство работает следующим образом.

В исхоцном состоянии триггер 4. нахоцится в единичном состоянии, тр п р5 гер 6 - в нулевом, На выхоцах всех элементов ИЛИ группы установлен за.прешающий ециничный сигнал. Вхоцная цвоичная информация поступает в ираэряцный регистр 1 B параллельном 30 коде. После окончания записи информа ции второй триггер сигналом управляю» щего вхоца устройства переводится в нулевое состояние, Если в первом разряце регистра записана 1", то пооле подачи разрешающего нулевого сигнала с выхоца второго триггера выхоц элемента ИЛИ 3.1 уцерживается в сос тоянии "1 сигналом с ециничного выхоца первого раэряца регистра. Нулевой сигнал с второго триггера, поцан40 ный на инверсный вхоц элемента И 2.1 разрешает появление на выхоце 2,1 ециничного сигнала, который через пер вый элемент ИЛИ 5 поступает на вход фЯ

В цальнейшем работа устройства осу» ществляется аналогичным образом. Мо» мент времени окончания работы устрой . ства определяется вторым элементом ИЛИ 7 срабатывающим при обнулеиии регистра 1.

Появление нулевого сигнала на выхоце элемента ИЛИ 7 дает возможность обеспечить считывание значения тригге ра 6 и установку триггера 4 в исходное состояние.

При необходимости устройство может быть использовано цля .опрецеле ния числа ециничных сигналов, например, в коцах постоянного веса. Для этого цостаточно в устройство вместо триггера 6 включить обычный цвоичный сче чик, фиксируюший зацанный вес в анализируемых коцовых комбинациях.

Прецлагаемое устройство облацает оцнороцностью структуры, . меньшим количеством оборудования и повышенным быстроцействием по сравнению с извеса ныме

1019453

C Оставитель Л. Логачева

Редактор А. Козориз Техред А.Бабинец Корректор М. немчик

Заказ 3706/44 Тираж 706 Подписное

ВНИИПИ Государственного комитета CCCP по делам изобретений и открытий

1Х3035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП Патент, г. Ужгород, ул. Проектная, 4