Цифровой функциональный преобразователь

Иллюстрации

Показать всеРеферат

ШФРрЭОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содеркащий первьй и второй VI-разрядные счетчики, первую группу элементов И, первый элемент ИЛИ, первый сумматор, пермлй вход котсфого соединен .с входом устройстэаа, выход перврго элемента ИЛИ соединен с вторым входом первого сумматора, выход которого подключен JC входу первого счетчика, вход второго счетчика соединен с входом устройства.о т л и ч а ю щи и с я тем, что, с целью расширения класса решаемыхзадач аа счет дополнительного вычисления функций и в него введены вторая группа элементов И, второй элемент ИЛИ, второй суммачор , ключ и третий счетчик, вход котогрого соединен с выходом второго суммато ра,.первый выход которого соединен через ключ с входом устройства, второй вход второго сумматора подключен к выходу второго элемента ИЛИ, входы которого соединены с выходами элементов И второй группы, первый и второй входы 1-вхоДового элемента И которой ( i 3, ... , И + 2) соединены соответственно с инверсным и прямым разрядными выходами, начиная с младшего разряд , второго и, начиная со ставшего разряШ) nejHsoro счетчиков, третий вход Ц -«ходового элемента И второй группы подключен к входу устройстзаа, входы, с (i+l)Htx) по ( )-й, (-1 И)-входового элемента И второй группы соединены (О с прямыми выходами разродов, с пеового по 1 ir-й, BTOjwro счетчика, первый и второй входы i -входового элемента И пе|жой группы соединены соответственно с инверсными разрядными выходами, начиная с младшего разряда, первого и второго счетчиков, третий вход -i -входового элемента И первой группы подключен ;К входу первого счетчика, входы, с (i +1)-го по ( i + «)-«, ( i + ц)-входосо ел вого элемента И первой группы соединены с прямыми выходами разрядов, с первого по и -и, первого счетчика, выходы элементов И первой группы подключены к входам первого элемента ИЛИ.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

O з(Я) 606F 5/3

ОПИСАНИЕ ИЭОБРЕТЕ

H- ASTQPCHOIVPV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (2 1) 3388764/18-24 (22) 02.02,82 (46) 23.05.83. Бюл, ¹ 19 (72) B. Б. Дудыкевич и 3. М. Стрилецкий (71) Львовский ордена Ленина политехнический институт им. Ленинского комсомо(53) 681, 325(088.8) (56) 1:. Данчеев B. й. Мифро-частотные вычцслительные устройства. М., "Энергия», 1976, с 60.

2. Айторское свидетельство СССР

¹ 572783; кл. 606 7/38, 1975 (прототип). . (54) (57) ЦИФРОВОЙ . ФУНИЛИОНАЛЬНЫЙ

ПРЕОБРАЗОВАТЕЛЬ, содержащий первый и второй И -разрядные счетчики, первую группу элементов .И, первый элемент ИЛИ, первый сумматор, первый вход которого соединен .с входом устройства, выход пери@го элемента ИДИ соединен с вторым входом. первого сумматора, выход которого подключен к входу первого счетчика, вход второго счетчика соединен с входом устройства О т л и ч & ю шийся тем, что, с целью. расширения класса решаемых аадач за счет дополнительного вычисления функций )(Р „Х и ХЮ1 )(-X, в него введены вторая. группа элементов И, второй элемент ИЛИ, второй сумматор, ключ и третий счетчик, вход кото-..

„„SU„„.1 03 9457 А

Ъ рого соединен с выходом второго сумматора,,первый выход которого соединен через ключ с входом устройства, второй вход второго сумматора подключен к выходу второго элемента ИЛИ, входы которого соединены с выходами элементов И второй группы, первый и второй входы j-входового элемента И которой (1 " 3, ..., И + 2) соединены соответственйо с инверсным и прямым разрядными выходами, начиная с младшего разряда, второго и, начиная со старшего разряда, первого счетчиков, третий вход

j -аходового элемента И второй группы подключен к входу устройства, входы, с (1 +1) го по (+ n) é, (И) входово» а

ro элемента И второй группы соединены с прямыми выходами разрядов, с rrensor по и -й, второго счетчика, первый и второй входы i -входового элемента И первой группы соединены соответственно с.инверсными разрядными выходами, на- 2 чиная с младшего разряда, первого и второго счетчиков, третий вход i -входового элемента И первой группы подключен к входу первого счетчика, входы, с 4, ) (i +1)-го по (i + и ) й, (i + и ) -входо- . о вого элемента И первой группы соедине- (© ны с прямыми выходами разрядов,. с пер- ф, вого по н -й, первого счетчика, вы3соды { д элементов И первой группы подключены к входам первого элемента ИЛИ.

1019457

Изобретение относится к автоматике вычислительной и измерительной технике и может быть использовано при раэработ ке цифровых систем управления, в специал иэированных вычислительных устройствах, в линеариэаторах характеристик первичных измерительных преобразователей и т.п.

Известно устройство для воспроизведения логарифмической функции, содержащее три счетчика и схему сравнения (1) .

Недостатком этого устройства является пониженная точность вычисления лога-. рифмической функции и узкий класс решаемых задач.

Наиболее близким к предлагаемому по технической сущности является цифровое устройство для вычисления логарифмов чисел, представленных число-импульсными кодами, содержащее первый и второй счетчики, элементы И блока, эле20 мент задержки, элемент ИЛИ и блок умножения, причем входы первого и вторс

ro счетчиков соединены с импульсными и потенциальными входами элементов И блока соответственно, выход элемента ИЛИ соединен с входом блока умножения и первого счетчика, выход элементов И блока соединен с входом элемента задержки, выход которого соединен с первым входом элемента ИЛИ, второй вход З0 которого соединен с входом устройства и входом второго счетчика,2 .

Известное устройство характеризуется узким классом решаемых задач, что заключается в невозможности вычисления З функции Ю X

Целью изобретения является расшире- ние решаемых задач эа счет дополнитель,иения фукций Х Е, Х ° ХЕ„Х-Х.

Поставленная цель достигается тем, 40 что в устройство, содержащее первый и второй и -разрядные счетчики, первую группу элементов И, первый элемент ИЛИ, первый сумматор, первый вход которого соединен с входом устройства, выход пер-4 вого элемента ИЛИ соединен с вторым входом первого сумматора, выход которого подключен к входу первого счетчика, вход второго счетчика соединен с входом устройства, введены вторая группа элементов И, второй элемент ИЛИ, второй сумматор, ключ и третий счетчик, вход которого соединен с выходом второго сумматора, первый вход которого соединен через ключ с входом уст55 ройства, второй вход второго сумматора подключен к вьгсоду второго элемента ИЛИ, входы которого соединены с выходами элементов И второй группы, первый и второй входы i -входового элемента И которой (1**3...,, у)+2) соединены соответственно с инверсным и прямым разрядными выходами, начиная с младшего разряда, второго и, начиная со старшего разряда, первого счетчиков, третий вход j -входового элемента И второй группы подключен к входу устройства, входы с (+1)-го по (+ и)-й, (1+ И)-входового элемента И второй группы соединены с прямыми выходами разрядов, с первого по и -й, второго счетчика, первый и второй входы -входового элемента И первой группы соединены соответственно с инверсными разрядными входами, начиная с младшего разряда, первого и второго счетчиков, третий вход -входового элемента И первой группы подключен к входу первого счетчика, входы, с (+1)-го по (1 + И )-й, (< + й)-жодового элемента И первой группы соединены с прямыми выходами разрядов, с первого по И-й, первого счетчика, выходы элементов И первой группы подключены к входам первого элемента ИЛИ.

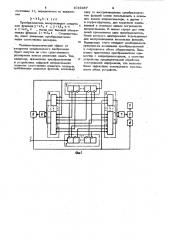

На фиг. 1 представлена блок-сехема преобразователя; на фиг. 2 — вариант выполнения импульсного сумматора.

Преобразователь (фиг. 1) содержит вход 1 устройства, первый счетчик 2, второй счетчик 3, первую группу элементов И 4, вторую группу элементов И 5, первый элемент ИЛИ 6, второй элемент

ИЛИ 7, первый сумматор 8, второй сумматор 9, ключ 10, третий счетчик 11.

Сумматор (фиг. 2) содержит элемент ИЛИ 12, элемент 13 задержки, входы 14 и 15, выход 16.

Счетчик 2, группа 4 и элемент 6 образуют первый двоичный умножитель ч астоты, управляемый счетчиком 3. Счет.чик 3, группа 5 и элемент 7 образуют второй двоичный умножитель частоты, управляемый счетчиком 2. Первый двоичный умножитель управляется кодовой комбинацией, снимаемой с инверсных разрядных выходов счетчика 3. Второй двоичный умножитель управляется кодовой комбинацией, снимаемой с прямых разрядных выходов счетчика 2. Элементы И .групп 4 и 5 являются (2+ n)-входовыми, где и- номер разряда счетчикаделителя двоичного умножителя частоты, с инверсным выходом которого соединен данный элемент И. Каждый элемент И групп 4 и 5 стробируется импульсами, поступающими на входы счетчиков 2 и .3.

Импульсы на выходах элементов И или или, окончательно, 3 10194 групп 4 и 5 не совпадают между собой, так как импульс на выходе соответствующего элемента И появляется лишь тогда, когда разряд счетчика-делителя, с инверсным выходом которого соединен данный

5 элемент И, находится в нуле (прямой выход - в нуле), .а все предЫдущце разряды в единице. Такие же двоичнв|е умножители выпускаются отечественной промышленностью в виде микросхемы 50

К155ИЕ8, которая может быть применена при практической реализации устройствами

Устройство работает следующим образом.

Перед началом работы все разряды первого счетчика 2 устанавливаются в нулевое состояние, а все разряды второго счетчика 3 — в единичное состояние.

Если ключ 10 замкнут, то входная им20 пульсная последовательность поступает . на вход второго (импульсного) сумматора 9, если разомкнут — не поступает.

Пусть для определенности ключ замкнут.

На вход 1 устройства поступает импульс; ная последовательность X. Приращения этой последовательности поступают на ,вход второго счетчика 3 и формируют в нем текущее значение управляющего 5 ода первого двоичного умножителя. Приращения dX, поступают также на первый

30 вход первого сумматора 8. Приращени, поступающие с выхода первого с.умматора 8 на вход первого счетчика 2, вызывают появление на выходе первого двоичного умножителя приращений (3 поступающих на второй вход первого сумматора 8. Следовательно, (4)

Учитывая, что все разряды второго 40 счетчика 3, управляющего первым двоичным умножителем, находились первоначально в единичном состоянии и, учитывая также, что этот умножитель управляется кодовой комбинацией, снимаемой с 45 инверсных разрядных выходов второго счетчика 3, определим значение Д 5

С5п-1-(Х-5) 34

Ь5 (1) где у5 - коэффициент и зресчета счетчи- 50 ков; (yn-5)- емкость счетчика; (y q)- значение йисла, формируемого входной импульсной последовательностью в счетчике; 55

$5n-g-(y-5))- числовое значение кода, управляющего первым двоичным умножителем.

57 4

После преобразований выражение (2) принимает вид ХИх (Ъ)

Подставляя (3) в (1), получим

d. =а Ф О55 X)dX (4)

2. Х 511 или, после упрощения и разделения переменных (6)

Интегрируя (5) д» вЂ”.-- „,(ь) получим

5„ и Х (a) Z=vnR )(. (S)

Полученное значение 2, формируемое в первом счетчике 2, является числовым значением управляющего кода второго двоичного умножителя, образованного вторым счетчиком Э, второй группой элементов. И 5 и вторым элементом

ИЛИ .7. Приращения ДХ, поступающие на вход второго счетчика 3, вь5зывают появление приращений на выходе второго двоичного умножителя или, учитывая (8) а„=е„х а„ о)

Приращения (3y поступают íà пе5з- . вый вход второго сум матора S, на второй вход которого через замкнутый ключ 10 поступают приращения ДХ

На выходе второго сумматора 9 получаем . Ч+ Х

Приращения д ъ. интегрируются третьим счетчиком 11, в котором фиксируется р езультат преобразования и)(x+dx (." ) Э» и юа =хе„ а„.га„; о )

0 О

>j =(xe x--:x)! х),; (м) 3 = xe„x-x+x (g) = А(55 X (6)

Если ключ 10 разомкнут, то результат преобразования, фиксируемый третьим

5 10194 счетчиком 11, определяется из выражения = с, - (7).

Преобразователь воспроизводит следующие функции:у=к „X у ;Xgи X-X и тамб Х, тогда как базовый обьекътолько функцию Z.= >.О м Х . Следователь-но, класс решаемых преобразователем задач сушественно расширен.

l0

Технико-экономический эффект от внедрения предлагаемого изобретения будет получен за счет существенного расширения класса решаемых задач. Так, например, применение преобразователя в устройствах цифровой аплроксимации позволит существенно повысить точность, приближения заданных функций, поскольку одну из воспроизводимых преобразователем функций можно использовать в основном канале алпроксиматора, а другиеs корректирующем, для коррекции возникающей и основном канале погрешности аппроксимации. В нашем случае для этих целей применяется один преобразователь, блоки которого одновременно используются для воспроизведения нескольких функций.

Вследствие этого отпадает необходимость применения нескольких преобразователей и сокряцается обьем оборудования. Возм ожно применение преобразователя совместно с микропроцессорами, в качестве устройства предварительной обработки и оступающей информации, что позволит более эффективно использовать возможности обоих устройств.

1019487

Составитель А. Шуляпов

Редактор Il. Гратилло Техред М.Гергель Корректор М. Шароши

Заказ . 3706/И Тираж 706 Подписное

ИПИ%1И Государственного комитета СССР по делам изобретений и открытий

13.:.3035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ИПП "Патент", г. Ужгород, ул. Проектная, 4