Устройство управления для доменной памяти

Иллюстрации

Показать всеРеферат

692 (И2, СОКИ СОВЕ ИХНИХ

МЦЮНЯЮ

1%СПУБЛИН @р Gi 11 С 11/14

ОПИСАНИЕ ИЗОБРЕТЕН

ГОСУДАРСТВЕННЫЙ НОМИ ГЕТ СССР

ЛМ 4й II

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 3392843/18-24 (22) 03.02.82 (46) 30.05.83. Бюл. В 20 (722 В.И.Косов, A.Ì.Èâàíîâ, К.В.Милованов, В.И.Мхатришвили, A.È.Ñàâåëüåâ и F).È.Ô êHí

f53) 681.327.66(088.8) (56) 1. Авторское свидетельство СССР

" 22 519761, кл. Ci 11 С 19/00, 1976.

2. Авторское свидетельство СССР

9 754480, кл. G 11 С 19/00, 1980 (.прототип ) .. (54)(57 ) УСТРОЙСТВО УПРАВЛЕНИЯ ДЛЯ

ДОМЕННОЙ ПАМЯТИ, содержащее генератор тактовых импульсов, первый выход ко торого является выходом устройства,. а второй выход подключен к блоку полупоатоянной памяти, регистр адреса, подключенный к кодовым шинам адреса н "Установка"0", и регистр числа, подключенный к кодовым шинам числа и

"Установка "0", о т л и ч. а ю щ е е— с я тем, что, с целью повышения быс1родействия и надежности устройства, оно содержит три триггера, первые входы которых соединены с кодовой . шиной "Установка "0", второй вход второго триггера соединен с .кодовой шиной "Запись адреса", второй вход третьего триггера соединен с кодовой шиной "Счет", второй и третий входы первого триггера соединены соответст венно c третьим. выходом генератора.

-тактовых импульсов и выходом блока полупостоянной памяти, счетчик адре са, блок сравнения, первый вход ко торого подключен к выходу счетчика ! адреса, а второй вход — к первому выходу регистра адреса, элементы И и ИЛИ, причем первые входы первого и второго элементов И соединены с кодовой шиной "Запись", вторые входыс выходом первого триггера, третий вход первого элемента Й подключен к выходу регистра числа, а выход первого элемента И вЂ” к первому входу первого элемента ИЛИ, выход которого является выходом устройства, третий вход второго элемента И подключен к второму выходу регистра адреса, а выход второго элемента И - к второму входу первого элемента ИЛИ, первый Я вход третьего элемента И соЕдинен с выходом второго триггера, второй вход с первым входом четвертого элемента И, выход которого подключен С к третьему входу регистра числа, третий вход — с выходом первого тригге- Я ра н вторым входом четвертого элемента И, а выход — с первым входом второго элемента ИЛИ, выход которого { подключен к входу счетчика адреса, причем первый вход пятого элемента И связан с выходом третьего триггера, второй вход — с первым выходом гене-, ратора тактовых импульсов, а выход— с вторым входом второго элемента ИЛИ, третий вход четвертого элемента И соединен с выходом блока сравнения, а четвертый вход - с кодовой шиной

"Считывание".

1020863

Изобретение относится к вычислительной технике и может быть использовано при построении устройств хранения дискретной информации на цилиндрических магнитных доменах (ЦМД).

Известно устройство управления 5 для запоминающего устройства, содержащее генератор тактовых импульсов, счетчик, блок записи-считывания инфОрмации, соециненный с разрядными и адресными шинами накопителя, дешифра- 10 тор, сумматор и элементы И « 1 3.

Недостатком данного устройства является невозможность разделения исправных и неисправных ячеек памяти накопителя. 15

Наиболее близким к предлагаемому является устройство управления для запоминающего устройства, содержащее генератор тактовых импульсов, элемент запроса, формирователь импульсов запроса приоритетной информации, выходной регистр, соединенный через элементы ИЛИ с каналом передачи данных, и блок буферной памяти приоритетной информации (2 ).

Недостатками известного устройства являются низкая надежность записи и считывания информации, а также пониженное быстродействие, связанное с большим временем различия дефектных ячеек и нахождением выбранных страниц 3 памяти. Отсутствие приоритета исключения дефектных ячеек памяти (регистров хранения ) в процессе работы «,тактового перебора ) ячеек и тактового определения нужного адреса страницы 35 значительно снижает быстродействие . записи и считывания информации, а следовательно, и надежность устройства в целом.

Цель изобретения — повышение быст- 4«) родействия и надежности устройства управления для доменной памяти.

Поставленная цель достигается тем, что устройство управления для доменной памяти, содержащее генератор так- 45 товых импульсов, первый выход которого является выходом устройства, а второй выход подключен к блоку полупостоянной памяти, регистр адреса, подклю енн«яй K 1

55 вход второго триггера соединен с кодовой шиной "Запись адреса", второй вход третьего триггера соединен с ко. довой шиной "Счет", второй и третий входы первого триггера соединены соответственно с третьим выходом генератора тактовых импульсов и выходом блока полупостоянной памяти, счетчик адреса, блок сравнения, первый вход которого подключен к выходу счетчика ,адреса, а второй вход — к первому, 65 выходу регистра адреса, элементы И и

ИЛИ, причем первые входы первого и второго элементов И соединены с кодовой шиной "Запись", вторые входы— с выходом первого триггера, третий вход первого элемента И подключен к выходу регистра числа, а выход первого элемента И вЂ” к первому входу первого элемента ИЛИ, выход которого является выходом устройства, третий вход второго элемента И подключен к второму выходу регистра адреса, а выход второго элемента И вЂ” к второму входу первого элемента ИЛИ, первый вход третьего элемента И соединен с выходом второго триггера, второй вход — с первым входом четвертого элемента И, выход которого подкЛючен к третьему входу регистра числа, третий вход — с выходом первого триггера и вторым входом четвертого элемента И, а выход — с первым входом второго элемента ИЛИ, выход которого подключен к входу счетчика адреса, причем первый вход пятого элемента И связан с выходом третьего триггера, второй вход — с первым выходом генератора тактовых импульсов, а выход— с вторым входом второго элемента ИЛИ, третий вход четвертого элемента И соединен с выходом блока сравнения, а четвертый вход — с кодовой шиной

"Считыва««ие".

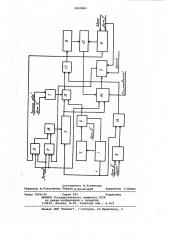

На чертеже приведена блок-схема устройства управления для доменной памяти.

Устройство содержит генератор 1 тактовых импульсов, первый и второй выходы которого подключены соответственно к входам блока 2 полупостоянной памяти и накопителя 3 на ЦМД, регистр

4 адреса, подключенный к кодовым шинам адреса и "Установка "0", регистр

5 числа, подключенный к кодовым шинам числа и "Установка "0", первый, второй и третий триггеры 6-8, счетчик

9 адреса, блок сравнения 10, первый

11, второй 12, третий 13, четвертый

14 и пятый 15 элементы И, а также первый 16 и второй 17 элементы ИЛИ.

Устройство управления для доменной памяти работает в двух режимах: запи-. си и считывания информации, причем считывание может .быть без разрушения хранимой информации — считывание с репликацией, и считывание с раэрушением информации — считывание с аннигиляцией. При записи информации в накопитель 3 на ЦМД генератор 1 тактовых импульсов выдает сигналы,. запускающие вращающееся магнитное поле в накопителе 3 и опрашивающие. блок 2 полупостоянной памяти. Перед началом работы первый, второй и третий триггеры 6-8, регистр 5 числа и регистр

4 адреса устанавливаются. в исходное положение с кодовой шины "Установка

"0 ". На кодовую шину "Запись " подается разрешающий потенциал, а на регистр 4 адреса — код адреса той страницы, s которую необходимо записать число. В блок 2 полупостоянной памяти перед началом работы записываются адреса исправных страниц и первый 5 же такт опроса заставляет блок 2 полупостоянной памяти выдать сигнал

"1" или "0" в зависимости от того, производится запись в исправную страницу или нет. Если страница исправ- tO ная, то первый триггер 6 устанавливается в состояние "1" и первый разряд из регистра 4 адреса по разрешающему потенциалу с первого триггера б через второй элемент И 12 и первый эле-15 мент ИЛИ 16 записывается в накопитель

3 на ЦМД. При неисправной странице первый триггер 6 остается в состоянии "0" и запись кода адреса страницы в накопитель 3 не производится.

Первый триггер 6 после окончания каждого такта сбрасывается в состояние "О". Таким образом, последова- тельно осуществляется запись адреса из регистра 4 адреса в накопитель 3 в исправные страницы памяти. После записи .адреса производится перезапись кода числа из регистра 5 числа через первый элемент И 11 и первый элемент

ИЛИ 16.также в исправные страницы накопителя 3 по. разрешающему потенциалу с первого триггера 6. После записи в исправные страницы их кодов адреса и кодов записываемых чисел доменная память готова к работе в режиме считывания (с аннигиляцией или репликацией — разрушением информации при считывании или без разрушения ).

Перед считыванием информации все блоки также устанавливаются в исходное состояние сигналом "Установка 40

"0". Затем начинает работать генератор 1 тактовых импульсов, который запускает вращающееся магнитное поле в накопителе 3, устанавливает в каждом такте первый триггер 6 и опрашивает 45 блок 2 полупостоянной памяти. Одновременно по кодовой шине "Запись адреса" устанавливается в состояние

"1" второй триггер 7. В течение первых тактов код адреса страницы из накопителя 3 по разрушающему потенциалу с второго триггера 7 и первого триггера 6 (в случае исправных страниц ) записывается через третий элемент И 13 и второй элемент ИЛИ 17 в счетчик 9 адреса. Этот код адреса сравнивается в блоке 10 сравнения с записанным перед началом работы адресом выбранной страницы в регистр 4 адреса. При несовпадении кодов адресов начинает работать третий триггер

8, устанавливаеьый в состояние "1" сигналов с кодовой шиной "Счет". Импульсы с генератора 1 тактовых импуль сов через пятый элемент И 15 и второй. элемент ИЛИ 17 проходят на счетчик 9 адреса, увеличивая его содержимое с приходом каждого такта на "единицу".

Одновременно в каждом такте производится сравнение содержимого счетчика

9 адреса и регистра 4 адреса на блоке 10 сравнения. При равенстве кодов блок 10 сравнения выдает сигнал разрешения на четвертый элемент И 14 и код числа с исправных страниц с нако(пителя 3. фиксируется в регистре 5 числа в случае наличия разрешающего потенциала с кодовой шины "Считывание".

Таким образом, использование предлагаемого устройства управления для доменной памяти позволяет производить запись кодов адреса страниц и кодов чисел в исправные страницы доменной памяти, а при считывании информации производить надежное различие исправных страниц, быстро и надежно определять адреса считанной страницы и затем последовательным счетом доводить до нужного адреса и считывать код числа из требуемой страницы,значительно повысить быстродействие при считывании информации иэ доменной памяти и надежность работы.

10208б 3

Составитель Ю.Розенталь

Редактор И.Рачкулинец Техред Б далекорей Корректор О.Билак

Заказ 3904/43 Тираж 594 Подлисное

BHHHIIH Государственного комитета СССР по делам изобретений и открытий

113035,, Москва, Ж-35, Раушская наб, д.4/5 филиал ППП "Патент", г.".жгород, ул.Проектная, 4