Устройство для контроля памяти

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАМЯТИ , содержащее формирователь контрольных сигналов, .регистры, первый коммутатор, формирователь сигналов ошибки, формирователь сигналов записи , блок управления, первую схему сравнения, формирователь сигналов четности, деши.фраторы, блок исправления ошибок, и первый элемент ИЛИ, причем первый выход формирователя контрольных сигналов .подключен к одним из входов первого регистра, выход которого соединен с пврвыми входами первого коммутатора, блок, исправления ошибок и формирователя сигналов ошибки, второй вход которого .подключен к выходу второго регистра, а выход - к первому входу первой схемы сравнения, входу первого дешифратора И:входу формирователя сигналов четности, выход которого соединен .с первым, входом второго девшфратора , второй-и третий входы которого подключены соответственно к выходу первого элетлefнтa ИЛИ и к. нулевому выходу первого дешифратора информационный выход которого средийей с вторыми входами исправления ошибок и первого коммутатора ,- выход которого подключен к первому входу формирователя сигналов записи, второй вход и выход которого соединены соответственно с контрольным выходом первого дешифратора и с вторьм входом первой схемы сравнения, выходы которой подключены к входам первого элемента ИЛИ, вход , фoEяvlиpoвaтeля контрольных сигналов и третьи входы первого регистра и первого кс ммутатора соединены соответственно с первым, вторьми третьим выходами блока уп.равления, четвертый вь1ход которого, второй выход форм.ирователя .контрольных сигналов, выход первого коммутатора и выход формирователя сигналовзаписи являЧ ются соответственно управляницим выходом , выходом корректирующих сигналов , информационнЕЛМ выходом и выходом записи устройства, второй вход первого регистра и вход второго регистра объединены и являются информационным входом устройства, о т л ичающе .еся тем, что, с целью (Л повышения точности контроля устройства , в него введены второй коммутаС тор, вторая схема сравнения, третий и четвертый регистры,второй, третий, четвертый и пятый элементы ИЛИ, при--в чем входы второго коммутатора подключены соответственно к выходу блока исправления ошибок, к выходу формирователя сигналов ошибки и к пятому выходу блока управления, а.вы-, ходы - к одним из входов третьего регистра и второй схемы сравнения, выходы которой соединены с входами четвертого регистра, входы второго, третьего и четвертого элементов ИЛИ подключены соответственно к выходаи. третьего регистра, к выходам четбер-. того регистра и к выходам второго дешифратора, а выходы - к входгад пятого элемента ИЛИ, выход которого соединен с входом блока управления , шестой и седьмой выходы которого подключены соответственно к управляющим входам третьего и четвертого регистров, другой вход второй схемы сравнения соединен с третьим выходом формирователя контрольных сигналов, выходы формирователя сигналов четности , первого элемента ИЛИ, нулевой

,Я0„„20865, A

СОЮЗ СОЕЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

3{Я1 G 11 C 29/00

ОПИСАНИЕ ИЗОБРЕТЕ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

f10 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3393200/18-24 (22) 05. 02. 82 (46) 30.05. 83. Бюл. 9 20 (72) Н. И. Вариес и A. К. Култыгин (53) 681 ° 327 (088. 8) (56) 1. Авторское свидетельстэо. СССР

И 744737, кл. G 11 С 29/00, 1978.

2. Авторское свидетельство СССР по заявке 9 3286966/18-24, кл. G 11 С 29/00, 1981 (прототип). (54) (57) УСТРОЙСТВО )(ЛЯ КОНТРОЛЯ ПА—

МЯТИ, содержащее формирователь контрольных сит налов, .регистры, первый коммутатор, формирователь сигналов ошибки, формирователь сигналов за-. писи, блок управления, первую схе.му сравнения, формирователь сигналов четности, дешифраторы, блок исправления ошибок и первый элемент ИЛИ, причем первый выход формирователя контрольных сигналов .подключен к одним из входов первого регистра, выход которого соединен с первыми входамй первого коммутатора, блок исправ ления ошибок и формирователя сигналов ошибки,-второй вход которого ,подключен к выходу второго регистра, а выход - к первому входу первой схемы сравнения, входу первого дешифратора и.входу формирователя сигналов четности, выход которого соединен с первым входом второго дешифратора, второй-и третий входы которого подключены соответственно к выходу первого элемента ИЛИ и к. нулевому выходу первого дешифратора, информационный выход которого соединен с вторыми входами блока исправления ошибок и первого. коммутатора,.выход которого подключен к первому входу формирователя сигналов записи, второй вход и выход которого соединены соответственно с контрольным выходом первого дешифратора и с вторым входом первой схемы сравнения, выходы которой подключены к входам первого элемента ИЛИ, вход формирователя контрольных сигналов и третьи входы первого регистра и первого коммутатора соединены соответственно с первым, вторым и третьим выходами блока управления, четвертый выход которого, второй выход формирователя .контрольных сигналов, выход первого коммутатора и выход формирователя сигналов записи явля+ ются соответственно управляющим выходом, выходом корректирующих сигналов, информационным выходом и выходом записи устройства, второй вход первого регис=ра и вход второго регистра объединены и являются информационным входом устройства, о т л и- Щ ч а ю щ е. е с я тем, что, с целью повышения точности контроля устрой- файф ства, в него введены второй коммута- НР тор, вторая схема сравнения, третий и четвертый регистры, второй, третий, четвертый и пятый элементы ЙЛИ, при- р чем входы второго коммутатора подключены соответственно к выходу блока исправления ошибок, к выходу формирователя сигналов ошибки и к пятому выходу блока управления, а..выходы — к одним из входов третьего регистра и второй схемы сравнения, ру выходы которой соединены о входами Ф четвертого регистра, входы второго, ф третьего и четвертого элементов ИЛЙ подключены соответственно к выходам ® третьего регистра, к выходам четвер-. того регистра и к выходам второго дешифратора, а выходы — к входам пятого элемента ИЛИ, выход которого с И. динан с входом блока управления,. аФ шестой и седьмой выходы которого подключены соответственно к управляющим входам третьего и четвертого регистров, другой вход второй схемы сравнения соединен с третьим выходом формирователя контрольных сигналов, выходы формирователя сигналов четности, первого элемента ИЛИ, нулевой

1020865

10 выход первого дешифратора, выходы третьего и четвертого регистров являются соответственно первым — пятым выходами контрольных сигналов устройства, третий выход формироватеИзобретение относится к вычислительной технике и может быть использовано при разработке аппаратуры для контроля памяти и запоминающих устройств с коррекцией ошибки.

Известно устройство, содержащее генератор кодов ошибки, дешифратор, схемы формирования синдрома, регистры и блок управления f 1 ).

Недостатком данного устройства является низкая точность при локализации неисправностей.

Наиболее близким к предлагаемому является устройство для контроля памяти, содержащее регистры, коммутатор, формирователи сигналов ошибки и четности, схему сравнения, дешифратор, блоки управления и контроля и элемент ИЛИ f2).

Недостатком известного устройства является низкая точность при локализации неисправностей, так как оно позволяет локализовать неисправность с точностью до двух блоков.

Цель изобретения — повышение точности контроля устройства.

11оставленная цель достигается тем, что в устройстве для контроля памяти, содержащее формирователь контрольных сигналов, регистры, первый коммутатор, формирователь сигналов ошибки, формирователь сигналов записи, блок управления, первую схему сравнения., формирователь сигналов четности, дешифраторы, блок исправления ошибок и первый элемент ИЛИ, причем первый выход формирователя контрольных сигналов подключен к одним из входов первого регистра, выход которого соединен с первыми вхо дами первого коммутатора, блока исправления ошибок и формирователя сигналов ошибки, второй вход которого подключен к выходу второго регистра, а выход - к первому входу первой схемы сравнения„ входу первого дешифратора и входу формирователя сигналов четности, выход которого соединен с первым входом второго дешифратора, второй и третий входы которого подключены соответственно к выходу первого элемента ИЛИ и к нулевому выходу первого дешифратора, информационный выход которого соеди15

50 ля контрольных сигналов и выход второго регистра являются соответственно шестым и седьмым выходами контрольных сигналов устройства. нен с вторыми входами блока исправления ошибок и первого коммутатора, выход которого подключен к первому . входу формирователя сигналов записи, второй вход и выход которого соединены соответственно с контрольным выходом первого дешифратора и с вторым входом первой схемы срав.— нения, выходы которой подключены к входам первого элемента ИЛИ, вход формирователя контрольных сигналов и третьи входы первого регистра и первого коммутатора соединены соответственно с первым, вторым и третьим входами блока управления, четвертый выход которого, второй выход формирователя контрольных сигналов, выход первого коммутатора и выход формирователя сигналов записи являются соответственно управляющим выходом, выходом корректирующих сигналов, информационным выходом и выходом записи устройства, второй вход первого регистра и вход второго реги-. стра объединены и являются информационным входом устройства, введены второй коммутатор, вторая схема сравнения, третий и четвертый регистры, второй, третий., четвертый и пятый элементы ИЛИ, причем входы второго коммутатора подключены соответственно к выходу блока исправления ошибок, к выходу формирователя сигналов ошибки и к пятому выходу блока управления, а выходы — к одним из входов третьего регистра и второй схемы сравнения, выходы которой соединены с входами четвертого регистра, входы второго, третьего и четвертого элементов ИЛЙ подключены соответственно к выходам третьего регистра, к выходам четвертого регистра и к выходам второго дешифратора, а выходы — к входам пятого элемента ИЛИ, выход которого соединен с входом блока управления, шестой и седьмой выходы которого подключены соответственно к управляющим входам третьего и четвертого регистров, другой вхОд второй схемы сравнения соединен с третьим выходо: формирователя контрольных сигналов, выходы формирователя сигналов четко ти, первого элемента ИЛИ, нулевой выход пятого дешифратора, выходы третьего и четвертого регистров яв1020865 ляются соответственно первым-пятым выходами контрольных сигналов устройства, третий выход формирователя контрольных сигналов и выход второго . регистра являются соответственно шестым и седьмым выходами контрольных сигналов устройства.

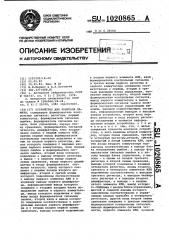

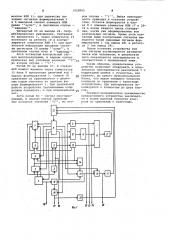

На фиг.1 приведена функциональная схема предлагаемого устройства; на фиг.2 — функциональная схема бло- 1О ка управления;

Устройство содержит (фнг.1} формирователь 1 контрольных сигналов, первый 2 и второй 3 регистры, первый коммутатор 4, формирователь 5 35 сигналов ошибки и формирователь б сигналов записи. На фиг.1 изображен контролируемый накопитель 7. .Устройство содержит также блок 8 управления, формирователь 9 сигналов четности, первую схему 10 сравнения, первый элемент ИЛИ 11, первый 12 и второй 13 дешифраторы, блок 14 исправления ошибок, второй коммутатор 15; третий регистр 16, второй элемент ИЛИ .17, вторую схему 18 сравнения, четвертый регистр

19, третий 20,четвертый 21 и пятый 22 элементы ИЛИ. На Фиг.1 обозначены соответственно первый — седьмой выходы 23-29 контрольных сигналов устройства.

Блок управления содержит (фиг.2) триггер 30 режимов,- синхронизатор 31, счетчик 32 импульсов, третий 33 и четвертый 34 дешифраторы и элемент

И 35.

Устройство работает следующим образом.

Режим записи является подготовительным: в устройстве формируется 4О и записывается в накопитель 7 информация, имитирующая ошибку в работе накопителя 7 и используемая далее для контроля правильности работы цепей коррекции ошибок ° Это проис- 45 ходит следующим образом.

Фбрмирователь 1 (фиг,1) подсчитывает импульсы, поступающие íà его вход с синхронизатора 31 (фиг. 2) блока 8 И формирует последовательность двоичных кодов, отличающихся друг от друга на единицу, преобразует эту последовательность в совокупность кодовых комбинаций, в которых единственная единица передвигается с позиции на позицию (бегущая единица ), которая поступает на первый выход формирователя l. Ha второй выход формирователя 1 по.ступают контрольные разряды корректирующего кода, которые записываются бО в накопитель 7. Информационные разряды записываются в накопитель 7 последовательно по адресам (адресные цепи накопителя условно не показаны) через регистр 2 и коммутатор 4.65 хранимая в накопителе 7 информация, содержащая по каждому адресу одну единицу в разных разрядах, при считывании рассматривается как нулевая информация, записанная с одной ошибкой"Р

B. режиме считывания информационные разряды с выхода накопителя 7 посту,пают. на регистр 2 (фиг.1), а контрольные разряды. — на регистр 3. Выходные сигналы с этих регистров по даются на входы формирователя 5, на выходе которого формируется двоичный код номера разряда, в котором имеет место ошибка. Этот код расшифровывается дешифратором 12, с выхода которого информационные разряды подаются на блок 14. На выходе блока 14 при правильной работе устройства имеет место исправленная информация нули во всех разрядах по всем адресам.

Скорректированная информация череэ. коммутатор 15 поступает на выход устройства. Кроме того, для обнаружения и локализации неисправностей в устройстве формируется пять контрольных сигналов (КС), кбторые также подаются на выходы 23-27 устройства.

Рассмотрим последовательно формирование и смысл каждого из пяти КС.

Первый КС на выходе. 23. Формирователь 9 определяет четность (выходной. сигнал формирователя 9 равен 1 ) или нечетность (выход ной сигнал равен 0 ) кода, содержащего ошибку. Формирование этого сигнала важно потому, что четный ну- . левой код номера разряда свидетельствует о наличии двух ошибок в считанной информации.

Второй КС на выходе 24 . Из вышеуказанного ясно, что необходмо йметь информацию о равенстве (сигнал 1 " ) или неравенстве (сигнал 0 ) нулю кода номера разряда, содержащего ошибку. Этот сигнал формируется на нулевом выходе дешифратора 12.

Третий КС на выходе 25 ° Формирователь 6, который в штатном режиме работы используется для записи информации в накопитель 7, в режиме .контроля используется для формирования контрольного сигнала. Сигналы с выхода дешифратора 12, соответствующие информационным разрядам, через коммутатор 4 подаются на вход.

Формирователя 6, с другого выхода дешифратора 12 непосредственно навход формирователя 6 поступают сигналы, соответствующие контрольным разрядам. По определению зтй сигналы совпадают с выходными сигналами формирователя 5. Поскольку формирователи 5 и 6 идентичны, при правильной их работе должны совпадать и выходные сигналы. Это контроли-. руется схемой 10 сравнения и эле1020865 ментом ИЛИ 11: при равенстве выходных сигналов формирователей 5 и 6 выходной сигнал элемента ИЛИ равен нулю, в противном случае . единице, Четвертый KC на выходе 26. Скор- 5 ректированная информация, считанная из накопителя 7, через коммутатор 15 поступает на регистр 16 и контролируется элементом ИЛИ 17: при правильной информации выходные сигна- 10 лы регистров 16 равны нулю, в противном случае есть и единицы .

Хотя четвертый контрольный сигнал многоразрядный, в первом случае присвоено ему условное значение 0, g во втором случае — 1 . !

Пятый КС на выходе 27. Б следующий момент времени через коммутатор

15 блок 8 пропускает двоичный код с выхода формирователя 5. Схемой 18 сравнения он сравнивается с двоичным кодом счетчика на третьем выходе формирователя 1. При правильной работе устройства сравниваемые коды должны совпадать, а при неправильной-,25 нет.

Хотя пятый КС вЂ” сигнал многоразрядный, в первом случае присвоим ему условное значение 0, во втором случае — 1, Любая неисправность приводит к останову устройства. Останов формируется в блоке 8 с помощью- элементов ИЛИ 17 и 2022 в конце каждого цикла считывания, когда уже сформировались все контрольные сигналы. Кроме пяти описанных выше контрольных сигналов выводятся также выходные сигналы формирователя 1 (на выход 28) и регист- ра 3 (на выход 29).

После останова устройства все эти сигналы анализируются автоматически или человеком, в результате чего локализуется неисправность в соответствии с приведенной ниже.

Таким образом, предлагаемое устройство позволяет обнаружить и локализовать неисправности накопителя 7 с коррекцией ошибок с точностью, как правило, до одного функционального блока, что вдвое повышает точность контроля по сравнению с известным устройством, где неисправности локализуются с точностью до двух блоков.

Технико-экономическое преимущество предлагаемого устройства заключается в более высокой точности контроля по сравнению с известным. !

Г

1

1.

I .1

1

1 !

1

I

I

Составитель Т.Зайцева

Редактор И.Рачкулинец Техреду.Кастелевич Корректор Г.Решетник

Заказ 3904/43 Тираж 594 Подписное

ВНИИПИ ГосударственноГо комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д..4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4