Устройство синхронизации сигналов

Иллюстрации

Показать всеРеферат

УСТК)ЙСТВр СИНХРЧЗНИЗА НИИ СИГНАЛОВ по авт.св. № 536611, ;О Т Л И ч а ю щ е ее я тем, что, с целью i 1юмехрустойяивостя, видены ШордедоватепьЕЕО со динешше анал1 атор ошибок С1яахро иаа1шк и коммутатор, а тавже элемент ИДИ, при этом выходы реверсивного счетчвка реа 1Е я шу1йто| соединены с обьеаввеав доли вхсахаыя пвр ,вого управителя и аналяЕабт ошвбенес с хр щиаащш1 к yGfuK&Bi которого подкшдчея вызсед dnsMewfu ИЛИ, д|7угбй вход н в;№сод авализато в сшвг бок синхронизаивн соедшзеш е сйотве ствуюшими кызито)л V входсм бшЕа пе реэшшси кода, причем к вховям элемевта ИЛИ подкивочекы соотвефст19ёв&о соотэетствуюшй шлод акащзатора Qiit бок сигасрс шзаци9г, соо1Фетствук 1ШЙ вход ашлизатора ошвСюк саюс рошЕзавин и соответртвукшшй вход формирователя импульсов переэа ИЕси 8 продЕШсеяия, |со торый является входом снгвала увравпе ния. (Л Сел

C0I03 С08ЕТСННХ

СООИАЯИОТИЧЕСНИХ

РЕСПУБЛИК (19) (11)

«)1д) Н 041 7/02

ОПИСАНИЕ ИЗОБРЕТ

Н ABTOPCNOMIV СИИДИтНЬСтвм

ГОСУДАРСТВЕННЬЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (6Ц 536613., (2:13 .ЗЭК 174/Х8-СЮ (22) 04. 08,83. (46): ЗО.05.83 Бюл.. М 20 (72 j -С,:"Аа Гщщевич . (7 Ц МинсщФ :рцйотехнический институт (83) 821.394 662(088.8) (56) 3.+ Авторское свидетельство СССР

"l4 836613: клф Н О4 1. 7/02, 1977

,(пРЫ ). (54у (87) УСТРОЙСТВО СИИ(РОНИЗА

ЯИИ СИГНАЛОВ по авт ° св. И 53663.1, о т л. и ч а ю щ е е с я тем,что, с пелью

- повыщения помехоустойчивост) введены

" 1последовательно соединенные анализатор апибок синхронизайии и коммутатор, а тек)ке элемент ИДИ, при этом. выходы реверсивного скетчика ерез коммутатор и, ного управители и анализатора ошибок

Ф которого пащипочен выид зиемента ИДИ, другой вхсщ и выход щиийизатора ошв бок синхронизании- соева)еии с соответствующими выходом и входом бежа перезаписи кс)да, причем:к вещам.элемен та ИДИ п щключекы с со- . ответствующий выход акализатора о)ии бок синхронизации, соотнетствушиий вход. анализатора ошибок синхрокизапии и соответствуюн)ий влхщ фсфмиреватели импульсов перезаписи и продвижения, который является входом сиг)м)ла управлен ия. ° ф

1 1021005 2

50

Изобретение относится к радиотехни: ке и технике связи и может ислользоваться в многоканальных системах передачи информации с временным разделением каналов для тактовой синхронизации.

По основному авт. св. ¹ 53661,1 известно устройство синхронизации curl ° .йалов, содержащее последовательно соединенные блок для выделения сигналов синхронизации, фазовый дискриминатор, 10 реверсивный счетчик, первый управитель и управляемый делитель,, первый выход которого подключен к другому входу фазового.пискриминатора ., второй выход и установочный вход каждого разряда управляемого делителя через блок перезаписи кода соединены с соответствующим входом и выходами кольцевого регистра, входы продвигающих импульсов которого и управляющие входы блока перезаписи кода соединены с соответствующими выходами формирователя импульсов перезаписи и продвижения, к входу которого подключен выход первого

25 делителя, к входу которого подключен с оответствующий вход первого управителя непосредственно, а выход генераторачерез второй управитель, к другим входам . которого подключены выходы реверсивного счетчика через последовательно соеди- 30 ненные ключ и интегратор, к соответствующему входу которого подключен выход первого делителя через второй делитель(А)

Однако известное устройство облада ет низкой помехоустойчивостью, 35

Цель изобретения - повышение помехоустойчивости.

Поставленная цель достигается тем, что в устройство синхронизации сигналов, содержащее последовательно соединенные 40 блок для выделения сигналов синхронизации, фазовый дискриминатор, реверсивный счетчик, первый управитель и управ- ляемый делитель, первый выид которого подключен к другому входу фазового 45 ди=криминатора, второй выход и установочный вход, каждого разряда управляемого делителя через блок перезаписи кода соединены с соответствующим вхо дом и выходами кольцевого регистра, входы продвигающих импульсов которого и управляющие входЫ блока перезаписи кода соединены с соответствующими вы-, ходами формирователя импульсов перезаписи и продвижения, к входу которого подключен выход первого делителя, к входу которого подключен соответствующий вход первого управителя непосредственно, а выход генератора - через второй управитель, к другим входам которого подключены выходы реверсивного счетчика через последовательно соединенные ключ и интегратор, к соответствующему входу которого подключен выход первого делителя через второй делитель, введены последовательно соединенные анализатор ошибок синхронизации и коммутатор, а также элемент ИЛИ, при этом выходы реверсивного счетчика через коммутатор соединены с обьединенными входами первого управителя и анализатора ошибок синхронизации, к установочному входу которого подключен выход элемента ИЛИ, другой вход и выход анализатора ошибок

1 синхронизации соединены с соответствующими выходом и входом блока перезаписи кода, причем к входам элемента ИЛИ подключены соответственно соответствуюа щий выход анализатора ошибок синхронизации, соответствующий вход анализатора ошибок синхронизации и соответствующий вход формирователя импульсов перезаписи и продвижения, который является входом сигнала управления.

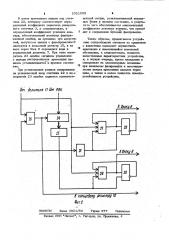

На фиг. 1 и 2 представлена структурная ! электрическая схема устройства синхронизации сигналов.

Устройство синхронизации содержит блок 1 для выделения сигналов синхронизаики, фазовый дискриминатор 2, ревереивный счетчик 3, генератор 4, первый и второй управители 5 и 6, управляемый делитель 7, блок 8 перезаписи кода, формирователь 9 импульсов перезаписи и продвижения, кольцевой регистр 10, первый и второй делители 11 и 12, ключ 13, интегратор 14, коммутатор 15, элемент ИЛИ 16 и анализатор 17 ошибок синхронизации,. состоящий из дешифраторов 18-20, элемента ИЛИ 21, счетчика 22 и измерителя 23 ошибок, причем формирователь 9 состоит из счет чика 24, дешифратора 25, элементов И 26-28, ЗК-гетеров 29 и 30 и . инвертора 31.

Устройство работает следующим образом.

На вход фазового дискриминатора поступает опорный сигнал и сигнал с выхода блока 1 для выделения сигналов синхронизации. Сигнал рассогласования с выхода фазового дискриминатора 2 поступает на реверсивный счетчик 3, осуществляющий его усреднение, Импульсы с выхода реверсивного счетчика 3 через коммутатор

15 поступают на ищды первого управителя 5, осуществлякпцего добавление импуль3 10210 сов или их исключение иэ последовательности, поступающей на вход первого упра вителя 5 с выхода генератора 4 через второй управитель 6. С выхода первого управителя 5 импульсы поступают на управляемый делитель 7, который понижает частоту высокочастотной последовательности до тактовой частоты сигнала, формируя таким образом опорный сигнал.

При этом в каждом временном канале !О за определенный промежуток времени устраняется фазовое рассогласование между опорным и принимаемым канальным сигналом,. т,е. устанавливается синхронный,.режим. Этому состоянию соответствует определенный фазовый сдвиг между эталонным сигналом на выходе первого делителя 11 и опорным сигналом на выходе управляемого делителя 7, которому соответствует опред,ленный код управляемого делителя 7 в моменты появления импульсов на выходе первого делителя 11. Этот код в конце кайального интервала заносится в кольцевой регистр 10 импульсом записи кода, по- р5 ступающим с выхода формирователя 9, Для этого от распределителя временных каналов в конце временного канала на установочный вход счетчика 24 подается импульс, устанавливающий его в нулевое . состояние. При этом потенциалом с дешифратора 25 открываются элементы

И 26 и 28, а со входа уст;ановки триггера 30 снимается сигнал установки нуля. В результате этого импульс с первого делителя 11 через элемент И 28 поступает на вход блока 8 перезаписи кода, заносит код управляемого делителя -7 в кольцевой регистр 10 и опрокидывает К-триггер 30, с выхода которого на вход элемента И 28 подается

40 сигнал запрета. Продвижение информации в кольцевом регистре 10 осущес1вляется импульсами с выхода элемента И 26, поступающими одновременно на счетчик 24, При- поступлении на вход счетчика 24 числа импульсов, соответствующих длине заносимого кода s кольцевой регистр 10 э срабатывает дешифратор 25, в результате чего на элемент И 26 подается сигнал запрета, а на элемент И 27 и установоч-5О ный вход ЗК-триггера 29 высокий потенциал. Импульс с вьмодй первого pemrтеля 11, пройдя элемент И 27, производит зались кода из кольцевого регистра

10 в управляемый делитель 7 и опроки- SS дывает ЗК-триггер 29, сигналом с выхода которого закрывается элемент

И 27. Для нормального функционирования

05 4 формирователя 9 необходимо обеспечить опережение импульса записи кода в кольцевой регистр 10 и отставание импухъса записи кода в управляемый делитель 7 соответственно относительно перва.о и последнего импульса продвижения информации в кольцевом регистре на время надежного срабатывания логических элементов, что достигается введением необходимого числа элементов задержки

{например, инверторов).

Второй управитель 6 служит для приведения частоты опорного сигнала к тактовой частоте принимаемого сигнала. Импульсы управления вырабатываются интегратором 14, который осушествляет интегрирование величины фазового рассогласования на входе устройства и формирует импульсы управления, компенсирующие частотную расстройку генератора 4 относительно частоты принимаемого сигнала.

Э то позволяет устранить различие заломим наемого значения фазы опорного сигнала от фазы входно о сигнала за цикл.

Система с астатизмом второго порядка позволяет свести к нулю динамическую ошибку синхронизации, при постоянной частотной расстройке межиу входным и опорным сигналами. При этом величина флуктуационной ошибки синхронизации может был. оценена как разностЬ импульсов исклочения и добавления, поступающих на вход управителя 6 в стационарном режиме, что может быть оценено с помощью из-. мерителя 23 ошибок. При этом состоя- ние измерителя 23 ошибок в каждый момент врем ени соответствует фпуктуационной ошибке, а допустимая величина ошибки может быть зафиксирована с помощью дешифраторов 18 и 19, настроенt ных на соответствующие комбинации прямого и дополнительного кодов, Превышение допустимой ошибки указывает на необходимость уменьшения коэффициента усиления, что обеспечивается включением дополнительных разрядов реверсивного счетчика 3. Это осуществляется следующим образом. Сигнал с дешиф» раторов 18 и 19 через элемент ИЛИ 21 поступает на вход счетчика 22 и на ус тановочный вход измерителя 23 ошибок.

На одном из входов дешифратора 20 появляется сигнал, подключающий c Iloмощью коммутатора 15 дополнительный разряд счетчика 3. Этим же сигналом измеритель 23 ошибок. устанавливается в нулевое состояние.

1021005

, 3уивепя f1 Й 7 РВЕ

gus,2

ВНИИПИ Заказ 3921/50 Тираж 677 Подписное филиал ППП Патент, г. Ужгород, ул. Проектная, 4

В конце временного канала код сче чика 22, которому соответствует определенный коэффициент пересчета реверсивного счетчика 3, а следовательно, и определенный коэффициент усиления контура, обеспечивающий величину флуктуационной ошибки, на превыша цую допусти мой, импульсом записи с формироватепя 9 заносится в кольцевой регистр 10, а из него через блок 8 перезаписи кода в управляемый делитель 7. При этом изме- . ритель 23 ошибок сигнФюм управления с выхода распределителя временных za . нналов устанавливается в нулевое состояние.

При установлении режима синхронизма на установочный вход счетчика 22 и из мерителя 23 ошибок подается соответсъвуюший сигнал, устанавливающий указанные блоки в нулевое состояние, в результате чего обеспечивается максимальный коэффициент усиления контура, что приво4 дит к сокращению времени фазирования.

Таким образом, предлагаемое устрой-» ство синхронизации сигналов по сравнению с известным позволяет осуществить адаптацию к изменяющейся помеховой обстановке, а следовательно, повысить качественные характеристики устройства, и, в первую очередь, время вхождения в синхронизм по элементарным посылкам при начальном фазировании и восстановлении начала временных каналов через цикл, а также в целом повысить помехоустойчивость устройства.