Арифметическое устройство

Иллюстрации

Показать всеРеферат

АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО , содержащее сгавиговые регистры, сумматоры вычитатели, коммутирующие , причем выходы первого и второго сдаигрвых регистров соединены с информационными входами первого и второго коммутирующих блоков соответственно, управляющие входы которых подключены к входу управления началам итерации команды устройства, выходы первого и второго комму ти : 1сяцих блоков подключены к первым информационным входам первого и BiToporo сумматоров-и 1читателей соответственно , упра.вляюпше входы которых соединены с входами настройки на данную итерашю команды устройства, выходы перв|ого и втЬрогч), с мматоров-вьхчатателей подключены к первому и второму инфор апионным выходам ус1ройства соi ответственно, выход второго сумматоравычи та теля подключен к входу первого i сдвигового регистра, вход управления на-: : стрЫ1кой на угловую постоянную данной , итерации команды устройства соединен с первым информационным входом третьего : с мматора вычитателя, второй ин{)ормаци1 ОНШ|1Й вход которого соединен с выходом третьего сдвиговото регистра, вход которого соединен с третьим информационным выходом устройства и с выходом третьего сумматора вычитателя, о т л и ч а ю ш е е с я тем, что, с целью повышения бьютродействия и упрошения, первый . и второй информационные входы третьего коммутирующего блока подключены к вы- . ходам первого и второго сумматоров вычитателей соответственно, выход Т1 етьего коммугарующего блока соединен с входом второго сдвигового регастра, уп- ; равпяюшнй вход третьего комму-гарующеГо бя{жа соединен с входом управления яаправлешем коммутагши уст эойства, упреЁЬпякжшй вход третьего сумматора чвычвтателя подключен к входу настройки на данную итераш{ю команды устройства, втсрые (авонные входы первого : R торга о сумматоров-вычитагелей подЕспючены к выходам ътораго и первого слаигогаых регистров соответственно.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

gpss (л 06 F 7/38

ЮСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И.ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИ

К ABTOPCHQMY СВИДЕТЕЛЬСТВУ (21) 3399279/18-24 (22) 17,02.82 (46) 07.06.83. Бкп. N 21 (72) Н." И. Вираховский, О. Н. Чемезов и А. М. Никитин (71 ) Рязанский радиотехнический институт (53) 681,3(088.8) (56) 1. Патент Великобритании Nñ 1331410, кл. G 4А, 1973."

2. Авторское свидетельство -СССР

N 796844, кл. G 06 F 7/38, 1979 (прототип). (54) (57) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО, содержашее сдвигоиые регистры, сумматоры вычитатели, коммутирующие блоки, причем выходы первого и второго . сдвиговых регистров соединены с информационными входами первого и второго коммутируюших блоков соответственно, управпяюшне входы которых подключены к входу управления началом итерации команды устройства, выходы первого и второго коммутируюших блоков подключены к первым информационным входам первого и второго сумматоровчьычитателей соответственно, управляюшие входы кото» рых соединены с входами- настройки на данную итерацию команды устройства, выходы первого н второго, су мматоров- вычи тателей подключены к первому и второму

„.Яны 1022152: A информационным выходам устройства соответственно, выход второго сумматора= вычитателя подключен к входу первого

:: сдвигового регистра, вход управления на-.

: стройкой на угловую постоянную данкой . итерации команды устройства соединен с первым информационным входом третьего сумматора=вычитателя, второй информаци ;:. онный вход которого соединен с выходом

: третьего сдвигового регистра, вход которого соединен с третьим информационным выходом устройства и с выходом третьего сумматора-вычитателя, о т л и ч а.— ю ш е е с я тем, что, с целью повыше- ния быстродействия и упрошення, первый и второй информационные входы третьего коммутирующего блока подключены к вы- . Е ходам первого и второго сумматоров-вычитателей соответственно, выход треть»

его коммутируюшего блока соединен с входом второго сдвигового регистра, управляюший вход третьего коммутируюше- P . го блока соединен с входом управления направлением коммутации устройства, уп- . равляющий вход третьего сумматора-вычитателя- подключен к входу настройкй на данную итерацию команды устройства, вторые информационные входы первого и,второго сумматоров-вычи тателей подключены к выходам вторжо и первого сдвиговых. регистров соответственно. Ci7l

3Я

1022152

Изобретение относится к вычислитель. ной технике и предназначено для постро- ения на его основе специализированных 118M.

Известно арифметическое устройство, реализующее алгоритм Воддера

1+1 х „-.„=х;+ „ Г Ч„", 9„„=S„.+ ;av cc6g Г" (<<) и позволякнцее вычислить

: — х -.к -/х + и и

e=C Ctq(V0/X,), () 10

k,> — коэффициент общего удлинения вектора, равный произведению коэффициентов удлинения на каждой итерации а

v,„h", „ Ó (4.I

30 — номер итерации, Хр g0 - начальные данные.

Это арифметическое устройство. содержит три сдвиговых регистра, три сумма- . тора=вычитателя и два коммутирующих блока Pl ).

Недостатком данного устройства является изменение масштаба результатов вычислений.

Наиболее близким к предлагаемому по технической сущности является арифметическое устройство, содержащее три сдви.— : . говых регистра, четыре коммутирующих блока, семь сумматоров-вычитателей. Этб 45 устройство производит коррекцию масштабов результатов на каждой интерации 2), Недостатксм известного устройства являвтся большой объем оборудования, Кроме того, введение коррекции на каж. дой итерации снижает быстродействие устройства.

Цель изобретения - повышение быстродействия н упрмцение устройства путем использования. для коррекции масштабов результатов имеющегося оборудования.

Поставленная цель достигается тем, что в арифметичвском устройстве, содержащем сдваговые регистры, суммато4 где Х1 JJ g.— значения координат и угла

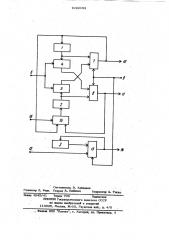

1I на 1 -й итерации; . — фуякяия, показывающая направление вращения и рав- 20 ная „=ЩИ 3„, ():, ры-вычитатели, коммутирующие блоки, причем выходы первого и второго сдвиговых регистров соединены с информационными входами первого и второго коммутирующих блоков соответственно, управляющие входы которых подключены к входу управления началом итерации команды устройства, выходы первого и второго коммутирующих блоков подключены к первым информационным входам первого и второго сумматоров-вычитателей соответственно, управляющие входы которых соединены с входами настройки на данную итерацию команды устройства, выходы первого- и второго сумматоро вычитателей подключены к первому и втЬрому информационным выходам устройства соответственно, выход второго сумматора=Ъы-. читателя подключен к входу первого сдвигового регистра, вход управления настройкой на угловую постоянную данной;;цтерации команды устройства соединен с первым информационным входом третьего сумматора-вычитателя, второй информационный вход которого соединен с выходом третьего сдвигового регистра, вход которого соединен с третьим информационным выходом устройства н с выходом третьего сумматораьаычитателя, первый и второй информационные входы третьего коммутирующего блока подключены к выходам первого и второго сумматоров=.вычитателей соответственно, выход третьего коммутирующего блока соединен с входом второго сдвигового регистра, управляющий вход третьего коммутирующего блока соединен с входом управления направлением коммутации устройства, управляющий вход третьего сумматора-вычитателя подключен к входу настройки на данную итерацию команды устройства, вторые информационные входы первого и второго сумматоров-аычитателей подключены к выходам второго и первого сдвиговых регистров соответственно., На чертеже представлена структурная схема арифметического устройства.

Устройство содержи т сдвиговые регистры 1-З, коммутирукнпие блоки - 4 и 5, вход 6 управления началом итерации, команды устройства, сумматоры=вычитатели 7.и 8, вход 9 настройки на данную итерацию команды устройства, первый и второй выходы 10 и 11 устройства, вход

12 уцравления:,настройки на угловую постоянную данной итерации. команды устрой ства, третий сумматор-вычитатель 13, трезв выход 14 устройства, коммутатор

3 . 1022

15, вход 16 управления направлением коммутации устройства.

На первых Р итерациях устройство реализует алгоритм (1). После этого устройство в течение трех дополнительных итераций производит следующие опе-. рации у, (g- +g 4) (Х .„ .= 4 2. ) Хи+1

Х"„;„(-L) X„„„, что равносильно умножению значения

На коэффициент allttpoKGHMattHH К, =

= 0,6069946.

Так как 15 К ц =0, 06994 6.. к„„=-,", С И на выходе устройства модуль комплекс- рО ного числа получается без удлинения в

КИ раз, Ошибка, получаемая при вычислении, .определяется по формуле

25 и уменьшается с ростоМ числа итераций.

Например, & q =1,0762 .10: 1, 1а 2 О>

4 =4,6678- 10 „4=0,946- 2 . Е =4, 25&j 3

° lO =0,87 ° .2

Устройство работает следующим образом.

Текущие значения координат )(и уо хранятся в соответствующих регистрах.

Угол Во =О. С .началом очередной ите . . 35 рации по команде из устройства управления, поступающей по входу 6, на выходах коммутирующих блоков 4 и 5 при сдвиге информации в регистрах 1 и 2 по-, являются операнды сдвинутые на t раз-рядов вправо (в сторону младших). На управляющие входы сумматоров-вычитателей 7, 8 и 13 из устройства управле-. ния по входу 9 поступает потенциал, соответствующий оператору. 8 s соответствии с котврым сумматоры-вычитатели настраиваются на выпапненяе итерации, Значение X +,рполучаюшееся на выходе сумматора-вычитателя 7 поступает

152 4 на выход 10 устройства H Ha вход ре гистра 1 для записи в него и выполнения следующей итерации.

Аналогично координате Х„ „ на выходе ,сумматора-вычитателя 8 получается знаI чение координаты У + подаваемое на выход 11 устройства для определения )<+< и на первый вход третьего коммутатора

15, на управляющие входы которого из устройства управления поступает потенциал 16, коммутирующий первый вход блока третьего коммутатора.

Одновременно текущее значение угла с выхода регистра 3 поступает на вход сумматора-вычитателя 13, где в соответствии с „ к нему прибавляется (вычитается) угловая постояннаяa)"сф2 > поступающая из запоминающего устройст4ва по входу 12. 6 -. + с выхода сумматора-вычитателя 13 записывается в регистр 3 и подается на выход 14 устройства.

Затем процесс повторяется до набора заданного чиспа итераций, и на выходе ,устройства появляются результаты, соот:: ветствующие (2).

После этого устройство производиткоррекцию масштаба модуля комплексного числа, . для чего Hà вход регистра 1 и на второй вход третьего коммутатора поступает значение Х На управляющие входы третьего коммутатора 15 из устройства управления поступает потенциал, коммутирующий второй вход этого блока.

После этого устройство в течение трех дополнительных итераций реализует алгоритм (5).

Предлагаемое устройство- позволяет уменьшить аппаратурные затраты по срав- нению с прототипом на 4 у. одноразрядных. сумматоров и 1,5 3 одноразрядных коммутаторов, где V - число разрядов числа.

При этом повышается быстродействие по сравнению с устройством-прототипом на (28-3) " у,, где. и- число основных итераций; ® — время одного суммирования.

1022152

Составитель В. Кайданов

Редактор Л. Филь Техред А. Бабинен Корректор А. Тяско

Заказ 4045/41 Тираж 706 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений н открытий

113035, Москва, Ж-35, Раушская наб., д.-4/5

Фнлиаи ППП Патент", r. Ужгород, ул. Нроектиаи, 4