Логическое запоминающее устройство

Иллюстрации

Показать всеРеферат

, SU.„a 022220

СОЮЗ СОВЕТСКИХ

Э

РЕСПУБЛИК G 11 С 15/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТЮЬПЪЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

l (21) 3405155/18-24 (22) 02.03.82 (46) 07.06.83. Бюл. И 21 (72) Г.К. Алдабаев, К.И. Диденко, А.Н. Кокарев, А.Г. Перекрестов и А.А. Ручинский (71) Научно-производственное объединение по системам автоматизированного управления (53) 681.327 (088.8) (56) 1. Авторское свидетельство СССР

N 524224, кл. G 11 С 15/ОО, 1 76.

2, Авторское свидетельство СССР и 501421, кл. G 11 С 15!00, 1976 (прототип). (54)(57) ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ

УСТРОЙСТВО, содержащее блок памяти, элементы И, элементы ИЛИ и элемент

НЕ, причем один из адресных входов блока памяти подключен к выходу пер-вого элемента ИЛИ, первый и второй входы которого соединены соответст.венно с выходами первого и второго элементов И, первые входы которых подключены к управляющему входу блока памяти, информационный вход которого соединен с выходом второго элемента ИЛИ, первый и второй входы которого подключены соответственно к выходам третьего и четвертого элементов И, первый вход третьего элемента И соединен с вторым входом второго элемента И и является информационным входом устройства, первый вход четвертого элемента И подключен к выходу элемента НЕ, вход которого является управляющим входом устройства, входом записи которого является управляющий вход блока памя ти, о т л и ч а ю щ е е с я тем, что, с целью расширения его функциональных возможностей за счет реализации функции самоблокировки после записи информации в ячейку памяти устройства, в него введены дешифратор, третий элемент ИЛИ и пятый элемент И, причем первый выход дешифратора соединен с первым входом треть- Я его элемента ИЛИ, третьим входом второго элемента И и .вторым входом четвертого элемента И, второй выход дешифратора подключен к вторым.входам первого и третьего элементов

И и второму входу третьего элемента

ИЛИ, выход которого соединен с пер- ваа вым входом пятого элемента И, выход которого подключен к третьему входу фф первого элемента ИЛИ, второй выход р пятого элемента И является входом Ю чтения устройства, входы дешифратора © соединены с другими адресными входами блока памяти и являются адрес- 4Р ными входами устройства, выходом которого является выход блока памяти.

1022220!

20

30

40

50

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть применено в комплексах программно-ло гического управления технологическими процессами и агрегатами, работающими по циклическим программам.

Известно логическое запоминающее устройство, содержащее блоки памяти, каждый из которых хранит определен" ное число одноразрядных слов 1J .

Недостатком устройства является ограниченность его функциональных возможностей.

Наиболее близким по технической сущности к предлагаемому является логическое запоминающее устройство, содержащее блоки памяти, элементы

ИЛИ, элементы И и элементы НЕ (2 j .

Известное устройство не реализует функцию самоблокировки ячейки памяти после занесения в нее информации, что ограничивает его функциональные возможности

Цель изобретения — расширение функциональных возможностей устройства за счет реализации функции само блокировки после записи информации в ячейку памяти устройства.

Поставленная цель достигается тем что в логическое запоминающее . устройство, содержащее блок памяти, элементы И, элементы ИЛИ и элемент

НЕ, причем один из адресных входов блока памяти подключен к выходу первого элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами первого и второго элементов И, первые входы которых подключены к управляющему входу блока памяти, информационный вход которого соединен с выходом второго элемента ИЛИ, первый и второй входы которого подключены соответственно к выходам третЬего и четвертого элементов И, первый вход третьего

Ф элемента И соединен с вторым входом второго элемента И и является информационным входом устройства, первый вход четвертого элемента И подключен к выходу элемента НЕ, вход которого является управляющим входом устройства, входом записи которого является управляющий вход блока памяти, введены дешифратор, третий .элемент ИЛИ и пятый элемент.И, при" чем первый выход дешифратора соединен с первым входом третьего элемента

ИЛИ, третьим входом второго элемента

И и вторым входом четвертого элемента И, второй выход дешифратора под" ключен к вторым входам первого и третьего элементов И и второму входу третьего элемента ИЛИ, выход которого соединен с первым входом пятого элемента И, выход которого подключен к третьему входу первого элемента

ИЛИ, втооой вход пятого элемента И является входом чтения устройства, входы дешифратора соединены с другими адресными входами блока памяти и являются адресными входами устройства, выходом которого является выход блока памяти.

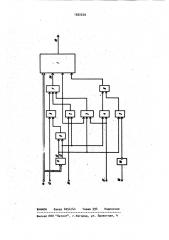

На чертеже представлена функциональная схема предлагаемого логичес" кого запоминающего устройства.

Устройство содержит блок 1 памяти, первый-пятый элементы И 2-6, первыйтретий элементы ИЛИ 7-9, элемент НЕ

10, дешифратор 11 с выходами 12 и 13.

На чертеже обозначены адресные входы 14, вход 15 чтения, вход 16 записи, информационный вход 17, управляющий вход 18 и выход 19 устройства, а также один из адресных входов 20 блока памяти, предназначенный для выбора кристалла блока памяти.

Устройство работает следующим образом.

Устройство может ° работать в двух режимах: в режиме реализации функции самоблокировки и в обычном режиме.

Режим работыустройства кодируется в адресе, который поступает с входов 14 устройства,единичйый сигнал на одном из выходов, например 12, дешифратора сопровождается нулем на другом его выходе, например 13. При этом при наличии единицы на выходе 12 дешифратора 11 реализуется режим самоблокировки, а при наличии единицы на выходе 13 — режим обычного оперативного запоминающего устройства, Работа устройства в зависимости от режима различна только при записи информации. Хранение и считывание . информации осуществляется идентично для обоих режимов.

Запись информации в режиме самоблокировки производится при наличии на входе 16 логической единицы, которая непосредственно поступает на управляющий вход блока 1 памяти, и логической единицы на входе 17 устройства, которая в сочетании с ло1022

220

3 гическими единицами с выхода 12 дешифратора 11 и входа 16 устройства приводит к появлению единицы на вы" ходе элемента И 3, которая через элемент ИЛИ 7 поступает на вход 20 блока 1 памяти. При этом для записи единицы в блок 1 памяти на вход 18 подается логический нуль, а для записи нуля - логическая единица. При логическом нуле на входе 18 .на выхо- 10 де элемента НЕ 10 появляется единица, . которая поступает на второй вход элемента И 5, на первом входе которого в рассматриваемом режиме присутствует единица с выхода 12 дешифратора 15

11. В результате с выхода элемента .

И 5 через элемент ИЛИ 8 на информационный вход блока 1 памяти поступает единица и записывается в нем. При логической единице на входе 18 на вы- о ходе элемента НЕ 10 устанавливается нуль, который через элемент И 5 и элемент ИЛИ 8, на первом входе которого присутствует нуль с выхода элемента И 4, поступает на информацион- 25 ный вход блока 1 памяти и записывается в нем.

Запись информации в режиме обычного запоминающего устройства производится при наличии на входе 16 ло- 30 гической единицы, которая непосредственно поступает на управляющий вход блока 1 памяти и на один иэ входов элемента И 2, на втором входе которого присутствует единица, поступающая в этом режиме с выхода 13 дешифрато35 ра 1I. -На выходе элемента И 2 при, этом присутствует единица, которая через элемент ИЛИ 7 поступает на вход 20 блока 1 памяти. Записываемая 4О информация в виде логических единиц и нулей поступает с входа 17 на один из входов элемента И 4. Так как на другом входе элемента И 4 в этом режиме постоянно присутствует едини45 ца с выхода 13 дешифратора 11, то при логической единице на входе 17 . на выходах элемента И 4 и элемента

ИЛИ 8 и информационном входе блока

1 памяти устанавливается единица, которая записывается в блок 1 памяти.

При логическом муле на входе 17 устройства на информационном входе блока -1 памяти устанавливается нуль, который записывается в.нем.

Считывание информации в обоих режимах. происходит при наличии логической единицы на входе 15, логического нуля на входе 16, поступающе" го непосредственно на управляющий вход блока .1 памяти, переводя его в режим считывания, и логической единицы на одном из выходов дешифратора 11, которая через элемент

ИЛИ 9 поступает на второй вход элемента И 5, на первый вход которого поступает логическая единица с входа 15 устройства. При этом единичный сигнал с выхода элемента И 6 через элемент. ИЛИ 7 поступает на вход

20 блока 1 памяти, Считанная информация с блока I памяти поступает на выход 19 устройства.

Таким образом, при работе устройства в режиме самоблокировки, в отличие от обычного режима, смена содержимого памяти невозможна после исчезновения логической единицы на его информационном входе 17, так как при этом доступ к содержимомублока 1 памяти заблокирован логическим нулем с выходом элемента ИЛИ 7, на входы которого при этом поступают логические нули с выходов элементов .

И 3, 2 и 6.

В предлагаемом устройстве реализуется функция самоблокировки после записи в него информации, за счет чего расширяются его функциональные возможности по сравнению с прототипом.

1022220 ВНИИПИ Заказ 4054/44 Тираж 594 Подписное филиал ППП "Патент", г.Ужгород, ул. Проектная, 4