Запоминающее устройство с автономным контролем

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

ОД М

РЕСПУБЛИК (19) (И) у5р G 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ . К. АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЦТИЙ

21) 3281405/18-24

° °

22 ) 29.04,81 (46 ) 0 7. 06. 83. Бюл . и 2.1 (72) Г. А. Бородин, Н,И. Егорова и

А. К. Столяров (71). Московский ордена Ленина и ордена Октябрьской Революции энергетический институт (53) 681 327(088.8)

"(56 ) 1. Патент СВА К 3573728, кл. 340-146.1, опублик. 1971 .

2. Патент Великобритании

N 1391976, кл. G 4 A,î()óáëèê.1975 (прототип). (54)(57) ЗАПОИИНАЮЦЕЕ УСТРОЙСТВО С

АВТОНОИНЫИ КОНТРОЛЕИ; содержащее блоки памяти, входные и выходные формирователи четности, схему сравнения, одни входы которой подключены к выходам выходных формирователей четности, другие соединены с контрольными выходами блоков памяти, контрольные входы которых подключены к выходам входных формирователей четности, одни из вхо- . дов которых и информационные входы блоков памяти объединены.и являются информационными входами устройства, информационными выходами которого являются информационные выходы блоков памяти, соединенные с одними из входов выходных формирователей четности, о т л и ч а ю.щ е е с я-тем, что, с целью упрощения устройства, в него введены группы элементов И, ИЛИ и ИЛИ-НЕ, причем входы элементов ИЛИ-НЕ и ИЛИ и адни из входов элементов И первых групп соединены с информационными входами устройства, другие входы входных формирователей четности подключены соответственно к выходам элементов ИЛИ-НЕ первой группы и элементов ИЛИ второй группы, входы которых соединены соответственно с -выходами элементов ИЛИ-НЕ первой группы и элементов И первой .группы, другие входы которых соединены с вы- . а ходами элементов ИЛИ первой группы, входы элементов ИЛИ третьей групры и элементов ИЛИ-НЕ второй группы и одни из входов элементов И второй группы соединены с информационными выходами устройства, входы элементов

ИЛИ четвертой группы подключены соответственно к выходам элементов

ИЛИ-НЕ второй группы и элементов И второй группы, другие входы которых соединены с выходами элементов ИЛИ третьей группы, другие входы выходных .формирователей четности под- ключены соо ветственно к выходам элементов ИЛИ-НЕ второй группы и элементов ИЛИ четвертой группы.

1022223

Изобретение относится к запоминающим устройствам и может быть использовано в запоминающем устройстве с об наружением пакетных ошибок, Известно запоминающее устройство с автономным контролем, которое содержит блоки памяти, формирователи контрольных разрядов кода Хэмминга, формирователи проверочного слова, де10 шифратор одноразрядных ошибок (1).

Недостатком этого устройства является невозможность обнаружения па,кетных ошибок, которые могут возникнуть при отказе многоразрядных панелей памяти, а также зависимость количества проверочных разрядов от количества информационных разрядов, Наиболее близким к предлагаемому является запоминающее устройство, состоящее из И четырехразрядных модулей памяти, блок обнаружения ошибок, сосстоящее из Й схем контроля по четности, и обнаруживающее все ошибки при отказе модуля памяти, т.е. до 4 разрядов. В блоке обнаружения ошибок

25 легко получается сигнал общей четности 1 21.

Недостатком известного устройства является большая ее избыточность в проверочных разрядах, а имен- ЗО но необходимо иметь количество проверочных разрядов, равное возможной кратности ошибок, что усложняет устройство.

Цель изобретения - упрощение уст- 35 ройства за счет уменьшения количества проверочных разрядов, необходимых для обнаружения многоразрядных ошибок.

Указанная цель достигается тем, что в запоминающее устройство с авто" 40 номным контролем, содержащее блоки памяти, входные и выходные формирователи четности, схему сравнения, одни входы которой подключены к выходам выходных формирователей чет- 45 ности, другие соединены с контрольными выходами блоков памяти, контрольные входы которых подключены к выходам входных, формирователей четности, одни из входов которых и ин- 50 формационные входы блоков памяти объединены и являются информационными входами устройства, информационными выходами которого являются информационные выходы блоков памяти, соеди- 55 ненные с одними из входов выходных формирователей четности, введены группы элементов И, ИЛИ и ИЛИ-НЕ,причем входы элементов ИЛИ-НЕ, ИЛИ и одни из входов элементов И первых групп .соединены с информационными входами устройства, другие входы входных фор» мироеателей четности подключены соот- ветственно к выходам элементов ИЛИ-HE первой группы и элементов ИЛИ второй группы, входы которых соединены соответственно с выходами элементов ИЛИ-НЕ первой группы и элементов И первой руппы, другие входы которых соединены с выходами элементов ИЛИ первой группы, входы элементов ИЛИ третьей группы и элементов ИЛИ-HE второй группы и одни иэ входов элементов И второй группы соединены с информационными выходами устройства, входы элементов ИЛИ четвертой группы подключены соответ-. ственно к выходам элементов ИЛИ-HE второй группы и элементов И второй группы, другие входы которых соединены с выходами элементов ИЛИ третьей группы, другие входы выходных формирователей четности подключены сооТ ветственно к выходам элементов ИЛИ-НЕ второй группы и элементов ИЛИ четвера îé группы.

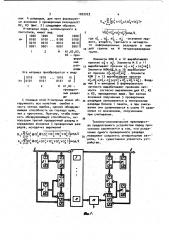

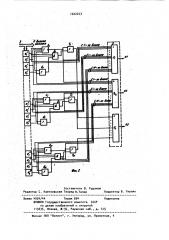

На фиг. 1 изображена структурная схема запоминающего устройства с as" тономным контролем; на фиг, 2 - схема процесса формирования проввроч« ных разрядов.

Устройство содержит (фиг . l ) И четырехразрядных блоков 1 памяти, информационные входы которых являются информационными входами 2 устройства, входные формирователи 3 четности, первые группы элементов ИЛИ-НЕ А, И 5 и ИЛИ 6, вторую группу элементов

ИЛИ 7. Информационные выходы блоков 1 памяти являются информационными выходами 8 устройства. Устройство также содержит выходные формирователи 9 четности, вторые группы элементов

ИЛИ-HE 10 и И ll, третью и четвертую группы элементов ИЛИ 12 и 13, схему

14 сравнения.

Устройство работает следующим образом, По входам 2 на И четырехразрядных блоков 1 памяти поступает двоичный код числа, подлежащего записи в очередном цикле записи. Поскольку запоминающее устройство с автономным контролем предназначено для õðàнения кодов чисел в четырехразрядных блоках памяти, из которых набирается слово требуемой разрядности, то необходимо сформировать код, позволяющий обнаруживать все ошибки в преде4

1022223

3 лах 4 разрядов, для чего формируются значения 3 проверочных разрядовKl

К2, К3 (фиг. 2) следующим образом.

Н-матрица кода, используемого в поототипе, имеет вид

Н=

3000 . 3000 3000

0300 0300 ... 0100

0030 0030 0010

0001 0001 . 0001

0001

К. =7 o"„ло л(о чО )ч

5 ч(а ча ча1чаДмад1

\ где а „, а, сР, ач -значения первогo, второго, третьего и четвертого информационных разрядов в каждой группе иэ И четырехразрядных

1 2 М Kl К2К3, К4 - проверочные раэ- 35 ряды

Эта матрица преобразуется к виду

1010 1010 ... 1010 10

H- =0101 0301 . 0101 Ol

1 2 М Kl,К2 проверочные разряды

С помОщью этОЙ H-матрицы мОжно Об- у5 наруживать все нечетные ошибки и часть четных ошибок, однако обнаруживающая способность ее гораздо хуже., чем у прототипа. Поэтому, чтобы повысить обнаруживающую способность, используем третий проверочный разряд и определяем значения 3 проверочных разрядов, исходя из выражений к =E(а" ео" 6 (а ча và" ча ))мода

3 1=1 1 3 1 2- Ъ 4 351 к =У(а ао,, (аÄva va ча" ) мод 2

< =1

rpynn.

Элементы ИЛИ 6 и 12 вырабатывают признак a 1 v а 1. Элементы М 5 и 11 вырабатывают признак е"„ ла A (а"че+ ).

Элементы ИЛИ-Н 4 и 10 вырабатывают признак a„qa va>va+, Элементы

" !" 13 . "у чу а „ б" л(а ч сыч(а„ ч а v а ч а ) . Входг нйе 3 и выходные 9 формирователи четности вырабатывают признаки четности согласно выражениям для Кl, К2 и К3, приведенным выше . При записи значения полученных 3 проверочных разрядов записываются в контрольные разряды блоков 3 памяти, à при считывании они сравниваются а схеме 34 сравнения со значениями, полученными при считывании .

Технико-экономическое преимущество предлагаемого устройства перед про тотипом заключается в том, что устра- нение одного проверочного разряда

3 позвопяет сократить аппаратурные зат-: раты, т.е . существенно упростить устройст во.

1022223

Составитель В. Рудаков

Редактор С. Квятковская Техред И.Тепер

Корректор В. Гирняк

Ю М

М Ю 0 А

Подписное филиал ППП "Патент", г. Ужгород, ул, Проектная, 4

Заказ 4054/44 Тираж 594:

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иоеква, Ж-35, Раушская наб., д. 4/5