Устройство для вычисления логарифмов двоичных чисел

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМОВ ДВОИЧНЫХ ЧИСЕЛ , содержащее два регистра, группу элементов 2И-ИЛИ, вход устройства соединен с входом первого регистра, инверсный выход второго регистра подключен к первому информационному входу группь элементов 2И-ИЛИ, отличающееся тек,что, с целью повышения быстродействия в него дополнительно введены три регистра, четыре сумматора, генератор тактовых импульсов . Триггер и (и-2) вычислительных блоков итерации, где V) - разрядность входного числа, причем выход i -го разряда первого регистра соединен с входом (i+2)-разряда второго регистра, второй информационный вход группы элементов 2И-ИЛИ подключен со сдвигом на два разряда вправо к вьЕходу л -го разряда третьего регистра , прямой выход первого разряда которого соединен с первым управляющим входом группы элементов 2И-ИЛИ, второй управляющий вход которой подключен к инверсному выходу первого разряда третьего регистра, выход i-го разряда первого регистра соединен с первым входом U+1.)-разряда и с вторым входом i-го разряда первого .сумматора, выход которого подключен к информационному входу третьего регистра , выход которого соединен с первым информационным, входом второго Сумматора, второй информационный вхЪд которого подключен к выходу группы элементов 2И-ИЛИ, инверсный выход первого разряда третьего регистра соединен с первым входом третьего сумматора , инверсный выход триггера подключен к первому входу четвертого сумматора , второй вход которого соединен с выходом четвертого регистра, выход четвертого сумматора через пятый регистр подключен к выходу устройства , в каждом вьлчислительном блоке итерации, содержащем три регистра, группу элементов 2И-ИЛИ и два сумматора , инверсный выход первого регистт ра соединен с первым информационным . входом группы элементов 2И-ИЛИ, вы- § ход i -го разряда ВТОРОГО регистра сое-; динен с первым информационным входом первого сумматора и c(-i + j +2 -разрядом второго информационного входа группы элементов 2И-ИЛН, где - l,2,...,m(i- номер разряда регистра ) , 1, 2,.,. ,И ()- номер вычислительного блока итерации), выход группы элементов 2И-ИЛИ подключен к второму информационному входу первого сумматора, первыйуправляющий вход группы элементов 2И-ИЛИ соединен с прямым выходом первого разряда второго регистра-, инверсный . вьдход которого подключен к второму управляющему входу группы элементов 2И-ИЛИ и первому входу второго, сумматора, второй вход которого соединен с выходом третьего регистра, кроме того вь;ход i -го разряда группы элементов 2И-ИЛИ устройства соединен с входом (-1 +1 )-го разряда первого регистра первого вычислительного блока итерации, выходы второго и третьего сумматоров устройства подключены соответственно к входам второго и третьего регистров первого вычислительного блока итерации, выход i -го разряда группы элементов 2И-ИЛИ предыдущего вычислительного .

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

4 А (19) (1??

Ъ(5В С 06 F 7 556 л

ОПИСАНИЕ ИЗОБРЕТЕНИ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

fl0 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 33450 37/18-24 (22) 08.10 ° 81

-. (46) 15. 06. 83. Бюл. 9 22 (7 2) A.À. Мель ник. (71) Львовский ордена Ленина политехнический институт им;Ленинского комсомола (53) 681.325(088.8) (56) 1. Авторское свидетельство СССР

Р 448459, кл. G 06 F 7/556, 1974 °

2. Данчеев В.П. Цифро-частотные вычислительные устройства. N., "Энергия", 1976, с . 61 (прототип). (54)(57) УСТРОИСТВО ДЛЯ ВЫЧИСЛЕНИЯ

ЛОГАРИФМОВ ДВОИЧНЬИ ЧИСЕЛ, содержащее два регистра, группу элементов

2И-ИЛИ, вход устройства соединен с входом первого регистра, инверсный выход второго регистра подключен к первому информационному входу группь. элементов 2И-ИЛИ, о т л ич а ю щ е е с я те .,что, с целью повышения быстродействия в него дополнительно введены три регистра, четыре сумматора, генератор тактовых импульсов, триггер и (н -2) вычислительных блоков итерации, где ?1 - разряд- ность входного числа, причем выход

-го разряда первого регистра соединен с входом (+2)-разряда второго регистра, второй информационный вход группы элементов 2И-ИЛИ подключен со сдвигом на два разряда вправо к выходу 1 -го разряда третьего регистра, прямой выход первого разряда которого соединен с первым управляющим входом группы элементов 2И-ИЛИ, второй управляющий вход которой подключен к инверсному выходу первого разряда третьего регистра, выход -го разряда первого регистра соединен с, первым входом (м+1,)-разряда и с

:вторым входом 1-го разряда первого сумматора, выход которого подключен к информационному входу третьего регистра, выход которого соединен с первым информационным входом второго сумматора, второй информационный вход которого подключен к выходу группы элементов 2И-ИЛИ, инверсный выход первого разряда третьего регистра соединен с первым входом третьего сумматора, инверсный выход триггера подключен к первому входу четверТого сумматора, второй вход которого соединен с выходом четвертого регистра, выход четвертого сумматора через пятый регистр подключен к выходу устройства, в каждом вычислительном блоке итерации, содержащем три регистра, группу элементов 2И-ИЛИ и два сумматора, инверсный выход первого регистт ра соединен с первым информационным . входом группы элементов 2И-ИЛИ, выФ ход i -го разряда второго регистра сое-; .динен с первым информационным входом первого сумматора и с(+) +2)-разрядом второго информационного. входа группы элементов 2И-ИЛИ, где

1,2,...,в (1- номер разряда ре- Я гистра), j = 1,2,...,??(j- номер вычислительного блока итерации), выход группы элементов 2И-ИЛИ подключен к второму информационному входу первого сумматора, первый управляющий вход группы элементов 2И-ИЛИ соединен с прямым выходом первого разряда второго регистра, инверсный, выход которого подключен к второму Я управляющему входу группы элементов 2И-ИЛИ и первому входу второго. сумматора, второй вход которого соединен с выходом третьего регистра, кроме того выход 1-го разряда группы элементов 2И-ИЛИ устройства соединен с входом (4 +1 )-го разряда пер- : фи вого регистра первого вычислительного блока итерации, выходы второго и третьего сумматоров устройства подключены соответственно к входам второго и третьего регистров первого вычислительного блока итерации, выход

-го разряда группы элементов

2И- ИЛИ предыдущего вычислительного

1023324 блока итерации соединен с.входом (i+1)-го разряда первого регистра последующего вычислительного блока итерации, выходы первого и второго сумматоров предыдущего вычислительного блока итерации подключен соответственно к входам второго и третьего регистров последующего вычислительного блока итерации, выход первого разряда первого сумматора (и -2)-ro вычислительного блока итерации соедиИзобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных ЦВИ для логарифмирования больших массивов многоразрядных чисел.

Известно цифровое устройство для логарифмирования двоичных чисел, содержащее два сумматора, сдвиговый регистр, схему И-ИЛИ, схему И, трег- ®

rep, запоминающий блок, блок управ.ления (13.

Недостатками известного устройства являются низкое быстродействие, а также необходимость хранения в памяти констант.

Наиболее близким к изобретению является устройство воспроизведения логарифмической и обратной зависимости, содержащее три регистра, 20 счетчик, две схемы И-.ИЛИ (2) ., (1 -—

Недостатком известного устройства является низкое быстродействие.

Цель изобретения - повышение быстродействия устройства. 25

Поставленная цель. достигаешься тем, что в устройство для вычисления лога рифмом двоичных: чисел, содержащее два регистра, группу элементов 2И-ИЛИ, вход устройства соединен с входом пер о вого регистра, инверсный выход второго регистра подключен к первому информационному входу группы элементов 2И-ИЛИ, дополнительно введены три регистра, четыре сумматора, генератор тактовых импульсов, триггер и (и -2 ) вычислительных блоков итерации, где и-. разрядность входного. числа, причем выход -го разряда первого регистра соединен с входом (i +2 ) разряда второго регист- 40 ра, второй информационный вход группы элементов 2И-ИЛИ подключен со сдвигом на два разряда вправо к выходу

-ro разряда третьего регистра, пря мой выход первого разряда которого соединен с первым управляющим входом группы элементов 2И-ИЛИ, второй управляющий вход которой подключен киннен с информационным входом триггера, выход второго сумматора (и -2)-го вычислительного блока итерации подключен к входу четвертого регистра устройства, второй вход третьего сумматора, устройства и третьи входы вторых сумматоров каждого вычислитель,ного блока итерации соединены с шиной логического нуля, управляющие входы триггера и всех регистров соединены с выходом генератора тактовых импульсов. версному выходу первого разряда тре.тьего регистра, выход разряда первого регистра соединен с первым входом (i +1) разряда и со вторым входом

-го разряда первого сумматора, выход которого подключен к информационному входу третьего регистра, выход которого соединен с первым информационным входом второго сумматора, второй информационный вход которого подключен к выходу группы элементов

2И-ИЛИ, инверсный выход первого разряда третьего регистра соединен с первым входом третьего сумматора, инверсный выход триггера подключен к первому входу четвертого сумматора, второй вход которого соединен с выходом четвертого регистра, выход четвертого суммат ра через пятый регистр подключен к выходу устройства, в каждом вычислительном блоке итерации, содержащем три регистра, группу элементов 2И-ИЛИ и два сумматора, инверсный выход первого регистра соединен с первым информационным входом группы элементов 2И-ИЛИ,выход л-ro разряда второго регистра соединен с пер вым информационны л входом первого сумматора и c(i+ j +2) разрядом второго информационного входа группы элементов 2И-ИЛИ, где (=1,2,...,в) л — номер разряда регистра, (, л = 1,2,...; ) — номер вычислительного блока итег рации, выход группы элементов 2И-ИЛИ подключен к второму информационному входу первого сумматора, первый управляющий вход группы элементов

2И-ИЛИ соединен с прямым выходом первого разряда второго регистра, инзерсный выход которого подключен к ,второму управляющему входу группы элементов 2И-ИЛИ и первому входу второго сум1латора, второй вход которого соединен с выходом третьего регистра, кроме того, выход i --го разряда группы элементов 2И-ИЛИ устройства соединен с входом (i,+1)-го разряда первого регистра первого вычислительного блока итерации, выходы второго и третьего

1-02332.4

3 сумматоров устроиства подключены соот . ступают на сумматор 6, на выхопе ветственно к входам второго и третье- которого формируется выражение ro регистров первого вычислительного блока итерации, выход л --го разряда х,=х,(н - ), группы элементов 2И-ИЛИ предыдущего вычислительного .блока итерации соеди- 5 Во втором такте содержимое регистнен со входом (л +1)-го разряда пер- ра 1, сдвинутое на .два разряда-вправого регистра последующего вычисли- во, записывается s регистр 2,.а энательного блока итерации, выходы пер- -чение Хл с выходов сумматора 6 в вого и второго сумматоров предыду- регистр 3. Если Ч, с 1, т.е. первый щего вычислительного блока итерации 10 разряд регистра 3, отображающий цеподключены соответственно к входам лую-часть числа Хл, равен нулю, второго и. третьего регистров после- то сигнал с инверсного выхода перводующего вычислительного блока итера- ro разряда регистра 3 разрешает про-.. ции, выход первого разряда первого хождение на сумматор 7 через группу сумматора -(и -2 ) -го вычислительного 5 элементов 2И-ИЛИ 10.содержимого реблока итерации соединен с информаци- гистра 3, сдвинутого на два разряонным входом. триггера, выход второго да вправо, т.е- Х„- 2 . Если же сумматора (y-2)-ro вычислительного Ч„Ъ1, то по сигналу с прямого выхоблока итерации подключен к входу да разряда регистра 3 через группу четвертого регистра устройства, вто-. элементов 2И-ИЛИ 10 проходит инверсрой вход третьего сумматора устройст- :ное значение содержимого регистра 2, -й ва и третьи входы вторых сумматоров равное — X o 2 . Таким образом, в каждого вычислительного блока итера- группе элементов 2И-ИЛИ 10 формируции соединены с шиной логического ну- ется значение ) . данное эначеля управляющие входы триггера и всех ние поступает на.сумматор 7, где сум-. регистров соединены с выходом генеI

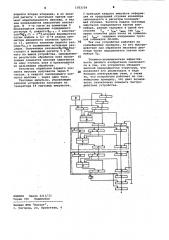

25 мируется с содержимым регистра 3 ра р атора тактовых импульсов. равным Хл . На сумматоре 7 формируетНа чертеже изображена блок-схема ся значение Х . Подача содержимо о г регистра 2 на.сумматор 7 обратным

Устройство содержит регистры 1-5, кодом позволяет заменить операцию сумматоры 6-9, группу элементов 30 вычитания операцией сложенйя.

2И-ИЛИ 10, триггер 11, (и -2) вычис- Константы9о© 1 + 2 ) ияор (1 + 2 ) лительиых блока 12 итерации, каждый формируются на входах суммма ора 8. из которых содсржит регистры 13-15, Константа ВОф; (1 + 2 ) в двоичном группу элементов 2И-ИЛИ 16, сумматоры коде имеет значение 0,100

01О1О111ОО

17 и 18, а также генератор 19 такто- 35 а константа ВОЯд (1 + 2 ) =

0,010100100111. Здесь принято, что

Устройство предназначено для вычис- и = 12.Для их формирования в разряды,. ления функции go/ X от нормализован- сумматора, где значение разряда констан-. ных чисел, представленных в формате

2 .ты равно единице, подает я обратное с фиксированной запятой. 40 значение первого разряда регистра 3. алгоритм вычисления описывается Если Хл 1, то в данные разряды по- . следующими итерационными формулами ступают единицы если )(,,рр 1, то ну.ли. Осталъны разряды сумматора заземлены, т.е. на их входы постоянно 1л.1 = 1л;2 -Щ 2. > подается значение логического "О".

Таким образом, на сумматоре 8 форми45 (л+л). руется значение Ч . В этом же такте во входной регистр 1 поступает

{р < +л,еслм х ъл второй элемент массива, и над ним про-

>i l о, если y, < изводятся операции, которые были вы50 полнены в первом такте над первым операндом. которые при начальных значениях Чо=Xq Чо= О %= О, „= g = дают пос- В третьем такте значение 9 из ле итераций 9 = 90 X. -: группы элементов 2И-ИЛИ 10, сдвинув бе.

Устройство состоит из и ступе- тое на разряд вправо, записывается ней, в каждой из которых выполняется 55 в регистр 13, в регистры 14 и 15 . заодна итерация вычисЛительного процес- писываются соответственно значения с са. Число и равно разрядности обра- выходов сумматоров 7 и 8. В группе батываемых чисел. элементов 2И-ИЛИ 16 первого вычислительного блока 12 формируется значеУстройство работает следующйм об- 60 ние 7, на сумматоре 17 -. х, на сумматоре 18 - 3 . В этом же так-.

В первом такте число Х поступает те в регистра 2 и 3 записываются во входной регистр 1. Содержимое pe- . промежуточные результаты обработки гистра 1, а также его содержимое, второго элемента массива, над ними сдвинутое на один разряд вправо, по- 65 ао второй ступени устройства произе

1023324 водится вторая итерация, а во входной регистр 1 поступает третий элемент обрабатываемого массива, и над ним производится аналогично описанной. В и -м такте на сумматоре 9

:йроизводится сложение содержимого регистра 4, равного и q, с констан» той log (1 + 2 ), которая формируется путем йрдачи в (и+ 1)-й разряд сумматора инверсного значения триггера 11, равного значению первого раэ- 10 ряда Хп q и заземления остальных разрядов. Полученное значение =бо Мпоступает в выходной регистр 5 и йз него на выход устройства. Одновремен-.

HD результаты обработки, всех последующих элементов массива сдвигаются на одну ступень вниз и производится их дальнейшая обработка.

Результат обработки первого элемента массива получается через И тактов, а каждого последующего элемента массива - через один такт.

Тактовые импульсы, управляющие работой устройства йоступают из генератора 19 тактовых импульсов.

ВНИИПИ Эеказ 4213/33

Тираж 706 Подписное

Филиал ППП "Патент", г, Ужгород, ул. Проектная, 4

С приходом каждого импульса информация из предыдущей ступени конвейера записывается в регистры последующей ступени. Частота подачи тактовых импульсов определяется тактом конвейера, равным задержке в одной его ступени To = tc + Силн где см время сложейия двух чисел на сумматоре, „„„- задержка информации группой элементов 2И-ИЛИ.

Так как устройство работает по конвейерному принципу, то его быстродействие при.обработке массивов двоичных чисел определяется тактом конвейера То.

Технико-экономическая эффективность данного изобретения заключает-. ся в том, что устройство обладает высокой однородностью структуры, что позволяет его реализовать в виде больших интегральных схем, а также то, что устройство работает по конвейерному принципу, что дает возможность значительно повысить быстродействие устройства.