Устройство для контроля параллельного двоичного кода на четность

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАЛЛЕЛЬНОГО ДВОИЧНОГО КОДА на четность по авт.св. 871166, отличающее с я тем, что, с целью расцшренигя функциональных возможностей эа счет обеспечения преобразования параллельного кода Грея в позидионньй код, в устройство введены группа из п-1 эло ентов И (где пчисло разрядов кода Грея),, группа из п-1 триггеров четности, второй элемент И и элемент задержки, причём вход синхронизации устройства соединен с первыми входами элементов И группы и через элемент задержки - с прямым входом второго элемента И, выход каждого элемента И группы соединен со счетным входом соответствующего триггера четности группы, выходад которых образуют группу выходов устройства, выход каждого, разряда . регистра соединен с вторым входом соответствующего элемента И rpynnia, выход п-го разряда регистра соединен с инверсным входом второга элемента и и является первым управляющим о S выходом устройства, выход второго элемента И является управляющим выШ хойом устройства. S еЬ9 оо со со «

- .СОЮЗ СОНЕТСКИХ . СО@4АЯИСТИЧЕСКИХ

PECf5%ЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТЙРЬГГИЙ (61) 871166

21). 3380018/18-24

22) 05.01.82 (46) 15.06.83е Бюл. Р (72) ВвВ.Зуб (53) 681.3 (088.8) (56) 1. Авторское свидетельство .СССР 9 871166, кл.G 06 Р 11/10 .07.01.80 (прототип) (54)(57) УС РОИС1ВО Paar КОНТРОЛЯ

ПАРАЛЛЕЛЬНОГО ДВОИЧНОГО КОДА на четность по авт.св. Ì 871166, о т л и ч а ю ш е е с я .тем, что, с целью расширения функцйональных возможностей за счет-обеспечения преобразования параллельного кода

Грея в позиционный код, в устройство введены группа из и-1 элементов

И (где п- число разрядов кода Грея) „

ÄÄSUÄÄ 1 4 А

g($Q G 06 Р 11/10;G 06 F 5 02 группа из и-1 триггеров четности, второй элемент И и элемент задержки, причем вход синхронизации устройства соединен с первыми входами элементов

И группы и через элемент задержки— с прямым входом второго элемента И, . выход каждого элемента И группы соединен со счетным входом соответствующего триггера четности группы, выходы которых образуют группу выходов устройства, выход каждого разряда регистра соединен с вторым входом соответствующего элемента И группы, выход и-го разряда регистра соединен с инверсным входом второго элемента И и является .первым управлякицим

"выходом устройства, выход второго

И . элемента И является управляющим выходом устройства.

1023334

Изобретение относится к вычислительной технике и может применяться для обнаружения ошибок при передаче информации в двоичном коде, а также в устройствах для преобразования кодов.

По основному авт. св. 9 871166 известно устройство для контроля параллельного двоичного кода на четность, содержащее элемент И, триггер четности и регистр сдвига, каждый разряд которого содержит триггер, дополнительный элемент И и элемент

ИЛИ, вход установки логической 1 каждого триггера регистра сдвига является информационным входом 15 устройства, выход элемента И соединен со счетным входом триггера четности, выход которого является выхо- . дом устройства, первый вход элемента И соединен с выходом регистра сдвига, а второй вход элемента И соединен с синхронизирующим входом устройства, в каждом разряде регист- ра сдвига единичный выход триггера соединен с первыми входами соответствующего дополнительного элемента

И и элемента ИЛИ, выход которого соединен с D-входом триггера последующего разряда регистра и со вторым входом элемента ИЛИ последующего разряда регистра, D-вход триггера старшего разряда соединен со вторым входом элемента ИЛИ данного разряда и со входом сигнала логического нуля устройства, выход эЛемента ИЛИ младшего разряда является выходом регистра, синхронизирующий вход устройства соединен со вторыми входами дополнительных элементов И, выходы которых соединены с синхронизирующими входами триггеров 40 соответствующих разрядов 1 1.

Известным устройством решается задача контроля на четность двоичного кода как позиционного, так и непозиционного, например, двоичного кода Грея, Последний нашел широкое применение в аналого-цифровых преобразователях в связи с малой ошибкой неоднозначности. Однако в связи с непозиционностью двоичного кода Грея возникает необходимость преобразования его в позиционный двоичный код.

Очень часто приходится решать одновременно задачу контроля двоичного кода Грея на четность и его преобразование в позиционный двоичный код, что известным устройством реализовать нельзя.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения пре- 60 образования параллельного кода Грея в позиционный двоичный код, Поставленная цель достигается .тем, что в устройство введены группа из и-1 элементов И (где п — чис- 65 ло разрядов кода Грея), группа из и-1 триггеров четности, второй элемент И и элемент задержкй, причем вход синхронизации устройства соединен с первыми входами элементов

И группы, через элемент аадержки связан с прямым входом второго элемента И, выход каждого элемента И группы .соединен со счетным входом соответствующего триггера четности группы, выходы которых образуют группу выходов устройства, выход каждого разряда регистра соединен со вторым входом соответствующего элемента И группы, выход и-го разряда регистра соединен с инверсным входом второго элемента И и является первым управляющим выходом устройства, а выход второго элемента И является вторым управляющим выходом устройства.

Введение дополнительных триггеров четности и вторых дополнительных,. элементов И позволяет расширить функциональные возможности устройства за счет преобразования кода Грея в позиционный двоичный код.

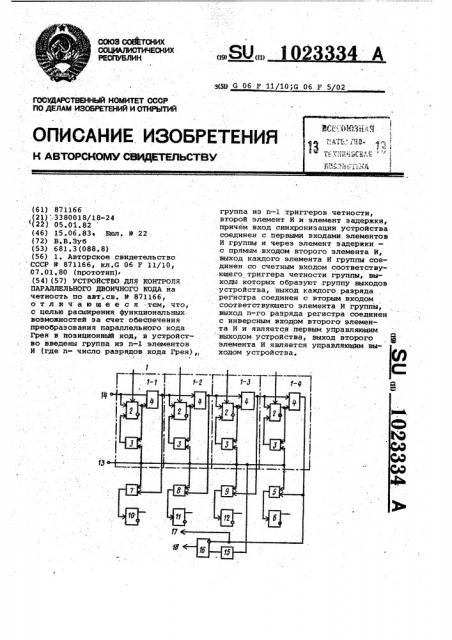

На чертеже представлена схема предлагаемого устройства при n=4.

B состав устройства входят регистр сдвига 1 с разрядами 1-1,1-2,1-3,1-4, в каждый из которых входят триггеры

2, первый дополнительный элемент И

3 и элемент. ИЛИ 4, элемент И 5, триггер 6 четности, группа вторых дополнительных элементов И 7,8 и 9, группа триггеров 10,11 и 12, синхрони зирующий вход 13 устройства и вход

14 сигнала логического нуля устройства, элемент задержки 15 и элемент

И 16, первый и второй управляющие выход 17 и 18 устройства. Установка в нулевое состояние всех триггеров устройства условно не показана.

Устройство работает следующим образом.

В исходном состоянии триггеры

2 регистра сдвига, триггер б четности и дополнительные триггеры

10,11 и 12 четности находятся в нулевом состоянии.

Контролируемый и преобразуемый код Грея подается на единичные входы триггеров 2 регистра сдвига 1 и записывается в нем. В тех разрядах, куда записаны логические нули входного кода Грея, нулевой потенциал с прямых выходов триггеров 2 блокирует соответствующий первый дополнительный элемент И 3 для прохождения через него синхронизирующих импульсов от синхронизирующего входа 13 устройства на синхронизирующий вход триггера 2, А прохождение логических единиц через разряд регистра сдвига, в котором записан логический нуль, осуществляется от входа

1023334

a(t+1) -a(t)(9b(t), Составитель И.Сигалов

РедактОр M.Áàíäóðà Техред A.A÷ Корректор О.Билак

Заказ 4214/34 Тираж 706 Подписное

ВНИИПИ Государственного комитета СССР по делам:изобретений и открытий

113035, Москва, Ж-35, Раущская наб.. д. 4/5

Филиал ППП Патент, г,ужгород, ул,Проектная,4

1 разряда через элемент. ИЛИ 4 на выход.

Каждый синхронизирующий импульс записывает логический нуль поступающий от входа 14 сигнала логического нуля устройства, а ближайший к этому входу триггер 2, в котором хранилась логическая единица, и одновременно поступает через те вторые дополнительные элементы И 7,8,9 и элемент

И 5, на второй вход которых посту- !О пает логическая единица с выходов элементов ИЛИ 4 разрядов регистра

1 сдвига, на счетные входы соответственно дополнительных триггеров 10

11 и 12 четности и триггера б чет- 15 ности, изменяя их состояние на противоположное. регистр сдвига обнулится за количество синхрониэирующнх тактов, равное числу единиц контролируемого и преобразуемого кода Грея. Определим при этом состояния триггера 6 четности и дополнительных триггеров 10, 11 и 12 четности.

Обозначим через b Ü.,b> и Ь4 значения двоичных битов разрядов кода Грея, а через а, а,а и а4 значения состояний соответствующих тригГеров четности 6,12,1I и 10, Триггер со счетным входом реали.зует операцию неравнозначности для внутреннего состояния S (t), совпадающего с, функцией выхода а (t) в момент времени t, и единственного входа Ь (t).

35 где a(t+1) - выход, совпадающий с внутренним состоянием S(t) через время ЬЙ.

1 40

Поэтому для состояния триггеров четности 6,12,11 и 10 соответственно..а,а,а и а4 можно записать

46 з ь 1 ) а2 =Ь4 ЕЬ,ЕЬ2 °

ag=b4®> ) а4 Ь4, Эта система равенств есть не что иное, как значения позиционных двоичных разрядов.

Значение ау является признаком четности проверяемого кода Грея и одновременно младшим разрядом позиционного двоичного кода.

Считывание позиционного кода с прямых выходов счетных триггеров

6,12,11 и 10 производится при обнулении регистра 1 сдвига по сигналу логического 0 на первом управляющем выходе 17 устройства.

Синхронизирующнй импульс, пройдя элемент задержки 15 и элемент И 16 (в случае, если на его инверсный вход поступает логический " 0 }, поступает на второй управляющий. выход 18. По этому снгналу производится сбрасывание счетных триггеров

6,12,11 и 10 в нуль и запись очередного параллельного двоичного числа в регистр 1 сдвига.

Время задержки в элементе 15 определяется временем переключения триг геров четности 6,12,11 и 10 и временем считывания информации с этих триггеров.

Использование устройства для контроля параллельного двоичного кода на четность предлагаемой конструкции позволяет одновременно производить контроль параллельного кода Грея на чеуность и преобразование его в позиционный двоичный код, Кроме того, предлагаемое устройство преобразует код Грея в позиционный двоичный код за количество тактов синхронизирующих импульсов, равное количеству логических единиц в коде Грея. Известные преобразователи параллельного кода Грея в позиционный двоичный код производят это преобразование или за количество тактов 2п или за количество тактов и. Таким образом, предлагаемое устройство обладает более высоким быстродействием операции преобразования параллельного кода Грея в позиционный двоичный код, ,чем известные устройства.