Устройство для контроля памяти

Иллюстрации

Показать всеРеферат

УСТР9ЙСТВО ДЛЯ КОНТРОЛЯ ПАМЯТИ содержащее формирователи адресных и разрядных токов, коммутатор , нагрузочные элементы, дискриминатор , блок индикации, первый элемент И, первый триггер и формирователь управляющих сигналов, причем первый вход коммутатора подключен к выходам формирователей адресных и разрядных токов, входы которых, второй вход коммутатора и первые входы первого триггера и первого элемента И являются одними из входов устройства, а первый выход коммутатора и выход блока индикации являются выходами устройства, третий вход и второй и третий выходы коммутатора подключены соответственно к одному из выходов нагрузочных элементов, к первому входу дискриминатора и к первому входу блока индикации, выход дискриминатора соединен с входом формирователя управлякшдах сигналов, выход первого элемента И подключен к второму входу первого триггера, отличающееся тем, что, с целью повышения надежности и быстродействия устройства, в него введены генератор контрольных сигналов, второй и третий триггеры, группа дискриминаторов, делитель напряжения , ключи, второй элемент И, элемент НЕ и группа формирователей управляияцих сигналов, входы которых соединены с выходами дискриминаторов группы, входы которых подключены соответственно к другим выходам нагрузочных элементов и к одним из выходов делителя напряжения, другой выход которого соединен с вторым входом дискриминатора, вход и выход первого ключа соединены соответственно с выходом первого триггера и с входом нагрузочных элементов, вход j элемента НЕ подключен к выходу формирователя управляющих сигналов, а выход - к второму входу первого элемента И и первому, входу второго триггера , выход которого соединен с первым входом второго элемента И и вторит входом блока индикации, третий вход которого подключен к одним из выходов формирователей управляющих сигналов группы, другие выходы которых соединены с первым входом третьего триггера, выход которого подключен к входу второго ключа, выход ко-торого соединен с входом генераР тора контрольных сигна}1ов, выход которого подключен к четвертому входу коммутатора, пятый вход которого соединен с выходом второго элемента И, второй вход которого, вторые входы второго и третьего триггеров и вход делителя напряжения являются другими входами устройства.

СООЗ СОВЕТСКИХ .

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ГО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

t (21) 3377588/18-24 (22) 04.01.82 (46) 15.06.83. Бюл. В 22 (72) A.H.Càâåëüåa, И.A.Ðîãèíñêèé, В.И.Косов, Л.В.Алексеев и A.Ä.Æó÷ков (53) 681.327 (088.8) (56) 1. Авторское свидетельство СССР

В 744736, кл. С 11 С 29/00, 1978.

2. Авторское свидетельство СССР

9 744734, кл. 6 11 С 29/00, 1978 " (прототип). (54).(57) УСТРОИСТВО ДЛЯ КОНТРОЛЯ

ПАМЯТИ; содержащее формирователи адресных и разрядных токов, коммутатор, нагрузочные элементы, дискриминатор, блок индикации, первый элемент Й, первый триггер и формирователь управляющих сигналов, причем первый вход коммутатора подключен к выходам формирователей адресных и разрядных токов, входы которых, второй вход коммутатора и первые входы первого триггера и первого элемента.И являются одними иэ входов устройства, а первый выход коммутатора и выход блока индикации являются выходами устройства, третий вход и второй и третий выходы коммутатора подключены соответственно к одному иэ выходов нагрузочных элементов, к первому входу дискриминатора и к первому входу блока индикации, выход дискриминатора соединен с входом формирователя управляющих сигналов, выход первого элемента И подключен к второму входу первого триггера, о т л и ч а ю ш е е с я тем, что, с целью повыщения надежности и быст,SU„„1023397 A родействия устройства, в него введены;генератор контрольных сигналов, второй и третий триггеры, группа дискриминаторов, делитель напряжения, ключи, второй элемент И, элемент НЕ и группа формирователей управляющих сигналов, входы которых соединены с выходами дискриминаторов группы, входы которых подключены соответственно к другим выходам нагрузочных элементов и к одним из выходов делителя напряжения, другой выход которого соединен с вторым входом дискриминатора, вход и выход первого ключа соединены соответственно с выходом первого триггера и с входом нагрузочных элементов, вход Я элемента НЕ подключен к выходу формирователя управляющих сигналов, а вьход - к второму входу первого элемента И и Первому. входу втОрого.триг.гера, выход которого соединен с первым входом второго элемента И и вто- ф рым входом блока индикации, третий вх д которого подключен к одним из выходов формирователей управляющих сигналов группы, другие выходы которых соединены с первым входом третье. го триггера, -выход которого подключен к входу второго ключа, выход ко-торого соединен с входом генера» тора контрольных сигналов, выход которого подключен к четвертому входу коммутатора, пятый вход которого

Соединен с выходом второго элемента

И, второй вход которого, вторые входы второго и третьего триггеров и вход делителя напряжения являются другими входами устройства.

1023397

Изобретение относится к вычислительной технике и может:.. быть использовано для контроля и испытаний накопителей запоминающих устройств

13у) .

Известно устройство для контроля памяти содержащее триггер, элемент И, блок сравнения, регистр числа, блок пуска-останова, блок управления, которые связаны между собой кодовой шиной (1) .

Недостатками этого устройства являются низкие быстродействие и надежность.

Наиболее близким к предлагаемому является устройство для контроля памяти, содержащее регистры числа, схему сравнения, счетчик .адресов, пульт управления, блок управления, соединенный с блоком Формирования тестовых сигналов, амплитудный дискриминатор, блоки анализа сигналов "1" и "0", элементы И и триггеры f2) .

Недостатками известного устройства являются низкие надежность и быстродействие, так как в нем не предусмотрен оперативный анализ причин сбоя, который может возникнуть из-за

10!

5 отказа формирователей адресных или разрядных токов, а также из-за обрыва адресных или разрядных шин, и анализ причин сбоя необходимо проводить с помощью дополнительных исследований.

Цель изобретения ; повышение надежности и быстродействия устройства. :35

Поставленная цель достигается тем, что в устройство для контроля памятй, содержащее Формирователи адресных и разрядных токов, коммутатор, нагруэочные элементы, дискриминатор,,щ блок индикации, первый элЕмент И, первый триггер и формирователь управляющих сигналов, причем первый вход коммутатора подключен к выходам формирователей адресных и разрядных токов, входы которых, второй .вход коммутатора и первые входы первого триггера и первого элемента И являются одними из входов устройства, а первый выход коммутатора .и вы« ход блока индикации являются выходами устройства, третий вход и второй и третий выходы коммутатора подключены соответственно к одному из выходов нагрузочных элементов, к первому входу дискриминатора и к перво- 55 му входу блока индикации, выход дискриминатора соединен с входом формирователя управляющих сигналов, выход первого элемента И подключен к второму входу первого триггера, введены генератор контрольных сигналов, второй и третий триггеры, группа дискриминаторов, делитель напряжения, ключи„ второй элемент И, элемент НЕ и группа формирователей управляющих сигналов, входы которйх соединень. с выходами дискриминаторов группы, входы которых подключены соответственно к другим выходам нагрузочных элементов и к одним,из выходов делителя напряжения, другой выход которого соединен с вторым входом дискриминатора, вход и выход первого ключа соединены соответ« ственно с выходом первого триггера и с входом нагрузочных элементов, вход элемента НЕ подключен к выходу формирователя управляющих сигналов, а выход - к .второму входу первого элемента И и первому входу второго

a",ðèããåðà, выход которого соединен с первым входом второго элемента И и вторым входом блока индикации,.третий вход которого подключен к одним из выходов формирователей управляющих сигналов группы, другие выходы которых соединены с первым входом третьего триггера, выход которого подключен к входу второго ключа, выход которого соединен с входом генератора контрольных сигналов, выход которого подключен к четвертому входу коммутатора, пятый вход которого соединен с выходом второго элемейта И, второй вход которого, вторые входы второго и третьего триггеров и вход делителя напряжения являются другими входами устройства.

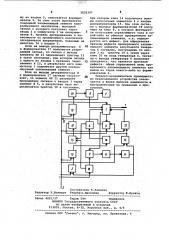

На чертеже представлена функциональная схема предложенного устройства.

Устройство содержит коммутатор 1, формирователи 2 адресных и разрядных токов (на чертеже обозначены входы 3 устройства), нагрузочные элементы 4, первый элемент И 5, генератор .б контрольных сигналов (7 - первый выход коммутатора),дискрнминатор 6, блок 9 индикации, первый триггер 10, элемент НЕ 11, второй элемент И 12, второй триггер 13, первый ключ 14, группу дискриминаторов 15, делитель 1б напряжения, формирователь 17 управляющих сигналов, группу формирователей 18 управляющих сигналов, третий триггер 19 и второй ключ 20 (21 — другой выход устройства:}.

Устройство работает следующим образом.

При контроле или испытании накопителей запоминающих устройств в режиме считывания по входам 3 поступает управляющий сигнал на вход элемента И 5, на другой вход которого проходит разрешающий сигнал с элемента НЕ 11. Выходной сигнал с элемента И 5 поступает на вход тригге- . ра 10, который устанавливается в то состояние, при котором через ключ 14 подключаются нагрузочные элементы 4 к коьвеутатору 1. Одновременно по сигналу, поступившему по одно1023397

: Ю

Составитель Т.Зайцева

Редактор К.Волошук Техред С.Мигунова Корректор В.Бутяга

Заказ 4221/37 Тираж 594 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП ",Патент", r. Ужгород, кл. Проектная, 4 му иэ входов 3, запускаются формирователи 2..3а счет этого проверяется очередной запоминанн ий элемент контролируемого накопителя, выходной сигнал с которого поступает через входы 3 и коммутатор. 1 на дискриминатор 8. Уровень дискриминации в зависимости от проверяемого накопителя опреДеляется напряжением, поданным на делитель 16 с входов 3.

Если на выходе дискриминатора -S 0 и формирователя 17 появляется разре= шающий сигнал, то сигнал с выхода элемента НЕ 11 переключает триггер 13 в такое состояние, при.котором сигнал с одного из входов 3 проходит через . 15 элемент И 12, в результате чего коммутатор 1 подключает другой контро лируемый запоминающий элемент.

Если на выходе дискриминатора 8 и формирователя 17 сигналы отсутст- 2О вуют, то элемент НЕ 11 разрешает . прохождение сигнала с входов 3 через элемент И 5, в результате чего переключается триггер 10 в состояние,. при котором ключ 14 подключает выходы нагрузочных элементов 4 к входам дискриминаторов 15. Прн этом сигна-. лы с выходов формирователей 18 поступают на блок 9, в котором фиксируется отсутствие управляющего тока в какой-либо из обмоток проверяемого запоминающего элемента, т.е. индицируется его дефект. Для определения причины дефекта проверяемого запоминающего элемента запускается генератор 6 сигналом, поступающим со входов 3 на: триггер. 19 и затем через ключ 20 на вход генератора 6. Сигналы с выхода генератора 6 позволяют определить, что является причиной дефекта; обрыв управляюшей вины проверяемого эапоминаюшего элемента нли выход иэ строя какого-либо Иэ формирователей 2.

Технико-экономическое преимуюест-. во предложенного устройства заключается в более высоких надежности и быстродействии по сравнению с пРо-. тотипом