Устройство для коррекции адресных сигналов в памяти последовательного действия

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ АДРЕСНЫХ СИГНАЛОВ В ПАМЯТИ ПО:ЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ, содержащее последовательно соединенные формирователь тактовых импульсов, регистр сдвига и усилитель считывания счетчики адреса и тактовых импульсов, регистр адреса, две схемы сравнения, два блока контроля, дешифратор и блок управления, причем выход формирователя тактовых импульсов соединен с входом счетчика тактовых импульсов и первым входом первого блока контроля , вход которого соединен с выходом счетчика тактовых импульсОв , выход первой схемы сравнения соединён с первым входом дешифратора , один из выходов которого подключен к входу блока управления а другой - к первым входам счетчика адреса и второго блока контроля , вторые входы которых объединены , выход счетчика адреса соединен с третьим входом второго блока контроля и с одним из входов второй схемы сравнения, другой вход которой ; подключен к выходу регистра адреса, а выход - к второму входу блока управления , отличают е е ,с я тем, что, с целью упрощения устройства , в него введены элемент НЕ, элемент ИЛИ и логический блок, причем входы элемента НЕ и первый вход элемента ИЛИ соединены с выходом усилителя считывания, второй вход элемента ИЛИ подключен к выходу элемента НЕ, а выход - к вторым входам счетчика адреса и счетчика тактовых импульсов и третьему входу первого блока контроля, входы первой схемы сравнения соединены соответственно с выходами счетчиков адреса и тактовых импульсов, второй и третий входы СП дешифратора подключены к выходам блоков контроля, второй выход подклю F чен к одному кз входов логического блока, вход которого соединен с одним из выходов блока управления , а выход - с третьим входом блока управления. : 2. Устройство по п. 1, отлиIN: чающееся тем, что логичесCri ОС кий блок содержит последовательно соединенные дополнительный элемент НЕ, триггер и элемент И, выход которого является ьыходом блока, одним из входов которого является один из ffi входов элемента И, а другимвходом Ь блока ЯВЛЯН1ТСЯ объединенныевход дополнительн го элемента НЕ иодин из входов триггера.

..SU„„ 1023399 А

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

g (53) G 11 Рр

ЕНИ

ОПИСАНИЕ ИЗОБРЕТ

Н ABTGPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬПЪЮ (21) 339.3220/18-24 (22) 05.02.82 (46) 15.06.83..Бюл. Р 22 (72) Н.A.Øeïàåâà, Б.E.Ãëàñêo и

A.Ê.Êóëòûãèí (53) 681.327 (088.8) (56) 1. Иигин A-.Ã., Дерюгин A.A.

Цифровые вычислительные машины. М., "Энергия", 1975, с. 355.

2. Авторское свидетельство СССР 9 903989, кл. С 11 С 29/00, 1980 (прототип). (54)(57) 1. УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ

АДРЕСНЫХ СИГНАЛОВ В ПАМЯТИ ПО"ЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ, содержащее последовательно соединенные формирователь тактовых импульсов, регистр сдвига и усилитель считывания, .счетчики адреса и тактовых импульсов, регистр адреса, две схемы сравнения, два блока контроля, дешифратор и блок управления, причем выход формирователя тактовых импульсов соединен с входом счетчика тактовых импульсов и первым входом первого блока контроля, второй вход которого соединен с выходом счетчика тактовых импульсов,. выход первой схемы сравнения соединен с первым входом дешифратора, один из выходов которого подключен к первбму входу блока управления, а другой — к первым входам счетчика адреса и второго блока контроля, вторые входы которых объедине- ны, выход счетчика адреса соединен с третьим входом второго блока конт. роля и с одним из входов второй схемы сравнения, другой вход которой подключен к выходу регистра адреса, . а выход — к второму входу блока управления, о т л и ч а ю щ е е с я тем, что, с иелью.упрощения устройства, в него введены элемент BE элемент ИЛИ и логический блок, причем входы элемента НЕ и первый вход элемента ИЛИ соединены с выходом усилителя считывания, второй вход элемента ИЛИ подключен к выходу элемента НЕ, а выход — к вторым входам счетчика адреса и счетчика тактовых импульсов и третьему входу первогО блока контроля, входы первой схемысравнения соединены соответственно с выходами счетчиков адреса и такто- Я вых импульсов, второй и третий входи дешифратора подключены к выходам блоков контроля, второй выход подключен к-одноыу из входов логического блока, другой вход которого соединен с одним из выходов блока управле- Я ния, а выход - с третьим входом блока управления ° пай

2. Устройство по п. 1, о т.л и ч а ю щ е е с я тем, что логичес- Màr кий блок содержит последовательно - © соединенные дополнительный элемент

НЕ, триггер и элемент И, выход- которого является ьыходом блока, одним -изб входов которого является один из входов элемента И, а другим входом блока являются объединенные вход до-, полнительного элемента НЕ и один из входов триггера..1fl23399

Изобретение относится к вычисли- тельной технике и может быть исполь-1 зовано для коррекции адресных сигналов в памяти последовательного действия.

Известно устройство для контроля 5 вЫбора адресных сигналов, содержашее регистр синхроимпульсов, формирователь продвигающих импульсов, регистр, включают.ий маркерный импульс, служащий для установления начала отсчета синхроимпульсов, усилитель считывания синхроимпульсов, счетчик синхроимпульсов, блок сравнения, усилитель считывания маркерного регистра, который последовательно соединен со вторым входом счетчика синхроимпульсов, и блок управления (1) °

Недостатком этого устройства является отсутствие контроля правильности выбора адресов и невозможность его коррекции.

Наиболее близким техническим ре-. шением к данному изобретению является устройство для контроля и коррекции выбора адресов, которое содержит

Формирователь продвигающих импульсов, регистр синхроимпульсов, усилитель считыьания синхроимпульсов, счетчик синхроимпульсов, схему сравнения, блок местного управления, регистр адреса, маркерный регистр, уси-ЗО литель считывания маркера, три бло-, ка контроля, блок дешифрации,. счетчик продвигающих импульсов 2 .

Недостатком известного устройства является его сложность в связи с 35 использованием двух регистров для записи служебной информации — регйстра синхроимпульсов и маркерного регистра.

Цель изобретения — упрощение уст- 4п ройства.

Поставленная цель достигается тем, что в устройство для коррекции адресных сигналов в памяти последовательного действия, содержащее 45 последовательно соединенные формирователь тактовых импульсов, регистр сдвига и усилитель считывания, счетчики адреса и тактовых импульсов, регистр адреса, две схемы сравнения, два блока контроля, дешифратор и блок управления, причем выход формирователя тактовых импульсов соединен с входом счетчика тактовых импульcos и первым входом первого блока контроля, второй вход которого Ы5 соединен с выходом счетчика тактовых импульсов, выход первой схема сравнения соединен с первым .входом дешифра, один из выходов которого подклкчен к первому входу блока управле. — 60 ния, а другой — к первым входам счет-. чика адреса и второго блока контроля, вторые входы которых объединены, выход счетчика адреса соединен с третьим входом второго блока контроля и одним из входов второй схемы сравнения, другой вход которой подключен к выходу регистра адреса, а выход— к второму входу блока управления, введены элемент НЕ, элемент ИЛИ и логический блок, причем входы элемента HE и первый вход элемента ИЛИ ,соединены с выходом усилителя считывания, второй. вход элемента ИЛИ подключен к выходу элемента НЕ, а выход — ко вторым входам счетчика адреса и счетчика тактовых импульсов и третьему входу первого блока контроля, входы первой схемы сравнения соединены соответственно с выходами счетчиков адреса и тактовых импульсов, второй и третий входы дешифратора подключены к выходам блоков контроля, второй выход подключен к одному из входов логического блока, другой вход которого соединен с одним из выходов блока управления, а выход — с третьим входом блока управления.

Логический .блок содержит последовательно соединенные дополнительный элемент НЕ, триггер и элемент И, выход которого является выходом блока, одним из входов которого является один из вхо3ов элемента и, а другим входом, блока являются объединенные вход дополнительного элемента НЕ и один из входов триггера °

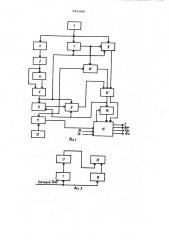

На фиг. 1 изображена структурная схема устройства для коррекции адресных сигналов в памяти последовательного действия, на фиг. 2 — 4 структурные схемы соответственно первого блока контроля совместно со счетчиком тактовых импульсов, логического блока и блока управлеНияа

Устройство содержит (фиг. Ц формирователь 1 тактовых импульсов, регистр 2 сдвига, усилитель 3 считывания, элемент НЕ 4, элемент ИЛИ 5, счетчик б адресов, счетчик 7 тактовых импульсов, первый 8 и второй

9 блоки контроля, первую 10 и вторую 11 схемы сравнения, регистр 12 адреса, дешифратор 13, логический блок 14 и блок 15 управления.

Блок 8 содержит (фиг. 2) счетчик

16 по модулю три, схему 17 свертки и схему 18 сравнения. Блок 9 отличается от блока 8 тем, что содержит на входе злеиент ИЛИ не показан) .

Логический блок 14 содержит (фиг.3) элемент НЕ 19, триггер 20 и элемент

И 21. Блок 15 управления содержит (фиг. 4) распределитель 22 импульсов, элементы И 23 и 24 элемент ИЛИ

25 и триггеры 26 и 27.

Принцип работы устройства заключается в следукиаем.

Перед началом работы устройства счетчик 7, счетчик. б, блоки контроля

8 и 9, блок 14 и .блок 15 установ1023399

3 лены в .нуль. (цепи обнуления не по- вует ошибке, возникшей в первой схе казаны ) . ме 10 сравнения, при этом блоки 8

В первой позиции регистра 2 сдвига и 9 не фиксируют ошибку. В том и записан импульс начала отсчета "0", другом случаях возбуждается первый а в-остальные позиции - синхроимпуль- выход дешифратора, сигнал поступает сы "1". При пуске устройства импульс 5 на корректирующие входы счетчика 6, начала отсчета из регистра 2 через блоки 11 и 14. Если ошибка возникла усилитель 3 поступает на элемент НЕ в регистре 2 или усилителе 3, то

4, где инвертируется и подается на откорректированная информация соотэлемент ИЛИ 5, с выхода которого пос-,ветствует истинному значению текущетупает на счетный вход счетчика б и 10.:го адреса и блок 9 не выдает сигнал блок 9 контроля, который проверяет :наличия ошибки, при этом соответствуюработу счетчика б, и далее подается ;щий выход дешифратора не возбужден и на вторые. входы счетчика 7 и блока 8 при опросе, который поступает иэ контроля, разрешая тем самым прохож- блока 15, выход блока 14 не возбуж- . дение тактовых импульсов с формиро- 35 ден. Если ошибка возникла в схеме 10 вателя 1. Последующие импульсы, счи- сравнения, то указанный выход дешифтанные с регистра 2, через усилитель ратора 13 остается возбужденным и

3 поступают на вход элемента ИЛИ 5 сигнал наличия ошибки остается на и далее на счетный вход счетчика б, входе блока 14. При опросе блока 14 .вход блока 9, на входы счетчика 7 р0 на его выходе возникает сигнал, кои блока 8, который контролирует ра- торый, поступая на блок 15, вызываботу счетчика 7. При этом происхо- ет останов устройства. дит занесение информации с формиро- При возникновении ошибки, в пер". вателя 1 на счетный вход счетчика 7 вом случае в блоках 8 или 9, а во и на вход блока 8, который контроли- втором — в счетчике 6 или счетчике рует. работу счетчика 7. Информация 7, будут возбуждены соответствующие . э состоянии счетчиков 6 и 7 посту- входы дешифратора 13. Это приводит пает на входы первой схемы 10 срав- tc формированию сигналов неисправноснения. тей на выходе дешифратора 13, постуЕсли в регистре 2, усилителе 3, пающих на вход блока 15, который счетчиках б и 7, в блоках 8 и 9 останавливает работу устройства с и первой схеме 10 сравнения ошибок одновременной фиксацией неисправнет, состояние счетчика 6 сравнива- ного блока, так как эти ошибки явется второй схемой 11 сравнения .ляются неисправимыми для данногоустс состоянием регистра 12. При совпа- родства и лишь фиксируются. денни адресов схема 11 сравнения З5 таким образом, предлагаемое уствыдает сигнал на блок 15, который ройство позволяет исправлять одивырабатывает сигйал разрешения за- ночные ошибки, возникающие в регистр писи (РЗп} или разрешения считыва- 2 и усилителе 3, но по сравнению ния (РСч) в. зависимости от того, с прототипом оно локализует неисправкакой управляющий сигнал действует 40 ности с точностью до определенного на его входах - запись (Зп) или блока, а именно, счетчнка 6 адресов, считывание (Сч) . Кроме того, блок 15 блоков 8 и 9 контроля и cxew 10 вырабатывает сигнал (C), поступающий сравнения (в прототипе просто фикв цВИ и свидетельствующий о том, что сация факта неисправности без ее поиск нужного адреса в запоминакщем 45 локализации), что повыаает точность устройстве последовательного дейст- контроля и надежность запоминающего вия завершен. устройства последовательного дей"

При возникновении ошибки в ре- . ствия. Кроме того, устройство позгистре 2 или усилителе 3 счетчик 7 воляет использовать один регистр фиксирует правильный адрес, а счет- для записи служебной информации чик 6 — текущий адрес на единицу вместо двух в прототипе, что при-меньше. В этом случае возникает снг- водит к упрощению устройства, при нал.ошибки в первой схеме 10 срав этом, количество используемых ренения, а блоки 8 и 9 не фиксируют гистров вместе с их электронныж ошибки, на входах дешифратора 13 обрамлением сокращается s 2 раза, :появляется код, соответствующий 55 а связанное с этим увеличение коли"

:ошибке, возникшей в регистре 2 или в чества электронной аппаратуры уст уснлителе 3, но тот же код соответст- ройства составляет около 5%..

IT023399

1023399

Яюрос

1и13

Составитель В.Рудаков

Редактор К.Волощук ТехредЖ.Кастелевич Корректор .Тяск0

Заказ 4221/37 Тираж 594 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж«35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4