Аналого-цифровой параллельно-последовательный преобразователь

Иллюстрации

Показать всеРеферат

АНАЛЮГО-ЦИФРОВОЙ ПАРАЛЛЕЛЬ;НО-ПОСЛЕЛОВАТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий входной блок и п по числу разрядов цифровых амплитудиых анализаторов, вход цифрового амплитудного анализатора первого разряда подключен к выходу входного блока и к первому входу сумматора первого разряда, а выход - к первому входу блока отсчета первого разряда и вхо-. ду логического блока первого разряда, выход которого через цифроаналоговый преобразователь первого разряда подключен к второму входу сумматора первого разряда, выход которого подсоединен к входу цифрового амплитудного анализатора второго разряда, вход цифрового амплитудного анализатора каждого последующего разряда соединен с выходами сумматора предудущего разряда и сумматора данного разряда, блок ввода поправок, выходом подключенный к второму входу блока отсчета первого разряда, о т л ичающийся тем, что, с целью уменьшения динамической погр иности преобразования,в него введены источник onojpHoro сигнала, дополнительные цифровые амплитудные анализатосш и сумматоры, входы первого из которых, подключены соответственно к выходам источника опорного сигнала, входного блока и цифроанаяогового преобразователя первого разряда, при зтсял выхода цифрового амплнтудиого анализатора второго разряда подключены J обратной последовательности к логическим входам первохх) дополнительного цифрового акошитуяного анализатора , сигнальный вход которого соединен с выходом первого дополнительного сумматора, первый выход - с входом блока ввода поправок первого разряда, второй выход - с входами логического блока и блока отсчета второго разряда, первые входы второго , третьего и четвертого дополнительных суктаторов подсоединены к выходу цифроаналоговогр преобразователя второго разряда, вгорае входы третьего и четвертого дополнительных сумматоров соединены с выкодом перiBOro дополнительного сумматора, третьи входы второго и четвертого дополнительных суммат( подключены к выходу источника опорного сигнала, выходы второго и третьего дополнителышос сумматоров подсоединены к сигнальным входам второго и третьего IND дополнительных цифровых амплитудных со сь анализаторов, логические входы котоPlix соединены соответственно в обрат Нрй последоаатёльирсти с йифел рового амплитудного анализахор а третьего разряда и в прякю последо-вательностн с выходами че:Гвертого дополнительного цифрового амплитудного анализатора, вход которого под:Ключен к выходу четвертого дополнительного сумматора, прнчем вторые вы|ходы второго и третьего дополнитель:ных цифровых амплитудных анализато;ров подсоединены к входам блока ввода поправок второго разряда.

„„SU„„1023650 A

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ЯСЮ Н 03 К 13 02

ОПИСАНИЕ ИЗОБРЕТЕ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3267906/18-21 (22) 01.04 ° 81 (46) 15.06.83. Бюл. 9 22 (72) Л.П. Петренко, Ю.И. Давыдов, С.Б. Кашуба и В.В. Жарких (53) 681. 325(088.8) (5б) 1. Авторское-свидетельство СССР

9 266937, кл. H 03 K 13/02, 03.08.70.

2. Цифровые электроизмерительные приборы. Под ред. В.И. Шляндина. И., . Энергия, 1972, с. 292-295, рис. 8-2 (прототип). (54)(57) АНАЛОГО-ЦИФРОВОЙ ПАРАЛЛЕЛЬ.- НО-ПОСЛЕДОВАТЕЛЬНЫН ПРЕОБРАЗОВАТЕЛЬg содержащий входной блок и П по чис лу разрядов цифровых амплитудных анализаторов, вход цифрового амплитудного анализатора первого разряда подключен к выходу входного блока и к первому входу сумматора первого разряда, а выход - к первому входу блока отсчета первого разряда и вхо-. ду логического блока первого разряда, выход которого через цифроаналоговый преобразователь первого разряда подключен к второму входу сумматора первого разряда, выход которого подсоединен к входу цифрового амплитудного анализатора второго разряда, вход цифрового амплитудного анализатора каждого последующего разряда соединен с .выходами сумматора предудущего разряда и сумматора данного разряда, блок ввода поправок, выходом подключенный к второму входу блока отсчета первого разряда, о т л ич а ю шийся тем, что, с целъю, уменьшения динамической йогрешности преобразования,в него введены источ-. ник опорного сигнала, дополнительные цифровые амплитудные анализаторы и сумматоры, входы первого нз которых подключены соответственно к выходам источника опорного сигнала, входноzo блока и цифроаналогового преобразователя первого разряда, при этом выходы цифрового амплитудного анализатора второго разряда подключены в обратной последовательности к логическим входам первого дополнительного цифрового амплитудного анализатора, сигнальный вход которого соединен с выходом первого дополнительного сумматора, первый выход - с входом блока ввода поправок первого разряда, второй выход — с входами логического блока и блока отсчета второго разряда, первые входи второго, третьего н четвертого дополнительных сумматоров подсоединены к I выходу цифроаналогового преобразователя второго разряда, вторые входы третьего н четвертого дополнительных сумматоров соединены с выходом первого дополнительного .суюаатора, третьи входи второго и четвертого Я дополнительныи сумматоров подключены к выходу источника опорного сигнала, выходы второго и третьего дополни тельных сумматоров подсоединены к 4и сигнальным входам второго и третьего Я дополнителъных цифровых амплитудных анализаторов, логические входы которых соединены соответственно в обрат- ф ) ной последовательности с внходаьаю циф-. рового амплитудного анализатора третьего разряда и в прямой последо-. (, вательности с выходами четвертого дополнительного цифрового . амплитудного анализатора, вход которого под,ключен к выходу четвертого дополнительного сумматора, причем вторые вы- ходы второго и третьего. дополнительI

;ных цифровых амплитудных анализато:ров подсоединены к входам блока вво да поправок второго разряда.

Изобретение относится к цифровой электронно-измерительной технике, а именно к конструкции аналого-цифровых преобразователей (АЦП) параллельно-последовательного действия, используемых для преобразования электрических сигналов в цифровой код.

Известен АЦП, который содержит сумматор, импульсный усилитель, цифровой амплитудный анализатор (ЦАА), выход которого соединен с блоком )О кодирующей логики, подключенным ко входам блока цифрового отсчета и цифроаналоговому преобразователю (ЦАП), выход которого соединен со вторым входом сумматора. Вход блока ввода поправок подсоединен к выходу импульсного усилителя, а выходыко второму входу ЦАП и к блоку цифрового отсчета tlj .

Недостатком известного АЦП является низкое быстродействие.

Наиболее близким к предлагаемому . является аналого-цифровой параллельно-последовательный преобразователь, содержащий входной блок и цифровых амплитудных анализаторов, вход цифрового амплитудного анализатора нервого разряда подключен к выходу входного блока и к первому входу сумматора., а выход - к первому выходу блока отсчета и входу логического блока, выход которого через ЦАП подключен iso второму входу сумматора, выход которого подсоединен ко входу цифрового амплитудного анализатора второго разряда, при этом вход циф- З5 рового амплитудного анализатора каж- дого последующего разряда соединен с выходами сумматора предыдущего разряда и сумматора данного разряда, блок ввода поправок подключен ко 4() второму входу блока. отсчета $2) .

Недостатком прототипа .является наличие динамической погрешности преобразования, поскольку при неизменном,входном сигнале .выходной сигнал (разностный 6 t) gy,) - информационный сигнал для последующего разряда, может измениться несколько раз с задержкой во времени на величину внутренней задержки блока ввода поправок, логического блока с ЦАП и. сумматора.

Целью изобретения является умень-;, шение динамической погрешности преобразования.

Поставленная цель достигается, тем, что в аналого-цифровой параллельнопоследовательный преобразователь, содержащий входной блок и П по числу разрядов цифровых амплитудных анализаторов, вход цифрового амплитудно- 60

ro анализатора первого разряда подключен к выходу входного блока и к первому входу сумматора aepsora раз-. ряда, а выход - к первому входу блока отсчета и входу логического блока первого разряда, выход которого через цифроаналоговый преобразователь первого разряда подключен к второму входу сумматора первого разряда, выход которого подсоединен к входу цифрового амплитудного анализатора второго разряда, вход цифрового амплитудного анализатора каждого последующего разряда соединен с выходами сумматора предыдущего разряда и сумматора данного разряда, блок ввода поправок, выходом подключенный к второму входу блока отсчета первого разряда, введены источник опорного сигнала, дополнительные цифровые амплитудные анализаторы и сумматоры, причем входы первого из которых подключены соответственно к выходам источника опорного сигнала, входного блока и цифроаналогового преобразователя первого разряда, при этом выходы цифрового амплитудного анализатора второго разряда подключены.в обратной последовательности к логическим входам первого дополнительного цифрового амплитудного анализатора, сигнальный вход которого соединен с выходом первого дополнительного сумматора,. а первый выход - с входом блока ввода поправок первого разряда, второй выход - с входами логического блока и блока отсчета второго разряда, первые входы второго, третьего и четвертого дополнительных сумматоров подсоединены к выходу цифроаналогового цреобразователя второго разряда, вторые входы третьего и четвертого дополнительных сумматоров соединены с выходом nepsoro дополнительного сумматора, а третьи входы второго и четвертого дополнительных сумматоров подключены к выходу источника опорного сигнала, выходы второго и третьего дополнительных сумматоров подсоединены к сигнальным входам. второго и третьего дополнительных. цифровых амплитудных анализаторов, логические входы которых соединены соответственно в обратной последовательности с выходами цифрового амплитудного анализатора третьего разряда и в прямой последовательности с выходами четвертого дополнительного цифрового амплитудного анализатора, вход которого подключен к выходу четвертого дополнительного сумматора, причем вторые выходы второго и третьего дополнительных цифровых амплитудных анализаторов подсоединены к входам блока ввода поправок второго разряда.

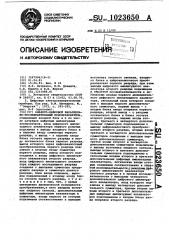

На Фиг. 1 изображена блок-схема предлагаемого преобразователяу на

Фиг. 2 и 3 - эпюры входных сигналов

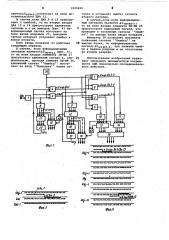

ЦАА относительно порогов их срабатывания и расчетных уровней напряжения для первого и второго разрядов; на Фиг. 4 - электрическая прин1023650 ципиальная схема четырех ЦАА последнего разряда с блоком ввода поправки.

Аналого-цифровой параллельно-последовательный преобразователь содержит входной блок 1, сумматоры 2 и 3, дополнительные сумматоры 4-7, ЦАА 8-10, дополнительные ЦАА 11-14, блоки отсчета 15 и 16, логические блоки 17-19, ЦАП 20 и 21 блоки ввода поправок 22 и 23 и источник опорного сигнала 24. - 30

Блок ввода поправки 23 {фиг. 4) содержит элементи 2И-НЕ 25 и 26, ЗИ-HE 27 и инвертор 28.

В исходном состоянии на дополни-. тельные сумматоры 4-7 подают эталон-. ный сигнал от источника опорного сиг" нала 24, равный разности двух соседних уровней U<=((g< - 0 ;, в результате на всех. выходах ЦАА 9,11 к 13 присутствуют сигналы (фиг. 4), что не мешает нормально функционировать

ЦАА 8, 10 и 12.

При подаче входного сигнала Uyg через входной блок 1 на ЦАА 8, который выдает информационные сигналы на блок отсчета 15 и на логический блок 17, входной сигналЦв может быть виве порога срабатывания ком- параторов в цАА 8, но меньше расчет» ного порога срабатывания Цк(, что приводит к ошибочному преобразованию входного сигнала U в цифровой эквивалент и, следовательно, преобразуется с ошибкой S коменскрующий . сигнал Ц, который подают на входи основного и дополнительного сумма- Ç5 торов 2 и 4, где формируется раэностние сигналы Ь((@ иЬЦ @,<, В случае,,если ЦАА 8 срабатывает с ошибкой (фиг. 2,0ш), то сигнаЛ a+ не поступает на компараторы ЦАА 9,чтода- 40 ет возможность нормально Функционировать ЦАА 12, иа втором входе .которого сигналами жд э соответствует разрешающей способности ЦАА 12, т.е. на пеРвых входах последних 45 элементов 2И-HE присутствует нулевой сигнал, который соответствует цифровому эквиваленту сигнала Ь()э, который Формируется на выходе сум-. матора, если ЦАА 8 срабатывает пра.— вильно. Другими словами не обязательно испольэовать ЦАА 8 с повышен ной точностью настройки компараторов, достаточно выбрать уровни их срабатывания ниже.или выше (однозначно) расчетных уровней срабатывания и к разиостному сигналу на выходе сумматора добавлять сигнал, равный разности двух соседних уровней предыдущего разряда к не требуется вносить поправки в компенсирующий 60 сигнал 0, что приводит к уменьшению длительности переходных процес сов для .последующих разрядов. В данном случае формируют два разностных сигнала ЬЦBx и Ь Ucop, которые исключа-65 ют возможные ошибки ЦАА при условии, что пороги срабатывания, всех компараторов выбраны ниже (выше) расчетных порогов срабатывания.

Величина опорного сигнала не обязательно должна выбираться равной разности двух соседних уровней, достаточно выбрать ее равной величине возможных отклонений порогов сраба" тывания компараторов ЦАА от их расчетных уровней. Ошибка в предыдущем

ЦАА 8 может быть всегда, когда на входе ЦАА 9 действует отрицательный сигнал,а íà ЦАА 12 сигналаЦ„д „ входит в его рабочий диапазон. Выходы ЦАА 9 и первые входы ЦАА 12 подключены в обратной последовательности, т.е. первый выход ЦАА 9 под-. ключен к последнему входу ЦАА 12, и т.д., что позволяет реализовать ситуацию когда раэностный сигнал прк выходе из рабочего диапазона

ЦАА 9 попадает в рабочий диапазон очередного ЦАА 12 со стороны компараторов с максимальным порогом срабатывания. Такое включение позволяет значительно упростить логические блоки преобразования информационных сигналов.

Сигнал ошибки со второго выхода

ЦАА 12 поступает (Фиг. 1) через блок ввода поправки 22 на второй вход блока отсчета 15 и устраняет погрешность выходного хода первого разряда, не изменяя уровней аналоговых сигналов в разряде.

Сигналы с первых выходов ЦАА 12 . поступают на блок отсчета 16.и через логический блок 18 на входы

ЦАП 21, на выходе которого Формируется компенсирующий сигнал Цк,, который поступает на вход сумматора 3 и на входы дополнительных сумматоров .

5-7, где возможны четыре случая.

Разностный сигнал b.U Э s сумматоре 2 формируется без ошибки ЦАА 8 и

ЦАА 9 второго разряда АЦПП также срабатывает без ошибки. В этом случае информационный сигнал д Ц 8 постуцает на ЦАА 10.

Разностиый сигнал h:U, в сумматоре 2 формируется без ошибки ЦАА 8, а во втором разряде ЦАА 9 срабатывает с ошибкой. В этом случае информационный сигналЬ9ц>р@< поступает на второй вход ЦАА 13.

Раэностный сигнал ЬЦ, э в допол« нительном сумматоре 2 Формируется с ошибкой ЦАА 8, а во втором разряде

ЦАА 12 срабатывает без ошибки. В этОм случае информационный сигнал

ЬО р4„ . поступает на второй вход

ЦАА 14.

Разностный сигнал Ь U q+ Э„„в дополнительном сумматоре 2 формируется с ошибкой ЦАА 8, а во втором разряде ЦАА 12 срабативает также с ошибкой. В этом случае информационный

1023б50 сигнал60к рз„ g поступает на вход дополнительного ЦАА ll °

В случае, если ЦАА .9 и 12 срабатывают с ошибкой, то на вторых входах

ЦАА 13 и 14 присутствуют единичные сигналы и с их выходов (фиг. 4) информационный сигнал поступает на блок ввода поправок 23, выходной сигнал которого устраняет ошибку в блоке отсчета.

Блок ввода поправок 23 работает 16 следующим образом.

В случае, если информационным си "алом является А4орвп фиг то на всех. входах элемента ЗИ-НЕ 27 присутствет единичный сигнал и, сле-.f5 довательно, проходя элемент 2Н-НЕ 26, единичный сигнал Ошибка поступает на вход Поправка блока от-, счета и устраняет ошибку отсчета второго разряда.

В случае, если. если информационным си л м является АОкор Ои-3 i то на всех входах элемента 2И-НЕ 25 присутствует единичнь1й сигнал, что приводит к появлению сигнала Ошибка на выходе блока ввода поправок.

Инвертор 28 цозволяет исключить появление сигнала Ошибка на выходе блока, по информационному сигналу ЬО,р Bre2, при наличии ошибки в первом разряде и ее отсутствии во втором разряде °

Использование изобретения позволяет уменьшить динамическую погрешность AIQI параллельно-последовательнога действия.

Фиа 4

Составитель Г. Шаповал

Редактор A. Гулько Техред И.Кскатура Корректор А. Ильин

Закаэ 4240/50 . Тираж 936 . Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4