Устройство для выделения максимального числа

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ МАКСИМАЛЬНОГО ЧИСЛА, содержащее элементы И, ИЛИ, причем вхопы -i -пз элемента ИЛИ соед11нены с входами 1 чых разрядов сравниваемьсс чисел (i I,..,. , w, где vn- число разрядов сравниваемксх чисел), а выход соединен с. первым входом i .«го элемента И, отличаюше ее я тем, что, с целью упрощения устройства и повышения быстродействия, устройство содержит элементы НЕ, првяем j -ый вход j -4ч э;1 емента И соединен с BXiiходом ( J- 1) -го элемента НЕ, где j 2, ,.., т , вкоа к-го элемента НЕ соепинен с выходом к-го элемента ИЛИ, где к 1,1.. , W- 1, выходы элементов И являюггся выходами устройства .

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН .

4902 А (19) И (11) всю G06 Р 7/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСИОИМ СВИДЕТЕЛЬСТВУ

Э>

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (2 1) 3397662/1824 (22) 17.02.82 (46) 23.06.83. Бюл. № 23 (72) В.П.Карелин и Б.Н.Миронов (7 1) Таганрогский радиотехнический институт им.В.Д. Калмыкова (53) 681.325 (088. 8) (56) 1. Авторское свидетельство СССР № 475616, кл. 60 6 F 1/04, 1973.

2. Авторское свидетельство СССР № 875376, кл. 606 F 7/04, 1980 (прототип), (54) (57) УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ МАКСИМАЛЬНОГО ЧИСЛА, содержашее элементы И, ИЛИ, причем входы

-го элемента ИЛИ соединены с sxoдами i -ых разрядов сравниваемых чи- сел (1 1„..., и, где vol- число разрядов сравниваемых чисел), а выход соединен с перв,ым входом 1 -го элемента И, о т л и ч а ю m е е с я тем, что, с целью yapomeHas устройства и повышения быстродействия, устройство содержит элементы НЕ, причем, j -ый вход ) -го элемента И соединен с выходом (- 1) -го элемента НЕ, где

) = 2, ..., йЪ, вход к-го элемента НЕ соединен с выходом к-r î элемента

ИЛИ, где к 1,, ю- 1, выходы элементов И являкйся выходами устройства»

1024902

Наиболее близкиМ к изобретению является устройство цля определения максимального иэ vn двоичных чисел, содержащее уп груш| элементов И, в групп

40 элементов памяти, уп групп элементов

ИЛИ, многовхоцовые элементы ИЛИ, управляющие элементы И, регистр результата, элементы задержки, причем вход управления началом работы устройства

45 соединен с первым входом первого элемента задержки, выход каждого 1 -ro элемента задержки, где 1,2, ...., (и - 1), -..количество разрядов сравниваемых чисел, соединен с первым входом (1+ 4 )-го управляющего элемента И и с входом t + 1)-го элемента задержки, выxone (и- l}-го элемента задержки соединен с выходной шиной устройства, .выход каждого j -го управляющего элемента И, где } - 1,2, ..., и, соединен с информационным входом -го разряда регистра результата, инверсный выход каждого первого элемента памяти к-й

Изобретение относится к технической кибернетике и может быть использовано для построения технических средств систем классификации, распознавания образов, поиска информации и автоматизации принятия решений в не четких условиях.

Устройство предназначено для реализации операуий дизъюнкции и импли кации над нечеткими, переменными (высказываниями) в нечеткой логике II,Çâqe, где результат С операции дизъюнкции И нечетких переменных В„- (i 1, 2,, и } вычисляется ло формуле С =

=ма В„., а результат З операции импликации A B„. двух нечетких переменных А и В; вычисляется ло формуле . 3 Yn 4(1-А, В„. ). Здесь А,B (1 = 1,2, . - -, И ), С, 3 — числа из интервала (0,1, представленные -разрядным унитарным кодом (один из ю ).

Известен распределитель сигналов, позволяющий выделять левую единицу из и -разрядного двоичного кода, соцержаший выполненные на триггерах вспомогательный регистр, основной регистр, однотипные ячейки, каждая из которых содержит элемент ИЛИ и цва элемента

И. Выделение левой единицы происходит эа цва такта (1) .

Недостатком известного устройства является низкое быстродействие, сложность и то, что оно не выделяет максимального иэ И чисел, представленных унитарным кодом. 35 группы, где к " 1,2, „, М, соединен с первым входом первого элемента И к-й группы, .выход каждого из которых соединен с входом установки в нулевое состояние второго элемента памяти к-й группы и с первым .входом первого эле мента ИЛИ к-й группы, выход каждого р -го элемента ИЛИ каждой к-й группы,. где P " 1,2,..., (И - 2), соединен с первым входом (р + 1 )-ro элемента

ИЛИ к-й группы, инверсный выход каждого 8-го элемента памяти к-й группы, где В =* 2,3,, (и -. 1)> соединен с первым входом Е -го элемента И к-й группы, выход которого соединен с вторым входом (8-- 1)-го элемента ИЛИ к-й группы, прямой выход каждого 1-го элемента памяти к-й груплы, соединен

В с к-м входом 1 -го многовхоцового элемента ИЛИ, выход кажцого из которых соединен с вторым входом 1-го управляют щего элемента И, выход каждого 1-го

E управляющего элемента И соединен с вторыми входами i-х элементов И всех групп (2) . 1

Недостаъ. ом устройства является его сложность. и низкое быстродействие.

Целью изобретения является упрощение устройства и повьпцение его быстродействия.

Поставленная цель достигается тем, что устройство QJIB выцеления макси-. мального. числа, . содержащее элементы

И,ИЛИ, причем входы 1 «го элемента

ИЛИ соединены с входами j -х разрядов сравниваемых чисел (j 1, „., р где Ф - число разрядов сравниваемых чисел), а выход соединен с первым входом 1 -ro элемента И, содержит элементы НЕ, причем ) -й вход -го элемента И соединен с выходом (": 1)-го элемента НЕ, где f 2,.... п, вход к-го элемента НЕ соединен с выходом -ro элемента ИЛИ, где к 1, „., и- 1, выходы элементов И йщяются выходами устройства.

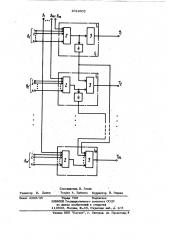

На чертеже пра@с"тавлена блок-схема устройства.

Устройство состоит из и поразрядных узлов анализа 1, . .., 1„„, содержащих элементы ИЛИ2, ИЗ и НЕ4 (вьМи узле элемент HE отсутствует), групйй шин 5<, 5,, ..., 5„цля подачи первого числаЪ групп 64, 6, „,, бщ по 8 шин в каждой для подачи соответственно 1-го, 2-ro,; i -, vn-го разряда каждого из и остальных чисел, выходных шин 74, 7, ..., 7„„.

1024902

Назначение каждого иэ щ поразряд- элементов ИЛИ2 поразрядных узлов ананых узлов анализа состоит в выполнении лиза образуется код, представляющий цизъюнкции соответствующих разрядов собой поразрядную цизъюнкцию кодов чиунитарных кодов чисел, поданных на вход сел В, В,,..., В„, . Пусть в этом элемента ИЛИ, в выделении единицы со- .,коде старшая единица находится в -м ответствующего разряда и выработке сиг- раэряце. Тогда единичный сигнал с выкала для блокировки элементов И млад- хода элемента ИЛИ 2, -го узла анаших узлов анализа. лиза проходит на выход элемента И 3,.

Возрастание индексации на чертеже так как на остальные входы этого элесоотве гствует упорядоченности от стар- мента с выходов элементов HE 4 всех

tO, < ших разрядов к младшим.. старших узлов анализа подаются едиВычисление дизъюнкции р нечетких ничные сигналы. Нулевой сигнал с выпеременных состоит в выполнении пораз- хода элемента HE 4 i -ro узла запрерядной. диэъюнкции унитарных кодов этих щает прохождение единич)юго сигнала чисел и в последующем выделении- иэ по- на выходы элементов И 3 всех младших

15 лученного кода старщей единицы. поразрядных узлов анализа. Таким обраВычисление результата 3) имплика- зом, на выходных шинах 7 формируешься ции А- В двух нечетких переменных унитарный код максимального иэ чисел

Аи В(состоит вполученииразности(1-А) В, В .,,.. В и нахождении аизъюнкпии чисел (1»А), В 2 При вычислении операции импликации в указанном порядка, В устройстве двух нечетких переменных А и В, на значение разности 1-А образуется шины 6 подается унитарный код числа А. за счет инверсного порядка подклю- При этом на первых входах элементов чения шин разрядов числа А к первым ИЛИ 2 образуется унитарный код числа входам эжмен ИЛИ поразряд уэ 25 1-A. лов анализа. Тем самым вместо кода Так как результат операции импликачисла А фактически подается код числа ции опрецеляется как дизъюякпия чисел (1-A) и В, то, подав число В на

Устройствоработаетслеаующим образом.. входы 6 укаэанным образом, на выхоПри вычислении операции дизъюнкцни 3О дах 7 устройства получим унитарный код нечетких переменных на шины 6 подаю результата операции импликации чисел ся нулевые сигналы. На шины 6 подаются А и В. унитарные коды и чисел B, В, .«.,Ц, Таким образом, предлагаемое изобре»

Если требуется вытижнить дизъкщк - ., тение позволяет упростить устройство цию меньшего числа нечетких переменных 35 за счет сокращения количества логичес1 то на шины остальных переменных по- ких элементов и повысизь быстродействие даются нулевые сигналы. На выхоцах устройствав

102490k

Состамтель В. Гусев Техреа А. Бабинец Корректор B. Гирняк

Редактор В. Данко

Тираж 706 Подписное

ВНИИПИ =Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раупская наб, д. 4/5

Заказ 4396/45

Филиал ППП Патент, г. Ужгород. ул. Проектная,4