Устройство для вычисления функции @ = @ + @

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК ую G 06 F 7/552

ПО ДЕЛАМ ИЗОБРЕТЕНИИ И ОТКРЫТИЙ

ОЛИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHO5Nf СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР (21) 3374987/18-24 (22) 06.01.82 .(46) 23.06.83. Вюл. 11 23 (72) И.О. Арро, О.Э. Кангур и

А.Э. Отс (71) Таллинский политехнический институт (53) 681.325(088.8) (56) 1. Авторское свидетельство СССР

Н 645154, кл. 6 06 F 7/552, 1979.

2. Авторское свидетельство СССР

Н 656055, кл. С 06 F 7/552, 1979 (прототип), 1 (54)(57) УсТ ой т о для вьиислкния

ФУИЮИИ Z = /х +у, содержащее блок выборки меньшего числа, блок деления, блок памяти;и три блока умножения, причем первый и второй входы блоков выборки меньшего числа соединены с входами соответственно первого и второго аргументов устройства, первый выход блока выборки, меньшего чис" па соединен с первым входом блокаделения, второй вход которогосоединен с вторымвыходом блокавыборки меньше„.Я0„„10 4912 А

ro числа и первым входом nepeoro блока, умножения, второй вход и выход" которого соединены соответственно с выходом второго блока умножения и вы: ходом устройства, о т л и ч а ющ е е с я тем, что, с целью повышения точности, в него введены блок возведения в квадрат, сумматор и вычитатель, первый и второй входы которого соединены соответственно с первым и вторым выходами блока памяти„ ° вход которого соединен с выходом старших разрядов блока возведения в квадрат, вход которого .соединен с выходом блока деления, выход вычитателя сое- динен с первым входом третьего блока о умножения, второй вход и выход которого соединены соответственно с выходом младших разрядов блока возведения в квадрат и первым входом сумма" тора, второй вход и выход которого соединены соответственно с первым выходом блока памяти и первым входом второго блока умножения, второй вход которого соединен с выходом всех разрядов блока возведения в квадрат.

1 024912

Изобретение относится к цифровой вычислительной технике и предназначено для использования в специализированных мини-ЭВИ.

Известно устройство для вычисления квадратного корня из суммы квад.ратов двух чисел, содержащее счетчики, схемы сравнения, делители частоты, блоки утроения, элементы И и НЕ и блок управления 1.1).

Однако. такое устройство обладает низкой точностью.

Наиболее близким к изобретению

1О по технической сущности является. устройство для вычисления квадратного корня из суммы квадратов двух чисел, содержащее схему сравнения, блок ум» ножения, блок вычисления коэффициентов, суммирующий и вычитающий счетчики (21.

Однако известное устройство так-же обладает низкой точностью, что связано с нецелесообразным выбором вида вспомогательной функции, эначе"

20 ния которой хранятся в блоке вычисле- 25 ния коэффициентов.

Целью изобретения является повыше" ние точности.

Поставленная цель достигается тем, что в устройство для вычисления. функции Е = 1Гх""+у"-, содержащее блок выборки меньшего числа, блок деления, блок памяти и три блока умножения, причем первый и второй входы блока выборки меньшего числа соединены с входами соответственно первого и второго аргументов устройства, первый выход блока выборки меньшего числа соединен с первым входом блока деления, второй вход которого соединен с вторым выходом блока выборки мень" шего числа и первым входом первого блока умножения, второй вход и выход . которого соединены соответственно с выходом второго блока умножения и выходом устройства, дополнительно введены блок возведения в, квадрат, сумматор и вычитатель, первый и второй входы которого соединены соответственно с первым и вторым выходами блока памяти, вход которого соединен с выходом старших разрядов бло ка возведения в квадрат, вход которого соединен с выходом блока деления, выход вычитателя соединен с пер- 55 вым входом третьего блока умножения, второй вход и выход которого соединены соответственно с выходом млад" ших разрядов блока возведения в квадрат и первым входом сумматора, второй вход и выход которого соединены соответственно с первым выходом блока памяти и первым входом второго блока умножения, второй вход которого соединен с выходом всех разрядов блока возведения в квадрат.

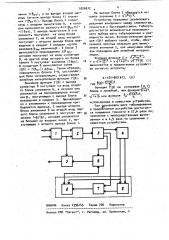

На чертеже представлена блоксхема устройства.

Устройство яля выиислвния функции

Е = (х +у содержит блок 1 выборки меньшего числа, блок 2 деления, блок

3 возведения в квадрат, блок 4 памяти, блоки 5-7 умножения, сумматор 8 и вычитатель 9.

Блок памяти 4 содержит дешифратор и две запоминающие матрицы.

Устройство работает следующим об" разом.

Числа х и у поступают на входы блока выборки меньшего числа 1, кото" рый сравнивает их и коммутирует на выходы так, чтобы на .первом выходе блока 1 всегда оказывалось меньшее число (будем считать, что это Y), а на втором выходе большее .(Х). Оба числа поступают на входы блока деления 2, в котором вычисляется частное

- 1, Это частное поступает на

М вход блока возведения в квадрат 3, в котором вычисляется величина Р

= (РЯ . Одновременно в блоке 3 двоичный код величины разбивается на две группы разрядов - старшую и младшую щ„, Число разрядов старшей группы ас . определяет шаг h=F с которым в запоминающих матрицах блока памяти

4 хранятся значения вспомогательной функции (р) †- =(Ъ

Остальная часть устройства работает аналогично известному. Старшая группа разрядов поступает на вход дешифратора блока памяти 4, Выходы дешифратора, чисяо которых равно

2 от, соединены с соответствующими строками запоминающих матриц. В первой матрице хранятся значения функции f(P), а во второй матрице " значения f(Qh), соответствующие сдвигу аргумента на шаг h. Появление определенной кодовой комбинации Р т на входе. дешифратора приводит к выборке соответствующих строк запоминающих матриц и появлению на выходе первой матрицы (первом выходе блока 4) эна3 10249 чения Г(т), а на выходе второй матрицы (втором выходе блока 4) значе-ния f(P +h), Выходы блока 4 соеди- . нены с входами вычитателя 9, в котором вычисляется разность f((.T+h)- 5

"Г(9ст). С выхода вычитателя 9 эта раэност ь поступает на вход блока умножения 7, на второй вход которого поступает с второго выхода блока воз" ведения в. квадрат 3 младшая группа 10 разрядов е величины)Ъ . В блоке 7 вычисляется произведение h, Р >p, > которое поступает на вход сумматора

8, на другой вход которого иэ блока памяти 4 поступает значение f(). 15

В сумматоре 8 вычисляется сумма

f(p) = Г()+ дфм . Таким образом, совокупность блоков 7-9, составляю-щая блок интерполяции, осуществляет линейную интерполяцию функции f(p), 2О

Значение функции f(P) с выхода сумматора 8 поступает на вход второго блока умножения 6, в котором оно умножается на полноразрядное эначе" ние р, поступающее с выхода блока 25 возведения в квадрат 3. О<цновременно с умножением к произведению прибавляется единица.. С выхода второго блока умножения 6 на второй вход первого блока умножения 5 поступает ве- Зо личина 1+pf(p) которая умножается на большее иэ входных чисел Х, поступающее с второго выхода блока 3.

12 4

На выходе блока 5 образуется искомое значение Z = -/х(+у .

Устройство позволяет реализовать разумный компромисс между сложностью, точностью и быстродействием. Гибкость достигается возможностью произволь" ного выбора шага табулирования и раз" рядности чисел. Вспомогательная функция f(P) выбрана такой, чтобы, обес" печивая простые операции для вычис" ления значения Е, она наилучшим обра-. зом подходила для линейной интерполяции.

Искомая Функция У, кх

- "x/1+(xX)а = х 1).Г+аР» 1+ р (1) вычисляется в предлагаемом устройстве согласно алгоритму =хВ+ имл, (И, да Им)= -"

Функция f(p) на интервале 0,1» ближе к линейной, чем функций )Д+,Р

- + или функция Р = используемая в известном устройстве.

При одинаковом шаге табулирования в предл%гаемом устройстве достигает" ся повышение точности в 27,6 раза по сравнению с непосредственным вычис" лением и в 6,9 раза по сравнению с известным устройством.

ВНИИПИ Заказ 4396/45 Тираж 706 Подписное к

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4