Устройство для контроля логических микросхем

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯКОНТРОЛЯ ЛОГИЧЕСКИХ МИКРОСХЕМ, содержащее генератор импульсов, триггер результата/ соединенный первым и вторым выходами с Входами индикатора годности и индикатора брака соответственно , первым входом - с входной клеммой устройства, вторым входом с выходом блока сравнения, соединенноро первым и вторым входами через первый И второй преобразователи уровней соответственно с клеммой для подключения .контролируемой логической микросхемы и с выходом эталонной логической микросхемы, соединенной первым входе с первым выходрм задатчика входных условий, соединённого вторым выходом с первой клеммой для подключения входа ..: контролируемой логической микросхемы , отличающееся тем,. что, с целью расширения области применения устройства, в него введены первый и второй анализаторы кода, первый и второй триггеры уста новкй, первый и второй элементы И-ИЛИ, первый одновибратор и второй одновибратор, соединенный входом через первый одновибратор с входной клеммой устройства и S-вхрдами первого и второго триггеров установки, непосредственно - с третьим входом блока сравнения, выходом - с первыми входами.первого и второго элементов И- ИЛИ, соединенных вторыми Щ и третьими входами с выходом генератора И1утульсов, выходами - соответственно с второй клеммой для подключения входа контролируемой логической микросхемы и с вторь м входом эталонной логической микросхемы , четвертыми входа1 и - с выходами соответств уюпих первого и второго триггеров установки, соединенных R-входами с выходами соответстIsD венно первого и второго анализаторов кода, соединенных входами с выа ходами соответствующих первого и BTopofo преобразователей уровней. со о:

«е <э

COI03 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

3G0 G 01 R 31 2 ю

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ьввь, .

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3412428/18-21

1 ((22) 26.03.82, (46) 30.06 ° 83. М 24 (72) В.В. Терпигорьев (53) 621 ° 317.79(088.8) (56) 1. Авторское свидетельство СССР

У 441532, кл. С 01 R 31/28, 1975.

2. Авторское свидетельство СссР

9 451994. кл. G 01 Р 11/00, 1975 (прототип), (54)(57) УСТРОЙСТВО ДЛЯ КОНТРОЛИ

ЛОГИЧЕСКИХ МИКРОСХЕМ, содержащее re. нератор импульсов, триггер результата, соединенный первым и вторым выходами с входами индикатора годности и индикатора брака соответственно, первым входом - с входной клеммой устройства, вторым входомс выходом блока сравнения, соединенного первым и вторым входами через первый и второй преобразователи уровней соответственно с клеммой для подюиочения,контролируемой логической микросхемы н с выходом эталонной логической микросхемы, соединенной первым входом с первым выходрм задатчика входных условий, соединенного вторым выходом с первой клеммой для подключения входа контролируемой логической микросхе- мы, о т- л и ч а ю щ е е с я тем, что, с целью расширения области применения устройства, в него введены первый и второй анализаторы кода, первый и второй триггеры уста новкй, первый и второй элементы

И-ИЛИ, первый одновибратор и второй одновибратор, соединенный входом через первый одновибратор с входной клеммой устройства и S-входами первого и второго триггеров установки, непосредственно - с третьим входом блока сравнения, выходом - с первыми входами. первого и второго эле.ментов И-ИЛИ, соединенных вторыми и третьими входами с выходом генератора импульсов, выходами - соответственно с второй клеммой для подключения входа контролируемой логической микросхемы и с вторьл входом эталонной логической микросхемы, четвертыми входами — с выходами соответствую их первого и второго триггеров установки, соединенных R-входами с выходами соответственно первого и второго анализаторов кода, соединенных входами с вы ходами соответствующих первого и второГо преобразователей уровней.

1026096

Изобретение относится к контрольно-измерительной технике и может быть использовано в производстве полупроводниковых приборов при контроле интегральных логических микросхем, в том числе больших интег — 5 ральных схем (БИС) преимущественно с отсутствием входного вывода установки микросхем в исходное состояние, содержащих узлы с триггерными элементами, например счетчики, регистры сдвига, делители частоты и др

Известно устройство для контроля логических микросхем, содержащее клеммы для подключения контролируе- мой и эталонной микросхем, схему сравнения, генератор управляющих сиг. налов и блок индикации (1) .

Однако известное устройство не позволяет проводить контроль логических микросхем типа счетчиков, делителей частоты, регистров сдвига.

Наиболее близким к предлагаемому является устройство для контроля логических микросхем, содержащее генератор импульсов, триггер резуль" тата, соединенный первым и вторым выходами с входами индикатора годности и индикатора брака соответственно, первым входом — с входом ЗО устройства, вторым — с выходом блока сравнения, связанного первым и вторым входами через первый и второй преобразователи уровня соответственно с выходами контролируе- 35 мой и эталонной логических микросхем, соединенных первыми входами с первым и вторым выходами задатчика входных условий соответственно (2j .

Недостатком такого устройства является ограниченность области при; менения,так как оно не позволяет контролировать микросхемы,. в струк-, туру которых входят узлы, Построенные на триггерных элементах, таких как делители частоты, регистры сдвига и другие, у которых отсутствуют входные выводы установки микросхемы в ноль, что приводит к неопределенности их составления при контроле. Кроме того, в устройстве отсутствует возможность предварительной установки микросхемы в произвольно заданное состояние, что необходимо при контроле сквозного пе- 55 реноса функционального узла, состоящего из нескольких последовательно соединенных счетчиков, например

БИС для электронных часов.

Цель изобретения — расширение об- Я) ласти применения устройства.

Поставленная цель достигается

-eM, что в устройство для контроля логических микросхем, содержащее генератор импульсов, триггер резуль- 65 тата, соединенный первым и вторым выходами с входами индикатора годности и индикатора брака соответст венно, первым входом — с входной клеммой устройства, вторым входом с выходом блока сравнения, соединенного первым и вторым входами через первый и второй преобразователи уровней соответственно с клеммой для подключения контролируемой логической микросхемы и с выходом этаЛонной логической микросхемы, соединенной первым входом с первым выходом задатчика входных условий, соединенного вторым выходом с первой клеммой для подключения входа контролируемой логической микросхемы, введены первый и второй анализаторы кода, первый и второй триггеры установки,.первый и второй элементы И-ИЛИ, первый одновибратор и второй одновибратор, соединенный . входом через первый одновибратор с входной клеммой устройства и S-.âõoдами первого и второго триггеров установки,.непосредственно — с третьим входом блока сравнения, выходом — с первыми входами первого и второго элементов И-ИЛИ, соединенных вторыми и третьими входами с выходом генератора импульсов, выходами — соответственно с второй клеммой для подключения входа конт- ролируемой логической микросхемы и с вторым. входом эталонной логической микросхемы, четвертыми входами— с выходами соответствующих первого и второго триггеров установки, coe"" диненных R-входами с. выходами соответственно первого и второго анализаторов кода, соединенных входами с выходами соответствующих первого и второго преобразователей уровней.

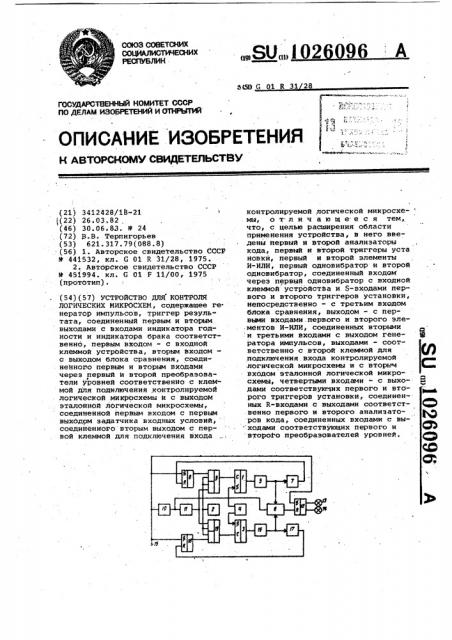

На чертеже показана блок-схема устройства.

Устройство для контроля логической микросхемы 1 содержит генератор 2 импульсов, эталонную микросхему 3, задатчик 4 входных условий, первый преобразователь 5 уровней, блок 6 сравнения, первый ана лизатор 7 кода, первый триггер 8 ,установки, перВый элемент 9 И-ИЛИ, первый и второй одновнбраторы 10 и 11, триггер 12 результата, индикатор 13 годности, индикатор 14

l брака, входную клемму 15, второй преобразователь 16 уровней, второй анализатор 17 кода, второй триггер

18 установки, второй элемент

И-ИЛИ 19.

Устройство работает следующим образом.

В устройстве используется принцип сравнения работы контролируемой логической и эталонной микросхем 1 и 3 соответственно при всех возмож1026096 ных комбинациях входных сигналов, единицы, сбрасывающий триггер 12 причем синхронность их работы дос- результата и включающий индикатор 14 тигается путем предварительной уста- брака, в противном случае продолжановки внутренних функциональных ет оставаться включенным индикатор узлов микросхем в идентивные состоя- 13 годности. По заднейу фронту имния. Установка проводится независи- 5 пульса первого одновибратора 10 за-, мо для каждой микросхемы, а конт- пускается второй одновибратор 11, роль — при их параллельной работе. импульс логической единицы с выхода

В исходном состоянии с помощью, которого через первые входы элемензадатчика 4 входных условий заданы тов И-ИЛИ 9 (19) разрешает прохожнеобходимые для создания счетного 10 дение импульсов от генератора 2 режима входные -воздействия на конт- импульсов на счетные входы с контролируемую 1 и эталонную 3 микросхе- ролируемой 1 и эталонной 3 микро/ мы. После прихода кратковременного схем. Информация с выходов этих микимпульса на. клемму 15 путем воз- росхем поступает на входы блока б действия на установочные входы 15 сравнения, который сравнивает лоS-триггеров установки 8 и 18 и ре-, " гические уровни одноименных .выходов зультата 12 последние устанавлива- контролируемой 1 и эталонной 3 микются в единичные состояния, запус-- pocxeM и при их .синхронной работе кается первый одновибратор 10. Вклк! не изменяет состояния своего выхочается индикатор 13 годности, на. 0 да. В случае неработоспособности четвертых входах элементов И-ИЛИ 9 контролируемой микросхемы идентичи 19 появляется сигнал логической ность состояния выходов обеих мик-:

: I единицы, на запрещающий вход (зап- Росхем нарушается, на выходе блока рет),блока б сравнения кодов посту- б сравнения формируется уровень лопает сигнал, устанавливающий на гической единицы, сбрасывается тригего выходе напряжение логического гер 12 Результата, включается инди-!

Нуля. На счетные входы контролируе- катор 14 брака. мой 1 и эталонной 3 микросхем от Контроль последующих функциональгенератора 2. импульсов через эле-! ных узлов контролируемой микросхемы менты И-ИЛИ 9 и 19 поступают импуль- 1 происходит аналогично описанному сы, которые изменяют состояние счет - З0 II Teì установки устройства в новое чиков контролируемой 1 и эталонной, исходное состояние.

3 микросхем до тех пор, пока на их При н обходимости контроля сквоз выходах .не появится код установоч- ного переноса для группы последоного числа (под установочным числом вательно соединенных счетчиков, Вхо подразумевается двоичное число, . 35 дящих в состав микросхемы, вначале соответствующее условному исходно- устанавливают все счетчики в исходму установочному состоянию f

В этот момент времени на выходе 23, путем установки нулевой длианализатора 7 кода (или 17) появит- тельности импульса второго одновибся. сйгнал логической единицы, кото- Ратора 11, а затем осуществляют рый сбрасывает триггер 8 (18) уста- контРоль счетчиков, устанавливая новки, превращая подачу импульсов 5 нулевую длительность первого однона счетный вход установленной мик- вибратора 10. росхемы. Анализаторы 7 и 17 могут Введение анализаторов 7 и 17 коперестраиваться и фиксировать раз- да триггеров 8 и 18 установки, - личные установочные числа. По истече- элементов И-ИЛИ 9 и 19 и одновибрании времени работы первого одновиб- торов 10 и 11 позвОляет за счет ратора 10 с входа блока 6 сравнения 50 установки эталонной и контролируеснимается запрет и в случае если мой логических микросхем, не имеюI ! установка контролируемой мйкросхемы: щих специального входа установки, 1 не произошла, что соответствует ; !в одинаковое и произвольно заданное неидентичности состояния выходов,,!исходное состояние автоматически ! контролируемой 1 и эталонной 3 мик- 55 контРолиРовать такие микросхемы, !

Росхем, на выходе блока б сравне- . что Расширяет функциональные возмс ния появляется сигнал логической ности устройства.

ВНИИПИ Заказ 4553/38 Тираж

710 Подписное

Филиал ППП "Патент", r.Óìãîðîä, ул.Проектная,4