Устройство для деления п-разрядных двоично-десятичных чисел

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ . Н-РАЗРЯДНЫХ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ, содержащее вычислительный блок, 6 т л и ч а ю щ е е с я тем, что, с целью упрощения устройства и повьаиения быстродействия при делении на два, оно содержит дополнительно (п-2) вычислительных блоков (п -число десятичных разрядов), каждай из вычислительных блоков, представляет собой комбинационный сумматор« причем каждый сумматор имеет четыре даоичных разряда, первые входы разрядов сумматоров соединены с входными шянами соответствующих десятичных разрядов делюлого устройств, вторые входи рервых и третьих разрядов комбинационных сумматоров соединены с шиной сигналалогического нуля устройства , входы вторых и четвертых разрядов комбинационных сумматоров соединены с выходами первых разрядов сумкоэ предыдущих комбинацион ных сумматоров соответственно, вторые входы второго и четвертого разрядов ( )-го кокйинационного сумкагора соединены с первой входной шиной п-го десятичного разряда делимого устройства, входные шины с второй по четвертую п-го десятичного раз- § ряда делимого устройства и шина логического куля устройства соединены с выхрДньвш шинами п-го десятичного разряда частного, выходные шины кгикдого разрдда частного с первого по (п-1)-й устройства соединены с выходами разрядов суммы с второго по четвертый и выходом переноса соответствующего комбинационного суналатора.

СОЮЗ СОВЕТСКИХ

GOlLHAЛИСТИ4ЕОКИХ

РЕСПУБЛИК

p(gg G 06 F 7/52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ASTOPCklOMV СВИДЕПОЫТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО 4KAAN ИЭОБРЕТЕНИЙ И ОТНРЫТИИ (21)3411694/18-24 (22)24.03.82. (46)30.06.83. Нюл. Р 24 (72)С. Я. Шишов и A. Б. Сучкова (53) 681. 325 (088.81 (56)1. Карцев И. A. Арифметика цифровых машин, М., "Наука", 1969, с. 524-532.

2. Патент CldA Р 3735107, кл. 235-165, опублик. 1974 (прототип) . (54)(57) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ..

К-РАЗРЯДНЫХ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ, содержащее вычислительный блок, о iл и ч а ю щ е е с я тем, что, с целью упрощения устройства и повышения быстродействия при делении на два, оно содержит дополнительно (n-2 ) вычислительных блоков (n -число десятичных разрядов), каждый из вычислительных блоков, представляет собой комбинационный сумматор, причем каждый сумматор имеет четыре дво ичных разряда, первые входы разрядов,ЯО„„А сумматоров соединены с входными шинами соответствующих десятичных разря-: дов делтвюго устройства, вторые входы первых и третьих разрядов комбинационных сумматоров соединены с шиной сигнала логического нуля устройства, вторые входы вторых-и четвертых разрядов комбинационных сумма торов соединены с выходами первых разрядов суммы предыдущих комбинационных сумматоров соответственно, вторые входы второго и четвертого разрядов (n-1)-ro комбинационного сумматора соединены с первой входной шиной n-ro десятичного разряда делимо-го устройства, входные шины с второй по четвертую и-ro десятичного раз- 9 ряда делимого. устройства и шина логического нуля устройства соединены с выходными шинами и-ro десятичного разряда частного, выходные шины каждого разряда частного с первого по (n-1)-й устройства соединены с вы- р ходами разрядов суммы с второго по четвертый и выходом переноса соответствующего комбинационного сумматора.

1026139 рые входы второго и четвертого разря.дов (и-1) -ro комбинационного сумматоров соединен с первой входной шиной и-го десятичного разряда делимого устройства, входные шины с второй по четвертую n-ro десятичного разряда делимого устройства и шина логического нуля устройства соединены с выходными шинами и-го десятичного разряда частного, выходные шины каждого разряда частного с первого

no (n-1)-й устройства соединены с выходами разрядов суммы с второго по четвертый и выходом переноса соответствующего комбинационного сумматора.

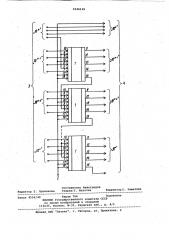

На чертеже изображена схема устройства для деления и-разрядных дво.ично-десятичных чисел.

Устройство содержит (n-1) четырехразрядных полных двоичных комбинаци,онных сумматоров 1, вычислительных блоков ., шину 2 сигнала логического нуля, входные шины 3 делимого, выходные шины 4 частного. устройство работает следующим об-, разом. и-разрядное десятичное число в двоично " десятичном коде поступает на входные шины 3 делимого..Три старших разряда двоичного кода цифры

n-ro разряда делимого являются тремя младшими разрядами двоичного кода цифры и-го разряда частного, старший разряд кода цифры п-го разряда частного равен нулю, Младший разряд двоичного кода п-го разряда делимого подается на входы 5 и б сумматора 1 (n-1)-Го разряда. Если младший разряд двоичного кода и-го разряда равен нулю, то двоичный код цифры (n-1)-го разряда делимого, поступающий на входы 7-10 сумматора

1 (n-1 )-го разряда, передается на выходы этого сумматора без изменения, и с выходов 11-14 снимается двоичный код цифры (n-1)-го разряда частного, равный половине значения цифры (n-1) -го разряда делимого. Если младший разряд 15 двоичного кода п-го разряда делимого равен единице, то в сумматоре 1 (n-1)-го разряда происходит сложение цифры (п-1)-го разряда делимого с цифрой десяти (1010), и с выходов 11-14 сумматора

1 (n-1)-го разряда снимается двоичный код цифры (n-1) -го разряда частного, равный половине значения полученной двоичной суммы. Шина 2 подключена к входам 1б-18 сумматоров 1.

Младший разряд суммы с выхода 15 сумматора 1 (и-1) -го разряда подается на входы 5 и б сумматора 1 (n-2)-ro разряда, на входы 7-10 которого подается двоичный код цифры (n-2 )-ro .разряда делимого. На выходах 11-14 сумматора 1 (и-2)-ro разряда формируИзобретение относится к вычислительной технике и может быть исполь-. зовано, в частности, в системах фор мирования кодов, а также в специализированных вычислительных устройствах статической обработки информации.

Известны устройства для деления десятичных чисел, содержащие регистры операндов, сумматоры, логические элементы, в которых очередная цифра частноГо вычисляется с помощью серии 10 вычитаний делителя из положительного остатка до получения отрицательной разности или серии сложений делителя с отрицательным остатком до получения положительной или нулевой раз- 15 ности (1 j, Наиболее близким к предлагаемому является устройство для деления п-разрядных двоично-десятичных чисел, содержащее регистр делимого, регистр20 делителя, регистр частного, блок формирования цифр частного, блок управления и вычислитель, два управляющих входа которого подключены к соответствующим выходам блока управле2ь ния, третий вход которого через блок формирования цифр частного подключен к первому входу регистра част- . ного, второй вход которого подключен к четвертому входу блока управления . З0 и к управляющему входу регистра делимого, первый выход которого подключен к первому .входу сумматора, а второй вход последнего — к первому выходу регистра делителя, выход сум- 35 матора подключен к входу регистра делимого (2).

Недостатком являются избыточность аппаратуры и низкое быстродействие при решении частной задачи деление и-разрядных двоично-десятичных чисел на два.

Цель изобретения — упрощение устройства и повышение быстродействия при делении на два. 45

Поставленная цель достигается тем, что устройство для деления и-разрядных двоично-десятичных чисел, содержащее вычислительный блок, содержит дополнительно) (n-2) вычислительных блоков (n-число десятичных разрядов), 5 каждый из вычислительных блоков представляет собой комбинационный сумматор, причем .каждый сумматор имеет четыре двоичных разряда, первые входы разрядов сумматоров соединены с 55 входными шинами соответствующих десятичных разрядов делимого устройства, вторые входы первых и третьих разрядов комбинационных сумматоров соедине» ны с шиной сигнала логического нуля б0 устройства, вторые входы вторых и четвертых разрядов комбинационных сумматоров соединены с выходами первых разрядов Суммы предыдущих комбинационных сумматоров соответственно, вто-б5

1026139 ется двоичный код цифры 1(и-2)-го разряда частного, равный половине значения цифры (n-2) -го разряда дели- мого, если младший, разряд суммы с выхода разряда 15 сумматора 1 (п-1) -го разряда равен нулю, или равный поло-. вине значения полученной суммы от сложения цифры (и-2)-го разряда делимого с цифрой десять (1010), если младший разряд суммы с выхода разряда 15 сумматора 1(n-1)-ro разряда равен единице.

Младший разряд суммы с выхода раз. ряда 15 сумматора 1 (n-2)-го разряда подается на входы 5 и 6 сумматора (n-3)-го разряда (не показан).

Формирование десятичной цифры частного (n-3) -го и последующих разрядов аналогично описанному выше формированию цифры частного (n-2)-го разряда.

Первый разряд .15 выхода суммы сумматора 1 младшего разряда свидетельствует о четности делимого. Если данный разряд равен нулю, то дели-с мое — число четное и разделилось Ha два без остатка, если разряд равен единице, то делимое число нечетное и к частному добавляется 0,5.

Например, когда на входные шины 3, подается код трехзначного десятич«, ного числа 728(0111 0010 1000), на выходных шинах 4 получается код числа 364(0011 0110 0100 О), а когда на входные шины 3 подается код.числа

729(0111 0010 1001) на выходных шинах 4 получается код числа 364,5(0011

10, 0110 0100 1) .

Предлагаемое устройство в отличие от.известных содержит меньшее число элементов, так как в нем отсутствуют регистры делимого, делителя и

15 частного, блок Формирования цифр частного и блок управления.

Быстродействие устройства определяе ся только собственным временем переключения двоичных полных четырехразрядиых сумматоров и не зависит от алгоритма Формирования цифр частного и времени переключения регистров делимого, делителя, частного, блока

5 Формирования цифр частного и блока управления.

1026139

Составитель Виноградов

Редактор E. Лушникова Техред Т. Маточка Корректор Г. Решетник

Эакаэ 4559/40 Тираж 70б Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП ."Патент", г. Ужгород, ул. Проектная, 4

< 1