Цифро-частотный умножитель

Иллюстрации

Показать всеРеферат

ЦИФРО-ЧАСТОТНЫЙ УМНО. ЖИТЕЛЬ, содержащий счетчик-делитель , : импульсов, блок сборки и блок формиро-i вателейимпульсов, первые входы которых соединены с выходами разрядов счетчикаелЕггеля импульсов, вторые входы подключены к шинам утфавляющего сигнала, а выходы соединены с входами .блокасборки, отличают и йен тем, что, с целью повышения точности, в него введены первый и второй дополнительные фор мирователи импульсов и инвертор, вход которого соединен с шиной старшего разряда утфавляющего сигнала и первым входом первого дополнительного формирователя импульсов, а -выход - с первым входом второго дополнительного формирователя импульсов, второй вход которого под. ключоа к выходу старшего разряда счетчика-делителя импульсов, третий вход соединен с шиной младшего разряда управляклцш о сигнала и вторым входом п вого дополнительного формирователя импульсов , третий Вход которого соединен с выходом счетчика-делителя импульсов, тфичем выходы дополнительных формирователей импульсов подключены к дополнитеш ным входам блока сборки.

СО1ОЗ СОВЕТСНИх О1,АДИСТИ1вжИХ . РЕСПУБЛИК аа (11):

Ц 11 Н 03 К 5 456

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

Н ASTOPCHOlUlV СВИДЕТЕЛЬСТВУ (21) 3343359/18-23. (22) 08.10.83.. (46) 30.06.83. Бюл. М 24 (.72) М. А, Гаврилюк, Т. Г. Галамай и B. Б. Дудыкевич (.71) Львовский ордена Ленина полигехнический институт им. Ленинского комсомола (S3) 62 1.374.4(088,8) (56) 3.. Акцептованная заявка Японии

34 49-740т кл. Н 03 К 5/3.56э 3.975, 2. Данчеев В, П. Бифро-частотные вы числительные устройства, М., «Энергия", 1976, введение, (54)(57) БИФРО-ЧАСТОТНЫЙ УМНО»

ЖИТЕЛЬ, содержащий счетчик-делитель

: импульсов, блок сборки и блок формиро- вателей импульсов, первые входы которых соединены с выходами разрядов счетчика-делителя импульсов, вторые входы подключены к шинам управляющего сигнала, а выходы соединены с входами .блокасборки, отличающийс ятем, что, с целью повышения точности, в него введены первый и второй дополнительные фор мирователи импульсов и инвертор, вход которого соединен с шиной старшего разряда управляющего сигнала и первым входом первого дополнительного формирова1 eas импульсов, а -выход - с первым входом второго дополнительного формирователя импульсов, второй вход которого подключен к выходу старшего разряда счетчика-делителя импульсов, третий вход соединен с шиной младшего разряда управляющего сигнала и вторым входом первого дополнительного формирователя им- ®

O пульсов, третий вход которого соединен, с выходом счетчика-делителя импульсов, причем выходы дополнительных формирователей импульсов подключены к дополнительным входам блока сборки.

1 10262

Изобретение относится к импульсной технике и предназначено для использования в устройствах функционального преобразования и коррекции информации.

Известен цифро-частотный умножитель содержащий последовательно включенные двоичный умножитель частоты и делитель. частоты t. 1 3.

Недостаток указанного устройства - огрениченноебыстродействие,так как высокая 10 точность устройства обеспечивается только за счет увеличения частоты входных импульсов, Наиболее близким к предлагаемому по технической сущности является цифрочастотный умножитель, содержащий

I счетчик-делитель импульсов, блок сборки, . шину управляющего сигнала и группу формирователей импульсов, первые входы которых соединены с выходами раз- 20 . рядов счетчика-делителя импульсов, вторые входы — с выводами шины управляющего сигнала, а выходы — с входами блока сборки 2 .

Недостатком известного устройства яв 25 ляется высокая погрешность из-за неравномерности расстановки выходных импуль. сов в цикле.

Устройство работает следующим образоме

Работа формирователей импульсов основана на принципе совпадения импульсов (импульсно-потенциальные схемы совпадения, схема совпадения с тактированием импульсами входной последовательности и т. д.), поэтому с изменением кода на .выходах счетчика-делителя 1 при заданном коде на шине 3 соответственно изменяется число формирователей 4, 6 и 7, на выходах которых появляется сигнал в моменты совпадения, что приводит к формированию на выходе блока 2 серии импульсов, пропорциональной ходу на шинах 3.

В известном устройстве выходная. импульсная последовательность в пределау, цихла существенно неравномерна. Эта неравномерность исхлючается введенными элементами: второй дополнительный формирователь 7 исключает образование импульса на выходе блока 2 в случае, когда в младшем и старшем разрядах шин 3 имеются логические «1», Импульс на выходе блока 2 может появиться только цри логическом О" в старшем разряде шин 3,. логической "1" в младшем его разряде и при переходе старшего разряда счетчика-делителя 1 с «О» .в «l.». Исключенный таким образом импульс переставляется в пределах цикла с помощью первого дополнительного формирователя 6.

На выходе этого формирователя появля-, ется импульс при наличии в старшем и младшем разрядах., шин 3 логических

1" и переходе старшего разряда счетчика-делителя 1 с "1» в О".

Цель изобретения - повышение точности устройства.

Уъ

Поставленная цель достигается тем, что в устройство, содержащее счетчикделитель импульсов, блок сборки и блок формирователей импульсов, первые входы

35 которых соединены с выходами разрядов счетчика-делителя импульсов, вторые, входы подключены к шинам управляющего

1 сигнала, а выходы соединены с входами блока сборки, введены первый и второй

40 дополнительные формирователи импульсов и инвертор, вход которого соединен с

l шиной старшего разряда управляющего сигнала и первым входом цервого дополнительного формиро45 вателя импульсов, а выход - с первым входом второго дополнительного формирователя импульсов, второй вход которого подключен к выходу старшего разряда счетчика-делителя импульсов, третий вход 50 соединен с шиной младшего .разряда уп- . равляющего сигнала и BTopbiM входом первого дополнительного формирователя импульсов, третий вход которого соединен с выходом -счетчика-делителя импульсов, 55 причем выходы дополнительных формирователей. импульсов подключены к дополнитель. ным входам блока сборки.

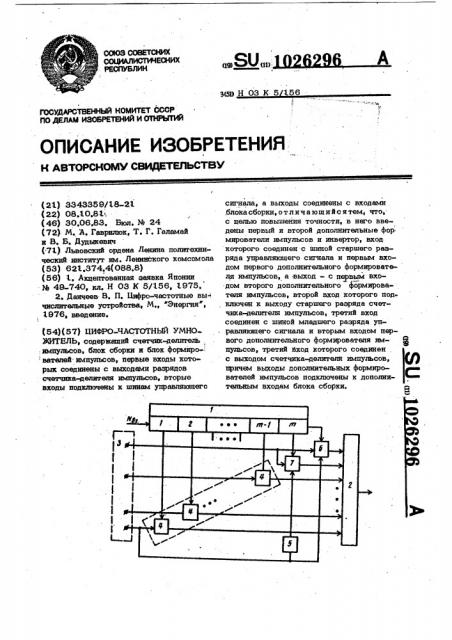

На чертеже представлена структурная схема предлагаемого устройства.

Бифро-частотный умножитель содержит счетчик-делитель 1 импульсов, блок 2 сборхи, шины 3 управляющего сигнала, блок формирователей 4 импульсов, инвертор 5, первый дополнительный формирователь 6 импульсов и второй дополнительный формирователь 7 импульсов.

Точность предлагаемого устройства равна точности известного, у которого разрядность выше на единицу, т. е. для обеспечения известного устройства той же точности умножения необходимо в два раза увеличить его емкость, а следовательно, и время преобразования, Преимуществом предлагаемого устройства является симметричность гистограммы з 1026296 4 пегрешностей, что позволит существенно Указанные преимущества достигнуты повысить точность построенных на его практически без усложнения устройства основе функциональных преобразователей. и без снижения других его показателей.

Составитель А.- Поддубный

Редактор С. Квятковская Техред И,Гайду Корректор Ю, Макаренко

Заказ 4575/48 Тираж 936 Подписное

ВНИИПИ Государственного комитета СССР по делам. изобретений и открытий

1 L3035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП «Патент, г. Ужгород, ул. Проектная, 4