Преобразователь параллельного кода в число-импульсный код

Иллюстрации

Показать всеРеферат

COOS СОВЕТСКИХ эе ю

РЕСПУБЛИК

З(Щ) G 06 Г 5 04

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И ABT0PCHOMV СВИДЕТЕЛЬСТВУ (2I) 3290207/18-24. (22) 19. 03 81 (46) 07,07.83. Бюл. В 25. (72) 3,В.Ивановская., A.Ô.Nàõoòà, Д.К.Михнов и В.П.Рудавин (71) Харьковский институт радиоэлектроники (53) 681.325(088.8) (56) 1 Авторское свидетельство СССР.

Р 343264, кл. С 06 F 5/04, 1971.

2. Авторское свидетельство ССС

9549802, кл. &06 F 5/04, 1974 (прототип) . (54) (57) 1. ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ЧИСЛО-ИМПУЛЬСНЫЙ

КОД, содержащий регистр, вычитающий счетчик, генератор импульсов, дешиф- ратор нуля, первый триггер, первый элемент ИЛЙ, первый элемент И, первый вход которого соединен с единичным выходом триггера, являющимся потенциальным выходом преобразователя, информационные входы которого соединены с входами регистра, выходы которого соединены с информационными ! вхопамн вычитающего счетчика, выходы которого являются разрядными выходами преобразователя и соединены свходами дешифратора нуля, выход которого соединен с первым входом первого элемента ИЛИ,.выход которого соединен с управляющим входом вычитающего счетчика и к -входом первого триггера, отличающийся тем, что, с,целью расширения области примене ния преобразователя путем циклического повторения и автоматического изменения частоты ".актовых импульсов, в него введены. времязадающий блок, второй триггер, второй и третий элементы ИЛИ и элемент запрета, выход которого соединен с 5-входом первого триггера, запрещающий вход соединен с выходом дешифратора нуля, а разрешающий вход элемента эайрета соединен с выходом второго элемента ИЛИ, первый вход которого соединен.с 5 -входом второго тригге-.,SU„„A ра и является входом пуска преобра- хзователя «второй вход второго элемента ИЛЙ Соединен с информационным выходом времязадающего блока, тактовый вход которого соединен с выходом генератораимпульсов и вторым входом первого элемента И, третий вход которого является управляющим входом преобразователя и соединен с управляющим входом времязадающего блока, тактовый выход которого соединен с третьим входом второго з=eмента ИЛИ и .с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом первого элемента .И, а Выход соединен с тактовым вхо дом вычитающего счетчика и является 9,, тактовым выходом преобразователя, стоповый вход которого соединен с:

: P, -входом второго триггера, единичный выход которого соединен с входом блоки- t ровки времязадающего блока, а нулевой выход второго триггера соединен с вто Я . рым входом первого элемента ИЛИ.

2. Преобразователь по и. 1, о тл и ч а ю шийся тем, что ьеремязадающий блок содержит счетчик, два эле мента И,.два элемента НЕ и элемент ИЛИ, первый и второй входы которого соединень аа,) соответственно с выходами первого и второго элементов И, являющимися тактовым и.информационными выходами )иииВ времязадающего блока соответственно, д третий вход элемента ИЛИ соединен с выходом первого инвертора, вход которого является входом блокировки времязадающего блока, а выход элемента ИЛИ соединен с R-входом счетчика, тактовый вход которого является тактовым входом времяэадающего блока, управляющий вход которого соединеп с входом второго элемента НЕ, первые входы первого и второго элементов И соединены соответственно с входом и выходом второго элемента НЕ, а .остальные входы первого и второго элементов И соединены с выходами счетчика, 1027714

Изобретение относится к цифровой автоматике и контрольно-измерительной технике и предназначено для циклического преобразования параллельногр кода в число-импульсный код и временной интервал. 5

Известен преобразователь параллельного двоичного кода в число-импульсный код, содержащий регистр, счетчик, параллельные входы которого соединены с входными шинами, входа. — 30 ми регистра и входами элемента ИЛИ, выход которого соединен с входом элемента задержки, первый выход которого соединен с первым входом первого элемента И, .выход которого сое- 5 динен с одним из входов элемента

ИЛИ и выходной шиной; выход элемента ИЛИ соединен с нулевым входом триггера, и второй элемент И (1 1.

Недостаками данного преобразователя являются его сложность и невозможность циклического преобразования параллельного кода в число-импульсный код.

Наиболее близким к предлагаемому по технической сущности и схемному построению является преобразователь параллельного кода в число-импульсный код, содержащий вычитающий счетчик, входы которого соединены с входами элемента ИЛИ, параллельными входами Э0 преобразователя и входами регистра,. выходы — с входами дешифратора нуля, а выход вычитания — с одним из входов .элемента ИЛИ, выходом преобразователя и выходом элемента И, первый вход j35 которого соединен с выходом триггера, вход которого соединен с выходом дешифратора нуля, а вход — с выходом элемента ИЛИ и входом элемента задержки, первый выход которого сое- 40 динен с дополнительным входом дешиф-. ратора нуля, а второй выход — с вторым входом элемента И 12 .

Недостаток известного преобразователя состоит в том, что он не позволяет осуществлять циклическое преобразование параллельного кода в число-импульсной код, а также формирование циклических временных интервалов.

Цель изобретения - расширение об- ласти применения преобразователя путем циклического повторения преоб разования и автоматического изменения частоты таКтовых импульсов.

Поставленная цель достигается тем, что в преобразователь параллель ного кода в число-импульсный код, содержащий регистр, вычитающий счет«. чик, генератор импульсов, дешифратор нуля, первый триггер, первый эле- 60 мент HJIH, первый элемент И, первый вход которого соединен с единичным выходом триггера, являющимся потенциальным выходом преобразователя, ин"

Формационные входы которого соединены45 с входами регистра, выходы которого соединены с информационными входами вычитающего счетчика, выходы котороrо являются разрядными выходами преобразователя и соединены с входами дешифратора нуля,, выход которого соединен с первым входом первого элемента ИЛИ, выход .которого соединен с .управляющим .входом вычитающего счетчика и Р-входом. первого триггера,.введены. времязадающий блок, второй триггер, второй и третий элементы .ИЛИ и элемент запрета, выход которого соединен с Й -входом первого триггера, запрещающий вход соединен с выходом дешифратора нуля,, а разрешающий вход элемента запрета соединен с.выходом второго элемента ИЛИ., первый .вход которого .соединен,с S —входом второго триггера и является входом пуска преобразователя, второй вход .второго .элемента ИЛИ соединен с.информационным выходом времязадающего блока,.тактовый вход которого соединен с выходом генератора импульсов и вторым входом первого элемента И, третий вход .которого яв;, ляется управляющим входом .преобразователя и.соединен с управляющим вхо» дом времязадающего блока, тактовый выход которого соединен.с третьим входом второго элемента ИЛИ и первыМ входом третьего элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, .а выход соединен с тактовым, входом вычитающего счетчика и является .тактовым выходом преобразователя, стоповый выход которого соединен с Й -входом второго триггера, единичный выход. которого .соединен с входом блокировки времязадаюшего блока, а нулевой выход второго триггера соединен с вторым входом первого элемента ИЛИ.

Кроме того, времязадающий блок со- держит счетчик, два элемента И, два элемента НЕ и элемент ИЛИ, первый и второй входы которого соединены соответственно с выходами первого и второго элементов И, являющимися тактовым и информационным выходами времязадающего блока соответственно,. третий вход элемента ИЛИ соединен с выходом первого инвертора, вход которого является входом блокировки времязадающего блока, а выход элемента ИЛИ соединен с Р-входом счетчика, тактовый вход которого является тактовым входом времязадающего блока, управляющий вход которого соединен с входом второго,элемента БЕ, первые входы первого и второго элементов И соединены соответственно с входом и выходом второГо элемента НЕ, а остальные входы первого и второго элемента И соединены с выходами счетчика .

1027714

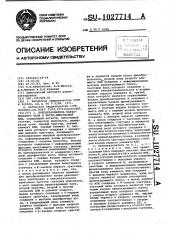

На фиг.l приведена структурная схема преобразователя параллельного кода s число-импульсный код; на

Фиг.2 - блоксхема времязадающего блока на фиг,3 - времеНные диаграм ваа.его,работы. 5

В состав .преобразователя входят первый..элемент ИЛИ 1, времязадающий блок 2, генератор 3 импульсов, триггер 4, элемент 5 запрета, второй элемент ИЛИ б, триггер 7 эле- 10 мент И 8, третий элемент ИЛИ 9, дешифратор 10 нуля„ вычитающий счетчик

1l регистр 12,.управляющий вход

13:, входы 14 ..пуска, стоповый вход .

15, информациоиные входы 16, такто:вый выход 17, потенциальнный выход .18.и разрядные выходы 19 преобразователя.

Блок-схема времязадающего блока содержит счетчик 20.первый 21 и второй 22 элементы И, элемент НЕ 23, элемент ЙЛИ 24, элемент НЕ 25, тактовий вход 25 и вход 27 блокировки.

Предлагаемый преобразователь работает следующим образом .

В исходном состоянии триггеры 4 и 7 находятся в нулевом состоянии. уровнем.с нулевого выхода триггера

4 s вычитающий счетчик записано значение преобразуемого параллельного кода с выходов регистра 12.

Сигиалом Пуск на входе 14 триггер 4 устанавливается в единичное состояние, включая времязадающий блок 2. Если содержимое вычитающего ° счетчика 1 не равно нулю, то триггер35

7 устанавливается в единичное состояние и иа выходе 18 появляется высокий уровень. При высоком уровне иа.входе 13 сигнал иа информационном выходе.времязадающего блока.2 отсутствует, а импульсы с .выхода генератора З,импульсов поступают через элемент И.и третий элемент ИЛИ 9 на тактовый выход 17 .и на первый вход вычитаккцего счетчика 11, уменьшая 45 каждый раз.его содержимое на единицу, Когда содержимое вычитающего счетчика 11 станет равным нулю, сигналом с выхода дешифратора 10 нуля через первый элемент ИЛИ 1 триггер 7 сбрасы.вается, а в вычитающий счетчик.ll снова производится запись преобразуемого кода. При этом на выход 18 выделяется низкий уровень, а импульсы на тактовом выходе 17 и входе счетчика ll отсутствуют. По истечении 55 временного интервала, формируемого времязадающыа блоком 2, íà его первом выходе появляется импульс, устанавливающий через второй элемент

ИЛИ б и элемент 5 запрета (если 60 значение преобразуемого кода не равно нулю) триггер 7 в единичное состояние. Описанный цикл повторяется.

Низкий уровень на входе 13 переводит преобразователь в ре:зим циклического преобразования параллельного кода в эквивалентный временной интервал (на выходе 18)< При этом на тактовом выходе времязадающего блока

2 сигнал отсутствует, а.на втором его выходе формируются импульсы

) времени. Работа преобразователя про-,. текает аналогично описанному.Информация с параллельных выходов

19 преобразователя может быть выведена на устройство индикации.

Сигналом.на входе 15 Стоп триггер 4.управления. возвращается в исходное состояние, преобразователь выключается..

Таким образом, преобразователь обеспечивает цикличность преобразования параллельного кода в число-импульсный код, а также формирование циклических временных интервалов.

Работа времязадающего блока 2 основана на установке требуемого коэф фициента пересчета для счетчика 20.

Коэффициенты пересчета К1 и К2,уста-. навливаемые с помощью первого .21 и второго 22 элементов И соответственно определяются подключенными выходами счетчика 20 к.входам указанных элементов И.

Низким уровнем на блокирующем входе времязадающего блока счетчик

2С.заторможен и находится в нулевом состоянии. При поступлении на этот вход. высокого уровня счетчик 20 начинает подсчет импульсов, поступающих на тактовый- вход времязэдающего -. блока..Если на управляющем входе

13 — низкий уровень, первый элемент "

И 21 выключен, а по достижении счетчиком 20 состояния К2, на выходе второго элеменТа И 22 появляется импульс,.устанавливающий счетчик 20 в нулевое состояние, после чего цикл повторяется, пока на входах 13 или

27 изменится управляющий сигнал. При этом.на.выходе 28 времяэадакицего блоха импульсы отсутствуют, а на выходе

29.формируются импульсы с периодом

Т2 ° ., Т2 = К2 .ЛГ.

Если на входе 13 времязадающего блока высокий. уровень, 10, второй элемент И 22 выключен, а на выходе

28 появляются импульсы с периодом .Tl

Tl < Kl - ЬТ

Преобразователь параллельного кода в число-импульсный код может быть применен как в составе других устройств, так и самостоятельно для циклического преобразования параллельного кода в число-импульсной код и формирования времени интервалов. Так при управлении движением судна применение преобразователя позволяет повысить безопасность морИплавания путем снижения утомляемости судоводителя, что.достигается

1027714 освобождением его от необходимости вести постоянный контроль времени.

Преобразователь может быть применен и в установках дозирования. При этом дозированне .осуществляется порциями, величина которыя определяется параметрами импульсов на импульсном выходе преобразователя (например длительность). Количество порций определяется значением параллельного кода на направленных входах преобразователя. Управление доватором осуществляется сигналом с.импульсного выхода преобразователя.

Предлагаемый преобразователь позволит упростить сопряжение циФровых систем автоматики, управлянщих технологическими процессами, с исполнительными механизмами.

1027714

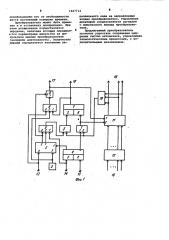

si гам би ПЯ

Юх ИД)

Аю 8®й)

Ющг ЩФ )

Составитель М. варшавский

Редактор A.Âîðîâè÷ ТехредЛ. Пекарь . Корректор В.Бутяга

Заказ 4741/53 Тираж 706 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП Патент, r,Óæroðîä, ул,Проектная,4