Устройство для сравнения кодов

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ КОДОВ/ содержащее счетчик, группу элементов Неравнозначность, элемент Неравнозначность, регистр , причем выходы разрядов счетчика соединены с первыми входами элементов Неравнозначногть группы , вториле входы которых соединены с входами первой группы устройства, отличающееся тем, что, с целью упрсяцения оно содержит блок памяти,, двухразрядный сдвигающий регистр, дешифратор, группы элементов И,- И-ИЛИ-и счетный триггер, причем первые информационные входы элементов И-ИЛИ группы соединены с соответствующими выходами элементов Неривнозначность группы, вторые информационные входы - с выходами разрядов счетчика, выходы элементов И-ИЛИ группы соединены с ад ресньши входами блока памяти, выходы которого соединены с информационными входами двухразрядного сдвигающего регистра , выходы которого соединены с входами элемента Неравнозначность , инверсный выход счетного триггера соединен с первыми управляющими входами элементов И-ИЛИ группы, прямой выход счетного триггера:соединен со счетным входом счетчика,- вторыми управляющими входами элементов И-ИЛИ группы и первым стробируюиим входом деО ) шифратора, входподачи таттовых импульсов устройства соединен с входок счетнего триггера,синхронизируквдимвходом двухразрядного сдвигающего регистра .и вторым стробируншим входом дешифрс З тора, выход элемента,Неравнозначность соединен с управляющими входами элементов И группы, информационные входы которых соединены с выходами дешифратора, информационные входы дешифратора соединены с выходами разрядов счетчика.

«9) «И.

СОЮЗ СОВЕТСКИХ

ОЯ.ЮЛИ

РЕСПУБЛИК

3(5В G, 06 t-" 7 04

ОПИСАНИЕ ИЗОБРЕТЕНИЯ и автаоснаьм авидатвъству

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3396079/18-24 (22) 19,02,82 (46) 07.07.83. Бюл. 9 25 (72) И.Ф.Холодный, Н.Г.Коробков, В.Ю.Ларченко и К.К;Фурманов (71) Харьковский ордена Ленина авиационный институт им. Н.Е.Жуковского ,(53) 681.325(088.8) (56) 1. Патент СШЛ В 4168487, кл. Q 06 F 7/04, опублик. 1979.

2. авторское свидетельство СССР

rto заявке Ф 3394392/18-24, кл. С, 06 F 7/04, 1982 (прототип). (54)(57) УСТРОВСТВО ДЛЯ СРАВНЕНИЯ

КОДОВ, содержащее счетчик, группу элементов Неравнозначность, элемент Неравнозначность, регистр, причем выходы разрядов счетчика соединены с первыми входами элементов Неравнозначность группы, вторые входы которых соединены с входами первой группы устройства, о т л и ч а ю щ е е с я тем, что, с целью упрощения оно содержит блок памяти,.двухразрядный сдвигающий регистр, дешифратор, группы элементов И, И-ИЛИ и счетный триггер, причем первые информационные входы элементов И-ИЛИ группы соединены с соответствующими выходами элементов Неравнозначность™ группы, вторые информационные входы - с выходами. разрядов счетчика, выходы элементов

И-ИЛИ группы соединены с адресными входами блока. памяти, выходы которого соединены с информационными входа" ми двухраэрядного сдвигающего регистра выходы которого соединены с вхоf

31 It дами элемента Неравнозначность инверсный выход счетного триггера соединен с первыми управляющими входами элементов И-ИЛИ группы, прямой выход счетного триггера соединен со счетным входом счетчика, вторыми управляющими входами элементов И-ИЛИ I группы и первым стробируюшим входом де шифратора, вход подачи та "ToBUx импульсов устройства соединен с входом счет- ного триггера, си хрониэирунщим входом двухразрядного сдвигающего регистра и вторым стробируюшим входом дешифра)а тора, выход элемента, Неравнозначность соединен с управляющими входами элементов И группы, информационные входы которых соединены с выходами дешифратора, информационные входы дешифратора соединены с выхода ми разрядов счетчика.

1027715

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств тестового и аппаратурного . контроля цифровых устройств.

Известна схема сравнения кодов, содержащая элементы Неравнозначность 1 3, Недостатком устройства является невозможность вычисления булевой разности. 10

Наиболее близкой к предлагаемой является схема сравнения кодов, содержащая регистр, группу элементов Неравнозначность, счетчик, !5 два коммутатора, элемент Неравнозначность, причем первые входы группы элементов Неравнозначность являются входами первой группы схемы, выходы счетчика соединены с вторыми yg входами элементов "НеравнозначнО -ь" группы и управляющими входами первого коммутатора, информационнь|е входы которого являются входами второй группы схемы и соединены с инфор- 2 мационными входами второго коммутатора, управляющие входы второго коммутатора соединены с выходами элементов Неравнозначность группы, а выходы первого и второго коммутаторов соединены с первыми и вторым вхддами элемента Неравнозначность выход которого подключен к входу регистра, тактовый вход которого соединен со счетным входом счетчика и тактовым входом устройстве, выходы регистр ра являются выходами устройства (2 j.

Недостатком данного устройства . является сложность, поскольку для его реализации требуются ° два.ком- 4О мутатора с числом информационных входов 2, а также регистр для и хранения исходной функции с числом

2", где ь- число переменных, от которых зависит исходная функция. 4

Данный недостаток обусловлен тем, что в устройстве принято параллельное хранение исходной функции на всех наборах входных переменных, хотя применяется последовательная обработка каждого набора.

Цель изобретения — упрощение уст ройства.

Поставленная цеЛь достигается тем, что устройство для сравнения кодов, содержащее счетчик, группу элементов Неравнозначность, элемент Неравнозначность, регистр,причем выходы разрядов счетчика соединены с первыми входами элементов Неравнозначность группы, 60 вторые вхоМы которых соединены с входами первой группы устройства, содержит блок памяти, двухразрядный сдвигающий регистр, дешифратор, группы элементов И, И-ИЛИ и счетный триггер, причем первые информационные входы элементов И-ИЛИ группы соединены с соответствующими выходами элементов Неравнозначность группы, вторые информационны входы — с выходами разрядов счетчика, выходы элементов И-ИЛИ группы соединены с адресными входами блока памяти, выходы которого соединены с инфррмационными входами двухразрядного сдвигающего регистра, выходы которого соединены с в.юдами элемента Неравнозначность, инверсный выход счетного триггера соединен с первыми управляющИми входами элементов И-ИЛИ группы, прямой выход счетного триггера соединен со счетным входом счетчика, вторыми управляющими входами элементов И-ИЛИ группы и первым стробирующим входом дешифратора, вход йодачи тактовых импульсов устройства соединен с входом счетного триггера, синхронизирующим входом двухразрядного сдвигающего регистра и вторым стробирующим входом дешифратора, выход элемента Неравнозначность соединен с управляющими входами элементов И группы, информационные входы которых соединены с выходами дешифратора, информационные входы дешифратора соединены с выходами разрядов счетчика.

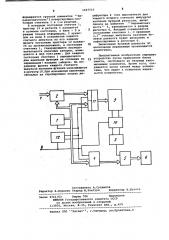

На чертеже приведена структурная схема сравнения кодов. устройство содержит счетчик 1, группу элементов Неравнозначность

2, элемент Неравнозначность 3, дешифратор 4, группу элементов И 5, регистр 6 для хранения результата, группу входов 7, вход 8 подачи счетных импульсов, блок 9 памяти, двухраэрядный сдвигающий регистр 10, группу элементов И-ИЛИ 11 и счетный триггер 12.

Значения исходной функции иа всех наборах входных переменных хранятся в блоке 9 памяти, который имееторганиниэацию 2 х 1 бит. . Адрес каждой ячейки блока 9 совпадает с соответствующим набором входных переменных, а содержимое этой ячейки равно значению функции на данном наборе.

На группу входов 7 подается ь-разрядный двоичный код, несущий информацию о. том, но какой переменной вычисляется булевая разность. Наличие в с-м разряде кода логической 1 . свидетельствует о вычислении булевой разности по этой переменкой. Адис ячейки блока 9 формируется с помощью счетчика 1, группы элементов Неравнозначность 2, триггера 12 и группы элементов И-ИЛИ 11. Если триггер. 12 находится в единичном состоянии, то адрес ячейки блока 9.определяется состоянием счетчика 1, а если триггер 12 находится в нулевом состоянии, то адрес ячейки блока 9

1027715

Составитель A.Ñósäàëîâ

Редактор A.Âîðîâè÷ Техред М.Коштура Корректор В.Бутяга

Заказ 4741/53 Тираж 706 Подписное

ВНИИПИ Государственного комитета СССР по долам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП Патент, г.ужгород, ул.Проектная,4 формируется группой элементов Не-: равнозначность" 2 инвертирукщих состояние счетчика 1 в i--м разряде;

В исходном состоянии счетчик 1, триггер 12 и регистр 6 находится в нулевом состоянии, а блок - 9 в режиме чтения ййформации, С прихо" дом на вход 8 устройства каждого счетного импульса по его заднему фронту состояние триггера 12 меняется на противоположное, а состояние tO счетчика 1, генерирующего последовательность двоичных наборов, изменяется в два паза, реже . для каждого состояния счетчика 1 определяются два значения функции на соседних по переменной i входных наборах. По пе. редиему» фронту каждого счетного импульса значения функцйи записываются в регистр 10.При совпадении единичных сигналов на стробирующих входах дешифратора 4 (что выполняется для каждого второго счетного импульса) значение булевой разности, вычис. ленное на элементе Неравноэначность 3, записывается s разряд регистра 6, который определяется состояниЕм счетчика 1. С приходом

2,2 счетных импульсов значение булевой разности будет вычислено и зафиксировано в регистре 6.

Вычисление булевой разности по нескольким переменным производится аналогично.

Предлагаемое изобретение упрощает устройство путем применения блока памяти, состоящего из матрицы запоминающих элементов. Кроме того, сокращается число связей между элементами, что ведет к повышению надежности устройства.