Цифровой функциональный преобразователь

Иллюстрации

Показать всеРеферат

ЦИФРОВО ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий два входных .регистра, три блока памяти, семь промежуточных регистров, два сумматора, блок синхронизации и выходной регистр, причем вых&д блока синхронизации соединен с управляющими входами всех регистров, выход первого входного регистра соединен с информационным входом первого промежуточного регистра и через пэрвый блок памяти с информационным входом второго промежуточного регистра, выход второго блока памяти соединен с информационным входом третьего промежуточного регистра, выход которого соединен с первым входом первого сумматора, выход которого соединен , с информационным входом выходного регистра, отличающийся тем, что, с целью повышения быстродействия , в него введены коммутатор, триггер и два блока памяти, причем выход второго входного регистра через третий блок памяти соединен с информационным входом четвертого промежуточного регистра, выход которого соединен с первым входом второго сумматора , второй вход и выход которого соединены соответственно с выходом второго промежуточного регистра и информационным входом пятого промежуточного регистра, выход которого через четвертый блок памяти соединен с информационным входом шестого промежуточного регистра, прямой и инверсный выходы которого соединены соответственно с о первым и вторым информационными вхоkn дами коммутатора, выход которого соединен с вторым входом первого сумматора , выход первого промежуточного регистра соединен с информационным входом седьмого промежутомного регист ра, выход которого соединен с вхо дами второго и пятого блоков памяти, 1C выход пятого блока памяти соединен к с информационным входом триггера, синхровход и выход которого соединены соответственно с выходом блока, ОО tC синхронизации и управляющим входом коммутатора. .

(19) OD

СОНИ СОВЕТСНИХ

СОЦИАЛИС1ИЧЕСИИХ

РЯСПУБЛИН у G 06 F 15/31

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБЙ=ТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Й АВТОРСКОМ-,К СВИДЕТЕЛЬСТВУ (21) 3403780/18-24 (22) 02.03.82 (46) 07.07.83. Ьюл. 25 (72) А.А. Мельник (53) 681.325(088.8) (56) 1. Авторское свидетельство СССР

1 674032, кл. 4 06 Р 15/31 1979..

2. Авторское свидетельство СССР по заявке Й 2911475/18-24, кл. G 06 F 15/31, 1980 (прототип). (54)(57) ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ

ПРЕОБРАЗОВАТЕЛЬ, содержащий два входных ,регистра, три блока памяти, семь промежуточных регистров, два сумматора, блок синхронизации и выходной регистр, причем выход блока синхронизации соединен с управляющими входами всех регистров, выход первого входного регистра соединен с информационным входом первого промежуточного регистра и через первый блок памяти с информационным входом второго-промежуточного регистра, выход второго блока памяти соединен с информационным входом третьего промежуточного регистра, выход которого соединен с первым входом первого сумматора, выход которого соединен. с информационным входом выходного регистра, о т л и ч а ю щ и " с я

:тем, -что, с целью повышения быстродей" ствия, в него введены коммутатор, триггер и два блока памяти, причем выход второго входного регистра через третий блок памяти соединен с информационным входом четвертого промежуточного регистра, выход которого соединен с первым входом второго сумматора, второй вход и выход которого соединены соответственно с выходом второго промежуточного регистра и информационным входом пятого промежуточного регистра, выход которого через четвертый блок памяти соединен с информационным входом щестого промежуточного регистра, прямой и инверсный выходы которого соединены соответственно с первым и вторым информационными sxoдами коммутатора, выход которого соединен с вторым входом первого сумматора, выход первого промежуточного регистра соединен с информационным входом седьмого промежуточного регист ра, выход которого соединен с вхо" дами второго и пятого блоков памяти, {,", выход пятого блока памяти соединен (Я с информационным входом триггера, а ф синхровход и выход которого соединены соответственно с выходом блока синхронизации и управляющим входом коммутатора..

1027

Изобретение относится к вычислительной технике и может быть использовано в качестве специализированного процессора вычислительной системьг высокой производительности для вычисления функций одного переменного.

Известно устройство для вычисления элементарных функций, содержащее семь сумматоров, три регистра числа, ре- 1о гистр аргумента, регистр остатка, два блока округления, тринадцать элементов.И, два блока умножения, семь элементов ИЛИ, восемь блоков сравнения и четыре счетчика.. Работа устройства выполняется в виде последовательности итераций, причем в каждой итерации выполняется несколько умножений (1 j.

Недостатком устройства является низкое быстродействие.

Наиболее близким к предлагаемому техническим решением является конвейерное устройство для вычисления элементарных функций, содержащее пят- 5 надцать регистров, три блока постоянной памяти ПЗУ, два блока умножения, два сумматора и блок управления. Данное устройство работает по конвейерному принципу. Его быстродействие при 30 обработке массивов чисел определяется временем умножения двух чисел на блоке умножения $2 ).

Однако в задачах цифровой .обработки данных сейсморазведки, радионавигации, результатов Физических экспериментов и т.д, где требуется многократное вычисление Функций одного переменного, в частности элементарных Функций, возникает необходимость 4О дальнейшего повышения производительности обработки. Это связано.как с возрастанием объемов обрабатываемых данных, так и с появлением новых алгоритмов обработки, реализация которых на медленных цифровых устройствах невозможна. Таким образом, быстродействие известного устройства уже не является удовлетворительным.

Цель изобретения - повышение быстродействия.

Поставленная цель достигается тем, что в цифровой функциональный преобразователь, содержащий два входных регистра, три блока памяти, семь промежуточных регистров, два сумматора, блок синхронизации и выходной регистр, причем выход блока синхронизации соединен с управляющими входами всех регистров, выход первого входного регистра соединен с информационным входом первого промежуточного регистра и через первый блок памяти с инфор мационным входом второго промежуточного регистра, выход второго блока памяти соединен с информационным вхо»ром третьего промежуточного регистра,выход которого соединен с первым входом первого сумматора, выход которого соединен с информационным входом выходного регистра, дополнительно введены коммутатор, триггер и два блока памяти, причем выход второго входного регистра через третий блок памяти соединен с информационным входом четведтого промежуточного регистра, выход которого соединен с первым входом второго сумматора, второй вход и выход которого соединены соответственно с выходом второго промежуточного регистра и информационным входом пятого промежуточного регистра, выход которого через четвертый блок памяти соединен с информационным входом шестого промежуточного регистра, прямой и инверсный выходы которого соединены соответственно с первым и вторым информационными входами ком.мутатора, выход которого соединен с вторым входом первого сумматора, выход первого промежуточного регист." ра соединен с информационным входом седьмого промежуточного регистра, выход которого соединен с входами вто" рого и пятого блоков памяти, выход пятого блока памяти соединен с информационным входом триггера, синхровход и выход которого соединены соответственно с выходом блока синхронизации и управляющим входом коммутатора.

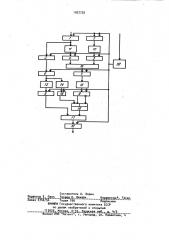

На чертеже представлена блок-схема преобразователя.

Преобразователь содержит регистры 1-10, блоки 11-15 памяти, сумматоры 16 и 17, триггер 18, коммутатор 19, блок 20 синхронизации.

Преобразователь производит вычисление произвольной функции F(x > 0 < х (1, по формуле Тейлора с использованием двух членов ряда:

Р(Xj 7=(К )+аХF (Xpj, где х = О,х . ..,х„0...0 - число, образованное старшими разрядами аргумент,в;

Ьх = 0,0...0х„+„,. х „- число, образованное младшими разрядами аргумента.

27732 4

3 10

Погрешность этой формулы можно сде" лать выходящей за пределы разрядной сетки путем соответствующего выбора параметра К.

Приращение Ьх F (х )вычисляется по формуле

QX F (ХО )-В1 п(Г (хО)) х (Ч2дХ+«t t F ("o)I)

«2

1 где функция

1, если х > О, 51(п = О, если х О, 1, если х <О, Для выполнения преобразований .

xp F(x )р хо F (хо)р дх 1офдх

2 ?, где 2 = 1о 2дх + 1ос /F (õoÖ

+p ls1gn /F (х )/исяользуются блоки 11-15 памятй. Случай Е (Х„)= О и дх = О учитывается тем, что в качестве соответствующих им значений

1ос /F (õ, )/и 1оо дх в таблицах берутся столь большие по абсолютной . величине отрицательные числа, что по« лученный результат выходит за пределы разрядной сетки.

Устройство работает следующим образом.

В первом такте в регистр 1 записывается число хО> а в регистр 2число дх. По данным числам из блоков 11 и 12 памяти считываются соответственно значения 1ос 2 /F (õ0)/ и 1ос 2 дх .

Во втором такте эти значения записываются соответственно в регистры 4 и 5, а в регистр 3 переписывается содержимое регистра 1. На сумматоре 16 осуществляется сложение содержимого регистров 4 и 5.

B .третьем такте число из сумматора 16 записывается в регистр 7, а в регистр 6 переписывается содержимое регистра 3. По содержимому данного регистра из блоков 13 и 14 памяти считываются соответственно значения хо) u Sign /F (õî)I(.Èo содержимому регистра 7 из блока 15 памяти считы" вается значение 22, т.е. íà его выходе получается число, равное произведению Йх / (х< )/

В четвертом такте считанные иэ блоков 13-15 памяти значения записываются соответственно в регистр 8, триггер 18 и регистр 9. На сумматоре 17 производится сложение содержимого регистров 8 и 9, т.е. формируется значение F(x ). Причем, содержимое регистра 9, поступает на второй вход сумматора 17 в прямом или обратном коде, в зависимости от seaxaF(x ), хранимого в триггере 18, что позволяет производить операцию вычитания.

В пятом такте полученное значение записывается в регистр 10, а иэ него поступает на выход устройства.

Разделение устройства регистрами позволяет его ступеням работать неза1О висимо. Поэтому, как только результат обработки одного элемента массива из одной. ступени передается в следующую, в данную ступень уже поступают результаты обработки второго элемента массива. Управление работой данным устройством сводится к выработке тактовых импульсов, подвигающих промежуточные результаты от регистров одной ступени в регистры следующей ступени.

Тактовые импульсы вырабатывает блок 20 синхронизации, который содержит генератор тактовых импульсов и схем пуска и останова, пропускающие или запрещающие прохождение тактовых импульсов на регистры устройства.

Устройство работает по конвейерному принципу, поэтому его быстродействие определяется длительностью такта, равной задержке в наиболее медленной ступени, т.е.

Г = с„„+ < 1,„, с . где 1 -, время суммирования на сумматоре;

4к - задержка информации коммута35 тором.

Быстродействие же прототипа равно .Как известно, операция умноженйя значительно медленнее операции сложения, в частности при исполь4О эовании наиболее быстродействующего многослойного перемножителя и сумматора с ускоренным переносомМ„ „.=

= 4t . Таким образом, предлагаемое устройство значительно превышает по

4 производительности прототип.

Общий объем блоков памяти уст" ройства различен для разных функций, в частности при разрядности обрабатываемых чисел Ь = 16 для функции Sin, 9 - =15 кбит, для функции

ЧГх, Я = 22 кбит..

На приведенной структуре можно реализовать любые функции одного переменного, если эти функции принадлежат к классу дважды непрерыва но дифференцируемых. При этом в ПЗУ необходимо иметь коэффициенты для всех функций, или заменять блоки ПЗУ если реализуются отдельные функции.

1027732

Составитель А. Зорин

Редактор E. Папп Техреа Л. Пекарь КорвекторА. Тяско

» » » е »г ° ЪГ ° фй»»»»

Заказ 4742/54 Тираж 706 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1130»35 Москва Х-35 Раушская наб. а. 4/5

» »»» » юй «» В э»й »»«»Аю »tc»

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4