Цифроаналоговый функциональный преобразователь со степенной характеристикой

Иллюстрации

Показать всеРеферат

C0OS СОВЕТСНИХ

Ю И ЛНЬ

PECflYSJlHH

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И ABTOPCKolVIV СВИДЕТЕЛЬСТВУ

ГОСУД СТВЕННЫЙ НОМИ -ГЕТ СССР

ДМ и (61) 907562 ! (21) 3403786/l8-24 (22) 02.03.82 (46) 07.07.83. Бюл. It 25 .(72) В.Е. Яиный, Ю.И. Литвинович, В.В. Шляхтин и А.Г. Выстропов (71) белорусский ордена Трудового

Красного Знамени государственный . университет им. В.И; Ленина (53) 681. 34681 ° 335(088.8) . (56) 1..Авторское свидетельство СССР

И 907562, кл. 6. 06 J-- 3/00, 6 06 G 7/20, 1980 (прототип)..80„„1027742 А

Удр 6 Об J 3/00; G 06 G 7/20 (54) (57) ЦИФРОАНАЛОГОВЫЙ ФУНКЦИОНАЛЬ.

HbN ПРЕОБРАЗОВАТЕЛЬ СО СТЕПЕННОЙ

ХАРАКТЕРИСТИКОЙ по авт. св. В 907562 отличающийся тем, что, с целью повышения точности функционального преобразования-, в него введен дополнительный блок памяти, подключенный входами к выходам младаих разрядов регистра аргумента, а выхо"дами к дополнительной групее информационных входов младших .разрядов бло-" . ка сдвига..

1 1027

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам преобразования цифрового кода М в аналоговый сигнал Ц&ь1Х по степенной характеристике аида 5 (1) где U - минимальное выходное напря-. о жение;

А - постоянная, зависящая от по" грешности преобразования (А = + б).

По основному авт. св. М 907562 известен цифроаналоговый функциональный преобразователь 1 со степенной характеристикой, содержащий регистр аргу- 15 мента, сумматоры, блок памяти, коммутатор, цифроаналоговый преобразова" тель с линейной характеристикой, управляемый делитель напряжения, выход которого является выходом преобразо- 20 вателя, и блок сдвига, информацион" ные входы младших разрядов которого подключены к выходам блока памяти, соединенного входом с выходами младших регистров аргумента, подключенно- 25 го выходами старших разрядов к первой группе информационных входов коммутатора, вторая группа информационных входов которого соединена с выходами разрядов первого сумматора, причем 50 управляющие входы управляемого делителя напряжения подключены к выходам переносов сумматоров и к управляющим входам коммутатора, а сигнальный вход " к выходу цифроаналогового пре 5 обраэователя с линейной характеристикой, соединенного цифровыми входами с выходами блока сдвига, информационный вход старшего разряда которого подключен к шине логической единицы,1 а управляющие входы - к выходам коммутатора, соединенного третьей группой информационных входов с выходами разрядов второго сумматора, причем сумматоры подключены первыми группами информационных входов к выходам стар45, ших разрядов регистра аргумента, вторыми группами информационных входовк шинам соответствующих опорных кодов, а входами переносов разрядовк шине логической единицы $ 1).

Основным недостатком устройства . является резкое возрастание абсолютной погрешности преобразования при увеличении входного кода. Относитель- 55 ная погрешность при этом не хуже заданной, а абсолютная погрешность может превышать величину кванта примененного линейного цифроаналогового преобразователя. Рассмотрим возрастание абсолютной погрешности. Пусть, например, входной код N = 10, U.

= 64 кванта линейного цифроаналоговоro преобразователя, например, .для

12-ти разрядного линейного преобразователя при ОВ „ „ц1 = 4096 мВ, величина кванта равна мВ, (1+Д )

= 2 /32 = 1,021897. Тогда из таблицы следует, что теоретическое выходное напряжение степенной шкалы должно быть 79,48 мВ. С точностью до одного кванта U sex scop = 79 мВ. С помощью блока памяти на 6 разрядов выходное напряжение преобразователя равно

79 мВ, т.е. ошибки здесь нет. Ошибка появляется при увеличении М « 32, т.е. когда выходное напряжение формируется за счет сдвига в блоке сдвига.

При этом за счет отбрасывания дробной части кванта и умножения сигнала при каждом сдвиге на 2 абсолютная ошибка может существенно превысить квант линейного цифроаналогового преобразователя. При сдвиге на 5 разрядов и округлении на 0,5 кванта максимальная ошибка будет равна 16 квантам, а при округлении до l кванта максимальная ошибка будет равна 32. В таблице приведены значения выходного напряжения устройства и его отличие от теоретического значения по выражению (1) при различных значениях М входного

1 кода, Цель изобретения - повышение точности функционального преобразования.

Указанная цель достигается тем, что в цифроаналоговый функциональный преобразователь со степенной характеристикой, введен дополнительный блок памяти, подключенный входами к выходам младших разрядов регистра аргумента, а выходами к дополнительной группе информационных входов младших разрядов блока сдвига.

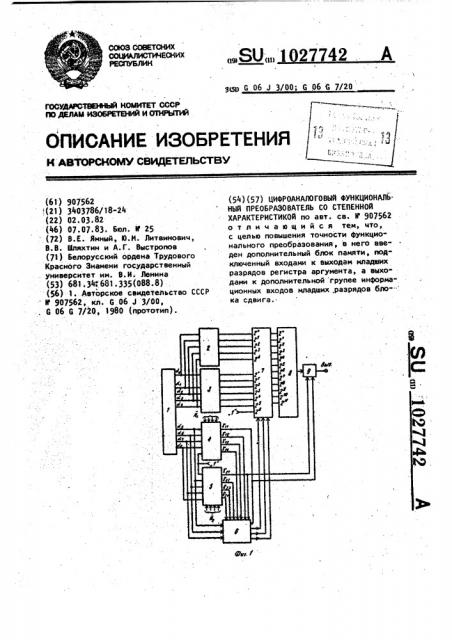

На фиг. 1 изображена блок-схема цифроаналогового функционального преобразователя со степенной характеристикой для случая - 9 разрядного регистра аргумента; на фиг. 2 - возможный вариант реализации блока сдвига.

Цифроаналоговый функциональный преобразователь со степенной характеристикой (фиг. 1) содержит регистр 1 аргумента, дополнительный блок 2 памяти, блок 3 памяти, первый и второй, сумматоры 4 и 5, коммутатор 6, блок 7

3 1027742 4 сдвига, цифроаналоговый преобразова- Количество Разрядов в слова бло, тель 8 с линейной характеристикой, ка 3 памяти должно выбираться из соуправляемый делитель 9 напряжения. . отношения

Блок 7 сдвига подключен информацион- m = (log ° (1/Д), ным.входом старшего разряда к шине: S где < 7 означает ближайшее большее логической единицы, информационными целое число. входами младших разрядов - к выходам . Количество разрядов h слова допол блока 3 памяти, дополнительной груп- нительного блока 2 памяти равно h пой информационных входов младших p (fll + 1))р разрядов к выходам дополнительного 10 где р - число разрядов преобразоваблока 2.памяти. Входы блоков 2 и 3 теля 8. памяти. соединены с выходами младших Количество старших разрядов аргуразрядов регистра 1 аргумента, под.- - мента равно ключенного выходами старших разрядов 8= 8о92й - и . к первой группе информационных вхо= 15 Сигналы с выхода блока 3 памяти дов коммутатора 6. ВтОрая группа ин- поступают на. информационные входы формационных входов коммутатора .б, блока 7 сдвига, а с выхода блока 2 .соединена с выходами разрядов первого памяти - на дополнительную группу сумматора 4, а третья группа инфор- информационных входов блока 7 сдвига, мационных входов коммутатора б под- 20 а на управляющие входы блока 4 сдвиключена к выходам разрядов второго га подаются сигналы r r r с вы0t /э а сумматора 5. Управляемый делитель 9, ходов коммутатора 6, которые опредевыход которого является выходом. пре- ляются следующим образом: образователя, подключен управляющими r и (при и 5 М ) о а. Е. входами к выходам переносов суммато- 2s r = и -й (при и (й с2й е ров 4 и 5 и к.управляющим входам ком- г2 = и -2й (при 2й С и ) е е мутатора 6, а сигнальным входом - к где йе - число, записанное в старших выходу цифроаналогового преобразова- разрядах регистра 1 аргумента, а теля 8 с линейной -характеристикой. й„р - а, т.е. коммутатор б пере"

П реобразователь 8 соединен цифровыми щ дает на выход сигналы либо со старших входами .с выходами блока 7 сдвига, Разрядов регистра 1 аргумента, либо управляющие входы которого подключе- с. выходов соответствующего сумматора. ны к выходам коммутатора 6. Сумма- Количество групп информационных вхоторы 4 и 5 подключены первыми группа- дов коммутаторов равно числу суммами информационных входов к выходам. : торов, а количество разрядов в каж 35 старших разрядов регистра 8 аргумен-. дой группе равно (8og и ), причем к та, вторыми группами информационных коммутатору подключаются младшие развходов " к шинам соответствующих ряды чисел- r, г, г, так как старопорных кодов, а входами переносов вшие разряды этих чисел не изменяются. разрядов - .к.шине логической единицы.. Возможная реализация коммутатора 6 40

Преобразователь работает следующим, может иметь иного вариантов, наприобразом. мер может быть собрана на элементах

Иладшие разряды входного кода ар-, †.И-ИЛИ или на мультиплексорах. умвнта. поступают с регистра 1 аргумента на входы блоков 2 и 3 памяти, на втоРы входы сУмматоРа 4 подает..

При этом на выходе блока 3 появляют- сЯ инвеРсный код исла и, на вторые ся коды, соответствующие степенной входы сумматора 5 подается инверсный шкале преобразователя., а на выходе коД числа й2 2(Р - а), а на вхоДы блока 2 - коды коррекции шкалы пре-. пеРеноса с йРедыдУщего РазРЯда пода" образователя при сдвигах, для умень- ется логическая единица. При этом на шения объема памяти степенная шкала выхоДах Разр"Дов 9 2 9 * Хд Ум"

50 выбирается такой, чтобы выполнялось матора 4 появляются коды, соответстусловие л„ вующие разности кодов числа Ng u (1 + 0") 2, числа й.1, на выходах разрядов, ,, сумматора 5 появляются коды, где d - относительная погрешность M соответствующие разности и -N а е е. преобразователя; на выходах переносов f и " сум+(2Ф и - чйсло младших разрядов аргу- маторов 4 и 5 появляются сигналы, ин" мента. формирующие о том, что коды старших. 1027742

40 разрядов входного - числа превышают й„: или N<.

Если входной код находится в пределах О+2 ", то логические уровни на выходах a(<, с(,а(-1, d g старших разрядов регистра 1 равны нулю, логические уровни на выходах переносов . сумматоров 4 и 5 также равны нулю.

Следовательно коммутатор 6 соединяет соответственно выходы о(,oLg, о(т с управляющими входами блока 7 сдвига °

До этого момента работа функционального цифроаналогового преобразователя не отличается от работы про- 15 тотипа.

Когда входной код превышает 2 но меньше 2 2, то на входе (появляется "1". Эта "1" йроходит через коммутатор 6 и вызывает смещение всех кодов, поступающих на информационные входы блока 7 сдвига, на один разряд вправо, что соответствует умножению кодов на два, при этом напряжение на выходе преобразователя 8 25 также возрастает в два раза. При этом на освобождающийся при сдвиге младший разряд преобразователя 8 блок 7 сдвига подает старший разряд корректирующего кода, поступающего на дополнительную группу информационных входов с дополнительного блока 2 па Ъ мяти. Коэффициент деления делителя 9 должен быть равен номинальному значению К4 . При дальнейшем увеличении 35 входного кода будет увелииваться и выходное напряжение. Соответственно при каждом сдвиге блок 7 подает на освобождающийся младший разряд преобразователя 8 следующий разряд корректирующего кода, снимаемого с выхода блока 2 памяти. Пусть, например, s младших разрядах входного кода записано число 17 (см. таблицу).

После 5-го сдвига мы получим число квантов шкалы 2944, в то время как теоретическое рассчитанное число квантов преобразователя 8 должно составлять 2960. Получаем ошибку в

16 квантов,. которая корректируется подачей на младшие разряды преобразователя 8, освободившихся при сдвигах, корректирующего кода, снимаемого с выхода блока 2 памяти через блок 7 сдвига. В данном случае корректирующий код равен 10000 (см. таблицу).

При превышении М ) М.1 на выходе переноса . сумматора 4 появляется логическая "1", которая изменяет ,коэффициент передачи делителя 9. Он должен стать равным К4 /2 ". При этом коммутатор 6 соответственно подключает выходы разрядов сумматора 4 к управляющим входам блока 7 сдвига.

При дальнейшем увеличении входного кода работа цифроаналогового функционального преобразователя происходит аналогично вышеописанному.

При дальнейшем увеличении входно го кода ивыполнения условия Np) N на выходе переносов сумматора 5 появляется логическая "1", которая изменяет коэффициент передачи делителя

9 до величины К /2 "1. Коммутатор 6 соответственно подключает выходы разрядов сумматора 5 к управляющим входам блока 7 сдвига и далее работа будет происходить аналогично вышеописанному. Конструктивная реализация блока 7 сдвига может быть выполнена по различным схемам. В частности, на фиг. 2 изображена схема блока 7, выполненная на двух группах мультиплексоров 10, в качестве которых могут быть использованы микросхемы I55KIl7

Таким образом, предлагаемый преобразователь по сравнению с прототипом позволяет получить выходное напряжение, изменяющееся по степенному закону в динамическом диапазоне

2 /l +d c абсолютной погрешностью, не превышающей одного кванта используемого в нем цифроаналогового преоб.,разователя с линейной характеристикой.

1027742

ВЫХ-г "bbNn

1-й сдвиг

8bIX i ЭЫХ Р

8ЫХР

Ошибка

Теоретическое значение

Прототип

Ошибка и „.+32

Sblx T

0,48.0,22

0,82

0,67

0,57

0,5I

0,49

Продолжение таблицы

2-Й сдвиг „.+96.ВИХР

Ошибка

Ошибка

74 317,92 316

75 324,88 324

76 332 332

72 339,26 336

78 346,69 344

79 354,28 352

-80 362,04 360

81 369,96 368

3,81

1,75

106 635. 83 632

107 649,75 648

108 664 664

109 678,52 672

110 693,38 688

11 308,56 704

112 724,08 720 113 739,93 736

1,92

0,88

10 79,48 7,9

11 81,22 81

12 83,0 83

13 84 82 84

14 86,67 86

15 88,57 88

16 90,51 90

17 92,49 92 й.+64 и

В 1ХT

3,26

2,68

2,28

2,04

1,96

42

43

44

46

47

48

158.96 158

162,44 162

166 166

169,63 169

173 34 172

177,14 176

181,02 180

184,98 184

0,96

0,44

1,63

1,34

1,14

l,02

0,98. 6,52

5,38

4,56

4,08

3,93

1027742

5»Й сдбиГ й„:+160

0 п

Ошибка

+tx

Ов

О вых

7,7..

01111

00111

3 5

ООООО

11010

10101

10010

10000

10000

Й1 +128

»»»»» 4В

»»»»»

138 1271, 7 1264

139 1299,5 1296

140 1328 1328

141 1357 1344

142 2 386,8 1376

143: 1417,1 1408

144 1448,2 1440

145 1479,,9 1472

13

1у,8

9,1

8,2

7,9

1.71

172

173

174

176

177

2543

2599

2656

2 714

2773

2834

2896

2960

Продолжение таблицы

2528 15

2592 . 7

2656 О

2688 26

2752 21

2816 18

2880 16

2944 16

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Заказ 4771/55

1027742

Тираж 706 Подписное