Цифровой частотно-фазовый дискриминатор

Иллюстрации

Показать всеРеферат

ЦИФРОВОЙ ЧАСТОТНО-ФАЗОВЫЙ ДИСКРИМИНАТОР, содержащий два ft-9триггера и три элемента й-йЕ, о т . л и ч а ю щ и я тем, что, с целью повышения помехоустойчивости дискриминатора при замираниях сигнала , в него дополнительно введены счетчик, регистр, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, формирователь коротких импульсов , три элемента ИЛИ и блок запре та, причем шина опорных сигналов сое.динена с входами установки нуля с 1етчика , счетный входкоторого соединен с щиной счетных ИМПУЛЬСОВ, а выходы с входами К-фазрядного статического регистра, вход записи которого сое:динен с ШИВОЙ входных сигналов, а Vn старших разрядов - с входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, (У«-И)-ЫЙ вход которого соединен с выходом (К+1)-го знакового разряда стати ,ческого регистра, с входом формирователя коротких импульсов и первым Iвходом первого элемента 3 ИЛИ, вто/ ,. ..:, ..рой вход которого соедкнеи с выходом элемента ИСКЛЮЧАЩЕЕ ИЛИ, с первым входом первого элемента 2 И-НЕ и с первым входом второго элемента 3 ИЛИ, второй вход которого соединен о инверсным выходом (k+1)-го знакового разряда статического регистра и первым входсм элемента 2 ИЛИ, причем выход формирователя коротких, импульсов соединен с вторьви входом первого элемента 2 И-НЕ, выход которого соединен с R-входами первого и второго R-5 -триггеров,S -входы которых соединены соответственно с выходами первого и второго элементов 3 ИЛИ, третьи входы которых соединены соответственно с выходами второго и первого R-S-триггеров, причем ин (Л версный выход первого R-S-триггера соединен с первым входом второго элемента 2 И-НЕ, второй вход rfoTopoго соединен с инверсным выходом втоporoR-S-триггера и вторьа ч входом третьего элемента 2 И-НЕ, первый вхо, которого соединен с выходом элемента 2 ИЛИ, второй вход которого соединен с выходом второго элемент 2 И-НЕ и управляющим входом блока запрета, инфо1 1ационные входа которого. сйеди : нены с К разрядами статического регистра ,. причем выходы блока запрета и второго элемента 2 И-НЕ соедине - ны с соответствукяцимн выходными информационными шинами, а выход третьего элемента 2 И-НЕ соединен с выходной шиной знакового разряда.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

МБО Н 03 0 13 00

Ф

ОПИСАНИЕ ИЗОБРЕТЕНИ

К ABT0PCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ, ИЗОБРЕТЕНИЙ И ОТНРИТИЙ (21) 3397570/18-21 (22) 08.02.82 (46) 07.07.83. Бюл. 9 .25 (72) В.Г. Аристов, Б.r. Иванов и С.В. Матвеев (53) 621 ° 398(088 ° 8),(56 ) 1. Авторское свидетельство СССР

Р 546087;" кл. Н 03 О 13/00, 1975.

2. Авторское свидетельство .СССР 9 .484621. кл..Н 03 0 13/00, 1974. (S4)(57) QH4P0BOA ЧАС О НО-ФАЗОВ и

ДискРииинАтОР, содержащий даaQ;""Sтриггера и три элемента И-НЕ, о тл и ч а ю шийся тем, что, с целью повышения помехоустойчивости. дискриминатора при замираниях сигнала, в него дополнительно введены счетчик, регистр, элемент ИСКЛЮЧАЮЩЕЕ

ИЛИ,,формирователь коротких импуль-сов, три элемента ИЛИ и блок запрета, причем шина опорных сигналов соединена с входами установки нуля счетчика, счетный вход.-которого соединен. е шиной счетных.импульсов, а выходыс входами K-разрядного статического регистра,. вход записй которого соединен с шиной входных сигналов, а

М старших разрядов — с входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, (И+1)-ый . вход которого соединен с выходом (1+1)-ro знакового разряда статического регистра, с входом формиро-. вателя коротких импульсов и первым

1входом первого элемента 3 ИЛИ, второй вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с первым входом первого элемента 2 И-ИЕ и с первым входом второго элемента 3

ИЛИ, второй вход которого соединен с инверсным выходом (К+1)-гс знаково:го разряда статического регистра и первым входом элемента 2 ИЛИ; .причем выход формирователя коротких, имп соединен с вторым входом первого элемента 2 И-НЕ, выход .которого соединен с R-входами первого и второго К-S -- триггеров,,S --входы которых соединены соответственно с выходамн первого и второго элементов 3

ИЛИ, третьи входы которых соединены соответственно с выходами второго Я и первого k-S-триггеров, причем инверсный выход первого Q.--,S-триггера соединен с первым входом второго элемента 2 И-НЕ, второй вход которого соединен с инверсным выходом втоporok-S-триггера и вторым входом и третьего элемента 2 И-НЕ, первый вхо которого соединен с- выходом элемента

2 ИЛИ, второй вход которого соединен. .с выходом второго элемента 2 И-HE и управляющим входом блока запрета, .информационные входы которого. соеди-... нены с К разрядами статического ре гистра, причем выходы блока запрета и второго элемента 2 И-HE соедине ны с соответствующими выходными информационными шинами, а выход третьего элемента 2 И-НЕ соединен с вы:ходной шиной знакового разряда.

1027798

Изобретение относится к радиотехнике, в частности к радиоавтоматике и импульсной технике, и может быть использовано в цифровых системах фазовой автоподстройки частоты.

Известен частотно-фазовый дискри- 5 мииатор, содержащий два формирователя связанные соответственно с тремя триггерами, чемырьмя элементами И и днумя элементами И-НЕ (1 ).

Недостатком данного дискриминато- )Q ра являются сбои при пропадании входного сигнала.

Известен также частотно-фазовый дискриминатор, содержащий связанные между собой три триггера и пять элементов И-HE в котором при сближении частот выполняется автоматический переход из режима сравнения частот в режим сравнения фаз 2).

Недостатком известного дискриминатора является низкая помехоустойчивость, так как при периодическом пропадании сигнала на входе дискриминатора, вызванного, например, глубокими амплитудными флюктуациями,. происходят нежелательные переходы 25 из режима сравнения фаз в режим сравнения частот.

Цель изобретения — повышение помехоустойчивости дискриминатора при замираниях сигнала. 30

Поставленная цель достигается тем, что н дискриминатор, содержащий два R-Á -триггера и три элемента

И-НЕ, дополнительно введены счетчик, регистр, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, З5 формирователь коротких импульсов, три элемента ИЛИ и блок запрета, причем шина опорных сигналов соединена с входами установки нуля счетчика, счетный вход которого соединен с шиной счетных импульсов, а выходы с входами )< -разрядного статического регистра, вход записи которого соединен с шиной входных сигналов, а уП старших разрядон — с входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, (Ю+1)-ый вход которого соединен с выходом (К+1)-ro знакового разряда статического регистра, с входом формирователя коротких импульсов и первым входом первого элемента 3 ИЛИ, второй вход gQ которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с первым входом первого элемента 2 И-НЕ и с первым входом второго элемента 3 ИЛИ, второй вход которого соединен с инверсным 55 выходом (К+1)-го знакового разряда статического регистра и первым входом элемента 2 ИЛИ, причем выход формирователя коротких импульсов соединен с вторым входом первого эле мента 2 И-НЕ, выход которого соединен с R,-входами первого и второго

P.-g-триггеров, Q -входы которых соеди- . нены соответственно с ныходами первого и второго элементов 3 ИЛИ, тре тьи входы которых соединены соответ- 65 ственно с выходами второго и первого P -S -триггеров, причем инверсный выход первого Й- S --триггера соединен с первым входом второго элемента 2

И-НЕ, второй вход которого соединен с инверсным выходом второго Q,-5 -триггера и вторым входом третьего элемента 2 И-HE первый вход которого соединен с выходом элемента 2 ИЛИ, второй вход которого соединен с вы- ходом второго элемента 2 И-НЕ и управляющим входом блока запрета, информационные входы которого соединены с К разрядами статического регистра, причем выходы блока запрета и второго элемента 2 И-НЕ соединены с соответствующими выходными информационными шинами, а выход третьего элемента 2 И-HE соединен с выходной шиной зиакового разряда.

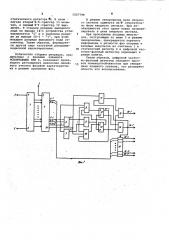

На фиг. 1 приведена схема предлагаемого устройства; на фиг. 2 и 3 временные диаграммы дискриминатора.

Цифровой частотно-фазовый дискриминатор содержит счетчик 1, шину

2 счетных импульсов, шину 3 опорных сигналон, статический регистр 4, выход 4-1 первого разряда статического регистра, выход 4-2 второго разряда статического регистра, выход 4-i

i-ro разряда статического регистра, выход 4-К К-го разряда статического регистра, выход 4-(К+1) знакового . разряда статического регистра, шину 5 входных сигналов, элемент

ИСКЛЮЧАЮЩЕЕ ИЛИ 6, .выход 6-1 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, формирователь 7 коротких импульсов, выход 7-1 формирователя коротких импульсон, первый элемент 3 ИЛИ 8, первый элемент 2 ИНЕ 9, второй 10 элемент 3 ИЛИ, элемент 2 ИЛИ 11, первый R- В -триггер.

12, выход 12-1 первого P.-g-триггера, второй R - -5 триггер 13, выход 13-1 второго К-5 триггера, второй элемент

14 2 И-НЕ, выход 14-1 второго эле,мента 2 И-НЕ,(выходная шина старшего разряда), третий элемент 2 И-НЕ

15, выход 15-1 третьего элемента 2

И-НЕ {выходная шина знакового разряда), блок 16 запрета, выходную шину

16-1 первого разряда, выходную ши-ну 16-2 второго разряда, выходную шину 16-i i-го разряда, выходную шину 16-К К-го разряда.

Счетный вход Т и вход R установки нуля счетчика 1 соединены с шинами 2 и 3 источников счетных и опорных импульсов соответственно, а выходы счетчика 1 соединены с входами статического регистра 4, вход записи информации С которого соединен с шиной 5 входных импульсов причем старших разрядов (4-i, .., 4- K) Kразрядного кода статического регистра 4 соединены с М входами элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ 6, (в+1)-й нход которого соединен с выходом 4 (К+1) знакового разряда статического регист10 27798

3 ра 4, с входом формирователя 7 коротких импульсов и первым входом ,первого элемента 3 ИЛИ 8, второй вход которого соединен с выходом 6-1 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с первым входом первого элемента 9 2 И-НЕ, 5 с первым входом второго элемента

3 ИЛИ 10, второй вход которого соединен с инверсным выходом знакового разряда статического регистра 4 и первым входом элемента 11 2 ИЛИ, 10 причем выход 7-1 формирователя 7 коротких импульсов соединен с вторым входом первого элемента 2 И-НЕ 9, вы-. ход которого соединен с R входами первого и второго К-с -триггеров 12 и 13, S -входы которых соединены соотверственно с выходами первого и второго элементов 3 ИЛИ 8 и 10, третьи входы которых соединены соот". ветственно с выходом 13-.1 второго и выходом 12-1 первого R-S-триггеров

13 и 12, причем инверсный выход первого -S -триггера 12 соединен с первым входом второго элемента 2 И-НЕ

14, второй вход которого соединен с инверсным выходом второго К-9-триггера 13 и вторым. входом третьего элемента 2 И-HE 15, первый вход которого соединен с выходом элемента

2 ИЛИ 11, второй вход которого соединен с выходом 14-1 второго элемен- 30 та 2 .И-НЕ 14, и управляющим входом блока 16 запрета, информационные входы которого соединены с К разрядами 4-1, 4-2,...,4-1,...,4-К статического регистра 4,-причем выходы З5

16-1, 16-2,...,16-К блока 16 запрета и выход 14-1 второго элемента 2 И-НЕ

14 соединены соответственно с выходными информационными шинами, а выход 15-1 третьего элемента 2 и-НЕ 15.40 соединен с выходной шиной знакового разряда. устройство работает следующим образом.

Опорные сигналы поступают с входа 3 устройства на вход R счетчика 1 45 устанавливая на выходе последнего ну" ли. На вход Т счетчика 1 по входной шине 2 поступают счетные импульсы.

При Этом частота счетных импульсов определяется выражением 50 у 2(1"-1) сч= т где (2 -1) — емкость счетчика, К

Т вЂ” период опорного сигнала. 55

В момент прихода по входной шине

5 импульса на вход С информация из счетчика"1 записывается в статический регистр 4.

Если частота входных импульсов, поступающих по входной шине 5, больше частоты опорных импульсов, поступающих по входной шине 3 (f8<) од ), то разность фаз этих сигналов убыва.ет от цикла к циклу (фиг.2 а) и дос- тигнет нижнего порога в момент времени t .„ когда количество счетных импульсов записанных в статический регистр 4 будет удовлетворять неравенству N С 2"- Х 2"- (на фиг. 2 рас» смотрен случай для m=.2). В этом случае в а старших и (4+1)-ом знаковом разряде 4 (К+1) статического регистра 4 будут нули.

Нуль появится на выходе 6-1 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ б и через открытый первый элемент 3 ИЛИ 8, на входе первого К- S триггера 12.

Первый R-Ü -триггер 12 установится в 1.и закроет второй элемент 3. ИЛИ

10, исключив включение второго R-5триггера 13 до сброса первого К-5— триггера 12. На выходе элемента

2 ИЛИ 11, установится "1", а на выходе 15-1 третьего элемента 2 И-НЕ

15, т.е. в знаковом разряде выходного кода устройства - "0", на выходе

14-1 второго элемента 2 И-НЕ 14, т.е.. в старшем разряде выходного кода цифрового частотно-фазового детектора установится единица, которая отключит младшие разряды выходного кода, поступающего через блок 16 запрета.

Сброс К-.5 -триггеров 12 и 13 произойдет при переключении знакового разряда статического регистра 4 на линейном участке характеристики дискриминатора (момент времени t< ) когда в статическом регистре 4 знаковый разряд 4 (К+1) переключается с "1" на "0" и в ь| старших Разрядов

4-i,...,4-К появилась хотя бы одна единица, или с "0" на "1" и в в старших разрядах появился хотя бы один нуль. В этих случаях короткие импульсы с выхода 7-1 формирователя

7 пройдут через открытый первый элемент 2 И-НЕ 9, и установят триггеры

12 и 13 в состояние "0" (выключено), при этом в старшем разряде выходного кода на выходе 14-1 появится нуль, который разрешает прохождения младших разрядов выходного кода статического регистра 4 на выходы 16-1, 16-2,...,.16-i 16-К, блок 16 запрета. Если разность частот опорных и . входных. импульсов не равна нулю, то процесс повторится. Таким образом, формируется одна полярность частотной дискриминационной характеристики.

Если эта разность равна нулю, то устройство работает в режиме сравнения фаз и устанавливается режим синхронизма..

Если частота входных импульсов, поступающих по шине 5 меньше частоты опорных импульсов, поступающих по шине 3 (fg< с 10„ ), то разность.фаз; этих сигналов возрастает от цикла к циклу (фиг. 2б). Верхний порог удов-. летворяет неравенству йъ 2к+,. 2 "

К-1 что соответствует появлению едйниц в старших и (K+1)-ом знаковом разряде

1027798

5 статического регистра %, В этом случае второй К-6-триггер 13 включен, а первый 9-3 -триггер 12 выключен, В старшем разряде выходногокода на выходе 14-1 устройства устанавливается "1" и в знаковом разряде:на выходе 15-1 — "1", при этом .младшие разряды выходного кода отключены. Таким образом, формируется.другой знак частотной дискриминационной характеристики.

Количество старших разрядов, соединенных с входами элемента

ИСКЛЮЧАКНЦЕЕ ИЛИ б, позволяет производить регулировку диапазона линейного участка фазовой характеристики в режиме сравнения фаз.

В режиме синхронизма фаза опорного сигнала сдвинута на ft относительно фазы входного сигнала; При необходимости этот сдвиг можно скомпенсировать в цепи опорного сигнала.

5 При пропадании входных импульсов, поступаюших по шине 5 в режиме синхрониэма, прекрашается перепись информации о разности фаз опорных и входных импульсов иэ счетчика 1 в статический регистр 4 и цифровой частотно-фазовый детектор переходит в режим памяти.

Таким образом, цифровой частот-, но-фазовый детектор, обладает высокой помехоустойчивостью при замираниях входного сигнала, что расширяет область его использования.,1027798

1027798

Составитель М. Катанова

Техред М. Костик Корректора. Тяско

Редактор Н. Ковалева

Филиал ППП "Патент", r.Óæãoðoä, ул. Проектная, 4

Заказ 4753/57 Тираж 936 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5