Д-триггер

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

agl nl>

gag Н 03 K 31286

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

° Ф

° а

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ.(21) 3405771/18-21 (22) 05.03.82 (46) 07.07.83. Бюл. 11 2g (72) В.Г.Аврамов и Ю.П.Иванов

:.(71) Иосковский ордена Трудового

Красного Знамени инженерно-физический институт (53) 621.374(088.8) (56) l. Каталог 0igiTAC Lutegrated

Сi.rcuit О.А.Т.А.Book.1976, Edition

23 р.302, fig 8.02-214 °

2. Я. Будинский. Логические цепи в цифровой технике. И., "Связь!, 1977, с.374, рис.7.90 (прототип). (54)(57) О-ТРИГГЕР,, содержащий транзисторы и резисторы, первую и вторую шины питания, источник опорных напряжений (ИОН), шину логического входа, .шину входа синхронизации, шины первого и второго выходов, причем .коллекторы второго и седьмого транзисторов объединены с. базой четвертого транзистора и через второй резистор соединены с второй шиной питания, коллектор четвертого транзистора соединен с второй шиной питания, а эмиттер с шиной первого, выхода и через четвертый резистор с первой шиной питания, эмиттер .третьего транзистора со-: . единен с эииттером второго, база соединена с первым выводом источника опорных напряжений, а коллектор соединен с базами пятого и шестого транзисторов и через третий резистор, с второй шиной питания, коллекторы шестого и пятого транзисторов соединены с второй шиной питания, а эмиттер последнего - с шиной второго выхода и через пятый резистор с первой шиной питания, база первого транзистора соединена с вторым выводом источника опорных напряжений, а эмиттер через первый резистор - с перво" шиной питания, отличающийся тем, что, с целью снижения напряжения питания, уменьшения потребляемой мощности,и упрощения схемы, в него вве" дены диод, шина парафазного входа синхронизации с восьмого по одиннадцатый транзисторы типа р-п-р, кол- р лекторы которых соединены с первой шиной питания, а эмиттеры попарно объединены с базой второго транзистора и через седьмой резистор соедине- С ны с второй шиной питания и с базой седьмого транзистора и через восьмой резиатор соединены с второй шиной питания соответственно, базы с восьмого по одиннадцатый транзистор соединены соответственно с шиной входа синхронизации, виной логического вхо" да, с катодом диода, анод которого со соединен с эмиттером шестого транзистора и с шиной парафазного входа синхронизации, коллектор первого тран" зистора соединен с эмиттерами второго, третьего и седьмого транзисторов, катод диода через резистор .соединен с первой шиной питания.

1, 10278

Изобретение относится к вычисли- .

; тельной технике и микроэлектронике и предназначено для использования в быстродействующих цифровых микросхе-. мах, в частности, для использующих логику на эмиттерных повторителях (ЗПЛ), Известны схемы триггеров, состоящие из бистабилвной ячейки и двух разностных преобразователей, управ- 1р ляющих ее работой 5 13

Недостатками данных схем являются сложность реализации в микросхемах на дПЛ и переключателях тока и сравнительно невысокое быстродействие, Наиболее близким к предлагаемому является О-триггер, использующий двухярусный переключатель тока 2 .

Недостатками известного триггера являются сравнительно большая потреб- о ляемая мощность, относительно высокое напряжение питания, значительное число компонентов. схемы.

Цель изобретения - уменьшение готребляемой мощности, снижение напряжения питания и упрощение схемы, Поставленная цель достигается тем, что в О-триггер, содержащий тран" зисторы и резисторы,. первую и вторую шины питания, источник опорных напряжений, шину логического входа, шину входа синхронизации, шины первого и второго выходов, причем коллекторы второго и седьмого транзисторов объединены с базой четвертого транзистора и через второй резистор соединены с второй шиной питания, коллектор чет. вертого транзистора соединен с второй шиной питания, а эмиттер — с шиной первого выхода и через четвертый ре- зистор с первой шиной питания,. эмит" тер третьего транзистора соединен с змиттером второго, база соединена с первым выводом источника опорных напряжений, а коллектор соединен с базами пятого и шестого транзистора и через третий резистор с второй шиной питания, коллекторы шестого и пятого транзисторов соединены с второй шиной питания, а эмиттер последнего " с шиной второго выхода и через пятый резистор с первой шиной питания, база. первого транзистора соединена с вторым выводом истОчника опорных напряжений, а эмиттер через первый„ резистор ". с первой шиной питания, введены диод, шина парафазного, входа синхронизации с восММого по одиннадцатый транзисторы типа р-п-р, 02 2 коллекторы которых соединены с первой шиной питания, а змиттеры попарно объединены с базой второго транзистора и через седьмой резистор соединены с второй шиной питания и с базой седьмого транзистора и через восьмой резистор соединены с второй шиной питания соответственно, базы с восьмого по одиннадцатый транзистор соединены соответственно с шиной входа синхронизации, шиной логического входа, с катодом диода, анод которого соединен с эмиттером шестого транзистора и с шиной парафаэного входа синхронизации, коллектор первого транзистора соединен с эмиттерами второго, третьего и седьмого транзисторов, катод диода через резистор соединен с первой шиной питания.

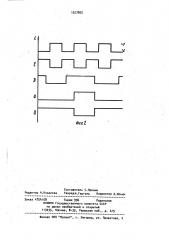

На фиг. 1 изображена принципиальная схема Р-триггера; на фиг.2 - временные диаграммы работы 0-триггера.

0"триггер содердит транзисторы с

1-7 и-р-и типа, транзистор 8 типа р"п-р, резисторы 9-14, шину 0 15 логического входа, шину 16 входа синхронизации, шины Q u Q выходов соот" ветственно 17 и 18, выводы 19 и 20

Е и Й„ источника опорных напряжений, диод 21, первую и вторую шины 22 .и

23 питания, резисторы 24 и 25, транзисторы 29-28 типа р-п-р, шину парафазного входа 29 синхронизации (С) .

D-триггер работает следующим образом.

Обозначим в соответствии с временными диаграммами (фиг,2) высокий выходной потенциал U = -Ub- через "!", а низкий выходной потенциал V =

/ I.

= Ч -!R V - Ч через "0", где 1 ток источника тока, собранного на транзисторе l и резисторе 9; R сопротивление резисторов 10 или 11;

Vg> - падение напряжения на переходе база-змиттер транзисторов 4-6, 8, 26-28. Как известно в 3ПЛ происходит изменение уровней напряжения на величину !/yg. Положим, что входные сигналы (C, С, О) смещены вниз на Ч&9 по сравнению с выходными (Q, Q). При согласовании входных и выходных уровней достаточно в цепи выходных эмиттерных повторителей, собранных на транзисторах 4 и и резисторах 12 и 13 в эмиттерную цепь включить диоды

Пусть триггер находится в состоя нии 0 0, Q =-. 1. Если С О, то потенциал базы транзистора 2 будет

3 1.0278 меньше потенциала базы транзистора

3 (Е ) при любом значении 0 потенциал базы транзистора 7 также меньше Е поскольку пары транзисторов 8 и 26, 27 и 28 реализуют логическую функцию И. Таким образом, источник тока будет протекать через. транзистор 3 и вызывать падение напряжения на резисторе 11 ьЧ -IR, которое передается на выход 17 Q и базу 27 транзистора. Триггер сохраняет свое состояние.

Если С = 1, то. при Р = 0 потенциал базы транзистора 2 меньше Е.1 и триг-. гер также сохраняет свое состояние, согласнб проведейному выше анализу.

Если С = 1, 0 = 1, то на эмиттерах транзисторов 8 и 26 формируется высокий .потенциал, который передается на базу транзистора 2 и ток в ключе переключателя тока начинает протекать через резистор 10, образуя падение напряжения на нем 60 = -.18 которое передается на выход 18. Выход 18 пе-. реключается из состояния "1" в состояние "0". Выход 17, соответствен- . .но, переключается из 0 в i При из" менении С из "1" в "0" потенциал базы транзистора 2 понижается из высокого в нйзкий, а потенциал базы транзис30 тора 7 повышается из низкого в высокий.

Потенциал базы транзистора 7 становится выше Е, ток 1 начинает протекать через транзистор 7. Состояние

02 ф выходов не изменяется, т.е. триггер хранит информацию.

Таким образом, предлагаемый триг" . гер-реализует фунцию О-триггера, как и прототип, выражающуюся уравнением:

Q = ОС + СО., где Q" и О " обозначают состояние выхода 17 триггера до и после поступления синхросигнала (изменение С из состояния "0" в состояние "1"), Реализовать предлагаемую схему позволяет технология "Изопланар", на основе которой реализуются как и-р-и транзисторы, так и р-и-р транзисторы с общим коллектором, выполненным на основе подложки.

В предлагаемом триггере используют одноярусный переключатель тока, а не двухъярусный, что позволяет. использовать меньшее напряжение питания и понизить потребляемую мощность. Kpgме того, одноярусный переключатель тока имеет меньшую задержку переключения t> по сравнению с двухъярусным.

Одноярусный переключатель 30 тока требует лишь одно опорное напряжение (E< 3, что упрощает трассйровку и конструкцию ИОН и приводит к экономии мощнооти ИОН по сравнению с двухъярус ным переключателем тока, Напряжение питания может быть уменьшено с 5,24,5 В до 3,0 В, что обеспечивает уменьшение йотребляемой мощности на

30-404.

1027802

Составитель С.Пронин

Редактор Н.Ковалева ТехредИ,гергель Корректор А.Ильин

Заказ 4754/58 Тираж 936 Подписное

ВНИИПИ Государственного комитета СССР

ho делам изобретений и открытий

113035, Ий:ква, Ж-35, Раушская наб., д. 4/5

8 ФЭ ЮЮ ВЮЮЮЮФ ЮЮЮЮ

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4