Формирователь сигнала выборки шины матрицы накопителя

Иллюстрации

Показать всеРеферат

ФОРМИРОВАТЕЛЬ СИГНАЛА ВЫБОРКИ ШИНЫ МАТРИЦЫ НАКОПИТЕЛЯ , содержащий И транзисторов, коплек торы и базы .которых объединены, а эмит тары подключены к соответствующим входным шинам формирователя, выходной транзистор, KomieKTO которого соединен с шиной источника питания, а эмиттер подключен к выходной шине формирова- . тепя, ава резистора, первые выводы которых объединены, второй вьшод первого резистора соединен с базой выходного транзистора, второй вывод второго резистора соединен с шиной источника питания , отличающийся тем, что, с целью у величения быстродействия, в него введены два транзистора, два диода и источник тока, причем коллектор первого введенного транзистора соед1щен с шиной источника питания, база соединена с первыми выводами резисторов, а эмиттер - с базой второго введенного транзистора и анодом первого дисца, коллектор второго введенного транзистора соедио нен с базой выходного транзистора, а эмит (Л тер - с коллекторами и транзисторов, катод первого диода соединен с базами И тран-аисторов и анодом второго диода, катод .которого соединен с источником тока.

СОО3 СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

3(5g Н 03 К 19/08

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИ

Н ABTOPCHOlVIY СВИДЕТЕЛЬСТВУ

1- ю,(21) ЗЗЦ1161/18 21 (22) 02.12.81 (46) 07.07.83. Бюл. 1 а 25 (72) В. В. Пастон, И. Л. Дробышева и Jt. П. Холоднова (53) 621.375,083(088,8) (56) 1. Патент Англии М 1489861, jxa. Н 03 К 13/25, 1977.

2. Uftra High speed .1К-Bit Ram .Urth 75 nS Access:. Time iSSCC 77 !

wednesday, February 1á, 1977, paqe 78-79 (прототип). (54) (57) ФОРМИРОВАТЕЛЬ СИГНАЛА ВЫБОРКИ ШИНЫ МАТРИЦЫ НАКОПИТВ»

ЛЯ, содержаший И транзисторов, коллекторы и базы которых объединены, а эмиъ

:теры поцключены к соответствующим входным шинам формирователя, выходной транзистор, коллектор которого соединен с шиной источйика питания, а эмиттер

-подключен к выходной шине формирова-, теля, цва резистора, первые вывоцы которых обьецинены, второй вывод первого резистора соединен с базой выхоцного транзистора, второй вывоц второго резис тора соединен с шиной источника питания, о т л и ч а ю ш и и с я тем, что, с целью увеличения быстроцействия, в него введены цва транзистора, qaa диоца и источник тока, причем коллектор первого введенного транзистора соецинен с шиной источника питания, база соецинена с первыми выводами резисторов, а эмич тер - с базой второго введенного тран- зистора и анодом первого диода, коллектор второго ввеценного транзистора соеци 42 нен с базой выхоцного транзистора, а эми

Щ тер с коллекторами Vl транзисторов, катод первого диода соецинен с базами g тран-.

-зисторов и аноцом второго циоца, катоц % ,которого соединен с источником тока.

1027824.Изобретение относится к вычислитель- ной технике и предназначено пля использо вания в качестве одного иэ элементов управления матрицей памяти интеграль ного запоминаюшего устройства.

Известен И вхоповой ЭСЛ дешифратор для выбора одной из 2" комбинаций, который состоит иэ И инверторов, каждый из которьж содержит в себе два эмит терно связанных транзистора и источник 10 тока, подсоединенный к связанным эмич терам. Дополнительные парафазные выход» ные сигналы получаются соответственно на коллекторах-ааух транзисторов. Дешиф» ратор соперкит также 2 -, VI входных пио 15 да, объединенных в Я -вентили, каждый из которъпс имеет выходной эмиттерный повторитель, на котором формируется сш нал выборки или невыборки строки или столбца матрицы накопителя $1) . щ

Недостатком данного пеши ратора являются высокие логические перепады в

его узлах и как следствие недостаточно высокое быстродействие.

Известен формирователь сигнала выборки шины матрицы накопителя; состояший иэ И транзисторов, объединенных в

И -вентили, базы которых обьепинены и попсопеинены к двум резисторам: первому и второму. Второй вывод первого ре энстора подсоединен к источнику питания, второй вывод второго резистора подсое динен к выводу, к которому подключены объединенные коллекторы 8 транзисторов, а также вывод базы транзистора формирователя, эмиттер которого попключен к шине -накопителя, а коллектор подключен к шине источника питания, Эмиттеры ртранэисторов имеют выводы, которые подключены к шинам дешифратора ) 2).

Недостатком укаэанного формирователя, связанным с его быстродействием, являеъм то, что один иэ резисторов включен параллельно перехопам б к 8 транэисто ров, вследствие чего изва возмож45 ности насьпцения транзисторов большую часть логического перепада, который определяет быстродействие, необходимо формировать на резисторе, соединенном с шиной источника питаниа, что увеличива- 5О ет перепад на базе И транзисторов и со ответственно перепал на эмиттерах этих транзисторов. Снижение быстропействия происходит также из-еа наличия большой емкости в коллекторном узле N транэис» торов, подсоединенной непосредственно к базе формирователя и как следствие большой постоянной времени в этом узле, в котором создается основной логический пе репап.

Бель изобретения - повышение быстро действия, Указанная цель достигается тем, что в формирователь, содержаший 0 транзисторы, коллекторы и базы которых объе динены, а эмиттеры подключены K соот» ветствуюшим входным шинам формирова теля, выходной транзистор, коллектор которого соединен с шиной источника пита ния, а эмиттер подключен к выходной шине формирователя, два резистора, пер вые выводы которых объединены, второй вывод первого резистора соединен с базой выходного транзистора, второй вывод второго резистора соединен с шиной источ ника питания, введены два транзистора,. два диода и источник тока, причем кол лектор первого введенного транзистора соединен с шиной источника питания, база соединена с первыми выводами реэисто» ров 8 sMHTTep c базой BTopoI o BBeg88» ного транзистора и анодом первого диода, коллектор второго введенного транзистора соединен с базой выходного транзистора, а эмиттер с коллекторами И транэисто ров, катод первого диона соединен с ба эами И транзисторов и анодом второго, диода, катод которого соединен с источ HHKOM тока.

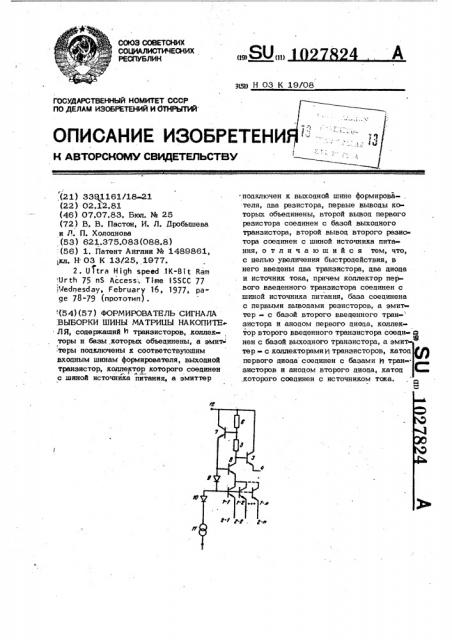

На чертеже представлена принципиаль наа электрическая схема предлагаемого формирователя.

Формирователь содеркит И транэисто ров 1-1 - 1-И, эмиттеры которых под» ключены к входным шинам фррмирователя 2-1 - 2-и, выходной транзистор 3, эмиттер которого подключен х выходной шине 4 формирователя, первый 5 и вто рой 6 резисторы, дополнительно введенные первый 7 и второй 8 транзисторы,первый 9 и второй 10 диоды, источник 11 тока, коллекторы выходного транзистора 3 и транзистора 7, при этом вывод резис тора 6 соединен с шиной источника 12 питания.

В дешифраторе строк и столбцов мат . рицы накопителя входные шины формирователей подключаются к одному иэ коллекторов соответствующих эмиттерно связан ных попарно транзисторов, образуюшкх для каждого разряда входа парафазные сигналы. Выходные шины формирователей подключа ются к соответствуюшим шинам матрицы накопителя. При этом пля всех формирователей используется обший датчик тока, E которому под3 1027824 ° 4

«лючаются катоцы циодов 10 формирова- ля. В остальных формирователях хотя бы талей. oaHH tLt N транзисторов oKttsh3BBBTctt .IlpH

Формирователь работает следующим этом OTttpbtThlM и на выходных шинах образом. формирователей будет низкий потенциал.

Пусть на входы цешифратора поцаеъ» > Независимо от числа открытых р транся такая комбинация логических сигна зисторов в формирователе ток в цеци ре лов, что во входных шинах цреалагае зистора 5 будет незначительно изменять мого формирователя так отсутствует, ся за счет наличия цепи через транзио все И транзисторы закрыты, транэио- тор 7 отрицательной обратной связи. тор 8 закрыт. При этом выходной трап tp Использование изобретения позволит эистор отк ыт, т.е. выбрана соотнес улучшить показатели ЗУ (по времени ствукшая шина матрицы накопителя. Ноа выборки aapectt) и увеличить технологи ключеиная к выходной шине формировате» ческие запасы цо этому параметру.

Составитель И. Дягель

Редактор Ю. Ковач Техред А.Ач Корректор Г. Огар

Заказ 4755/59 Тираж 936 Подписное

ВНИИПИ Госуцарственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж35, Раушская наб., ц. 4/5

Филиал ППП "Патент, г. Ужгород, ул. Проектная, 4