Делитель частоты на три

Иллюстрации

Показать всеРеферат

ДЕЛИТЕЛЬ ЧАСТОТЫ НА ТРИ по авт. св. № 784004, о т л и ч а ю ш U и с я тем, что, с целью расширения функционалышх возможностей, в него введены элемент И и в кажоый разряд элемент НЕ в цополшстельный элемент И-НЕ, выход которого соедт1енс входом элемента НЕ, а Первый вход с прямым выходом триггера этого же разряда, второй вход дополнительноххэ элемента И-НЕ второго и третьего разряда - с инверсным выходом триггера предыдущего разряда, а второй вход дополнительного элемента И-НЕ первого разряда соединен с инверсным выходом триггера третьего разряда, прямой выхрд которого соединен с первым входом элемента И,; второй вход которого под клгочен к прямому выхощ триггера второго разряда.

СОЮЗ СОВЕТСКИХ

ИЦЙ

РЕСПУБЛИН

09) (И) А

Зцо Н 03 К 23/02

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ " н авторскому свиддткльствм

/ (61) 784004 (21) 3407263/18--21 (22) 17. 03.82

{46) 07.07.83. Бюл. Ж 25

{72) Н. В. Угланов (53) 621,374.44 (088.8) (56) 1. Авторское свицетельство СССР

М 784004, кл. Н 03 К 23/02, 1979. (54) (57) ДЕЛИТЕЛЬ ЧАСТСУГЫ НА

ТРИ по авт. св. Ж 784004, о т л ич а ю шийся тем, что, с мелью расширения функциональных возможностей, в него введены элемент И и s каждый разряд элемент НЕ и дополнительный элемент И-НЕ, выход которого соединен. с входом элемента НЕ, а первый входс прямым выходом триггера этого же разряда, второй вход дополнительного элемента И HE второго и третьего разряда - с инверсным выхоцом триггера предыдущего разряда, а второй вход дополнительного элемента И-HE первого разряда соединен с инверсным выходом триггера третьего разряда, прямой выход которого соединен с первым входом элемента И,. второй вход которого под;ключен к прямому выходу триггера второго разряда.

1 10278

Изобретение относится к импульсной технике и может быть использовано при построении генераторов тактового питания приборов с зарядовой связью, трехфазных распределителей. 5

По основному авт. св. N 784004 известно устройство, содержащее в кал » дом разряде триггер, прямой выход кото-, рого подключен к первому входу элемента И-НЕ, а также инвертор, вход кото- 10 г

РОГО подключеН К ВХОДНОЙ ШИНЕ, ВХОДЫ синхронизации триггеров подключены к входной шине, вторые входы элементов

И- Е подсоединены к выходу инвертора, а выход каждого элемента,И-НЕ соеди- 15 нен с инверсным входом триггера предыдущего разряда Р 1) .

Недостатком известного устройства являются ограниченные функпиональные возможности, так как длительность пере- ц крытия выходных импульсов делителя на двух выходах делителя равна сумме длительности входного тактового импульса плюс задержка переключения тригге ра по установочному входу, что исключает25 применение этого устройства.

Бель изобретения - расширение функпиональных воэможностей.

Указанная пель достигается тем; что в делитель частоты на три, содержащий в каждом разряде триггер, прямой выход которого подключен к первому входу элемента И-НЕ, а также инвертор, вход которого подключен к входной шине, входи синхронизаяии триггеров подключены к 35 входной шине, вторые входы элементов

И" HE подключены к выходу инвертора, а выход каждого элемента И-HE соединен с инверсным входом триггера предыдущего разряда, введены элемент И и в 40 каждый разряд элемент HE и дополнительный элемент И НЕ, выход которого соединен с входом элемента НЕ, первый вход — с прямым выходом триггера этогО же раэряда втОрой вход допОлнитель 45 ного элемента И HE второго и третьего разряда - с инверсным выходом триггера предыдущего разряда, а второй вход дополнительного элемента И-НЕ первого разряда соединен с инверсным выходом триггера третьего разряда, прямой выход которого соединен с первым входом элемента И, второй вход которого подключен к прямому выходу триггера вто» рого жэряда. 55

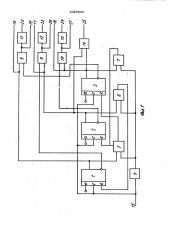

На фиг. 1 представлена структурная схема предлагаемого устройства; на

35 2 фиг. 2 - временные диаграммы, поясняющие его работу.

Устройство содержит триггеры 1 - 3, инвертор 4, элементы И-HE 5 - 7, дополнительные элементы И-НЕ 8 - 10, элементы ЙЕ 11-13, элемент И 14, входную шину Х5 и выходные шины

l6 - 25.

Делитель частоты на три работает следующим образом.

Пусть до подачи тактовых импульсов делитель находился в состоянии 001.

Тогда на выходах элементов 5 и 6 дейсъ вует уровень логической 1, а на выходе элемента 7 - уровень логического О, удерживающий триггер 2 в состоянии, при котором на его выходе присутствует уровень логического О, Так как на обоих входах элемента

10 находятся уровни логической 1, то на выходной шине 21 (фиг. 2э) имеется уровень логического О, а на выходной шине 24 (фиг. 2 д) - уровень логичес- кой 1. На одном из входов логических элементов 8, 10 и 14 находятся уровни логического О, на выходных шинах 19 и 20 (фиг. 2и, к) - уровень логической 1 и на выходных шинах 22, 23 и

25 (фиг. 2 е, ж, л) - уровень логического О.

При приходе первого тактового импульса триггер 1 через некоторое время, определяемое задержкой нереключе"ния, переходит в единичное состояние, так как íà его прямом и инверсном входах действуют уровни логической 1. За это же время на выходе элемента 7 формируется уровень логической 1, подготавливающий триггер 2 .к переклю чению. Во время действия тактового импульса делитель находится в состоянии

101 и изменяется логический уровень на выходе 16 с О" на «1» (фиг. 2в).

Логические уровни на других выходах остаются без изменений.

По окончании тактового импульса на выходе элемента 5 вырабатывается уровень логи 9рского О, устанавливающий триггер 3 в нулевое состояние, т. е. делитель устанавливается в состояние

100, что вызывает устайовку уровней логической 1 на выходах 20 — 22 (фиг, 2 к, з, е) и уровней логического

О на выходах 19, 23, 24 и 25 (фиг. 2 и, ж, д, л).

Аналогично при поступлении второго тактового импульса делитель находится в состоянии 110, а на выходной шине

17 (фиг. 2г) появляется уровень логи3 10278 ческой 1, по окончании второго тактового импульса делитель устанавливается в состояние 010 и на выходных шинах 19, 21 и 23 (фиг. 2 и, з, ж) устанавливаются уровни логической 1, а на выхо»дных шинах 20, 22, 24 и 25 (фиг; 2 к, е, д, л) - уровни-логического

О, при поступлении третьего тактового импульса делитель находится в состоянии .011, а на выходных шинах 18 и 25 30 (фиг, 2 б, л) появляются уровни логической 1, по окончании . третьего тактового импульса делитель устанавливается . в состояние OOl,,появляются уровни логической 1 на выходных шинах 19, 20 и 24 (фиг. 2 и, к Ы и уровень логического 0 на выходных шинах 21, 22, 23, и 25 (фиг. 2 з, е, ж, n), т. е. делитедь устанавливается в начальное состояние.

Исходя из этого длительность пере- 20 . крытия выходных импульсов на выходных шинах 16 - 18 (фиг. 2 в, r, б) равна. длительности тактового импульса

I. плюс задержка переключения триггера по установочному входу, что может быть 25 использовано. при построении генераторов тактового питания приборов с зарядовой связью. Выходные шины 22 - 24 (фиг. 2 е,. ж, д) формируют выходные ,импу сы длительность ко орых ра на . 30 периоду следования входных импульсов, а период равен трем прриодюм входных импульсов..На выходных шинах 19 .- 21 (фиг. 2 и, к, з) формируются выходные

35 4 импульсы, длительность которых равна двум периодам входных импульсов, а период равен трем периодам входных импульсов, что может быть использова но при построении трехфазных распределителей. На выходной шине 25 (фиг. 2л) по каждому третьему входному импульсу появляется положительный импульс., длительность которого равна длительности входного импульса, что может быть использовано при построении пересчетных схем по модулю три.

Предлагаемый делитеж на три может быть выполнен в интегральном исполнении»

Таким образом, за счет незначительных изменений электрической схемы делителя на три получена возможность ис,пользовать его при построении как генераторов тактового питания приборов с зарядовой связью, так и трехфазных распределителей и ересчетных схем по

&QQ 3.

По сравнению с делителем на три, вьшоленнном на 3 -триггерах согласно

ОСТ 11. 340902-78, предлагаемый делитель исключает одновременную установку двух триггеров в состояние 1 при отсутствии входного сигнала из-за появления ньмех по пеням питания. Это обеспечивает выдачу выходного сигнала толь ко по одному из выходов в зависимости от количества входных импульсов, поступивших на вход делителя.

1027835

1027835 ВНИИПИ Заказ 4755/59 Тираж 936 Подписное

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4