Источник калиброванных напряжений

Иллюстрации

Показать всеРеферат

ИСТОЧНИК КАЛИБРОВАНЯИХ НА- j ПРЯЖЕНИЙ ПО авт. св« 943672., о «ч ли ч а юи и и б я Т9М, что, с целью повышения точности в него введены i последовательно.включенные згшатчйк кода опорного напрйженйя и второй преобрг19ователь кода во временной интервал, а выход послед ч него связан с вторым входом матричного коммутатора.

SU„„A

СОЮЗ СОВЕТСКИХ

ШИМИОЗН К

РЕСПУБЛИК Щ) !О 05 F 1 44

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ; ". " ..!,."

К АВ ГОРСКОМУ СВИДДТЕЛЬ У

61 943672 (21) 3355150/24-. 07 (22) 23 ° 11.81 (46) 15 07,83, Вюл, в 26 (72) А.E.Волынский, С,А Рачия и А,A.Ñìêðíîâ (53) 621.316. 722. 1(088.8) (56): 1. Авторское свидетельство

СССР 9 943672, кл. G 05 F 1/44, 1980 ° (54) (57) источник кАливРовАн ых НА-., ПРЯЖЕНИИ по авт св 9 943672., О т л ar ч а в-шийся тем, что, с

-целью иовщаения точности, .в него введеныiиоследовательио включенные

: вадатчик. кода опорного напряжения и второй преобразователь кода во временной интервал, а выход послед него связан с вторйм входом матрнЧкого коммутатора.

1029155

Изобретение относится к электро= технике, в частности к источникам калиброванных напряжений, и предназначено для использования в электротехнических установках различного назначения.

По основному авт.св.Р 943672 известен источник калиброванных напряжений, содержаший регистр памяти, преобразователь код-напряжение, аналоговый сумматор, преобразователь кода во l0 временной интервал, блок опорного напряжения, два коммутатора, два преобразователя напряжения в ток, два ключевых элемента, матричный коммутатор, последовательно вклю- 15 ченные первый и второй блоки интегрирования, блок управления, в котором вход управления устройства связан с входом регистра памяти, первый и второй выходы последнего подключены соответственно к входу преобразователя код-напряжение и входу преобразователя кода во временной интервал, первый и второй входы аналогового сумматора. соединены соот- ветственно с выходом преобразователя код-напряжение и выходом второго блока интегрирования, первый вход первого коммутатора и второй вход второго коммутатора связаны с выходом аналогового сумматора и выходной

30 клеммой, второй вход первого коммутатора и первый вход второго коммутатора соединены с выходом блока опорного напряжения, выход каждого коммутатора через последовательно вклю- З5

f ченные соответствуюшие преобразователь напряжения в ток и ключевой элемент связан с входом первого блока интегрирования, вход управления каждого ключевого элемента 40 соединен с соответствующим выходом матричного коммутатора, первый вход последнего подключен к выходу преобразователя кода Во временной интервал, а входы управления регистра памяти матричного коммутатора, второго блока интегрирования, объединенные первые входы управления йервого и второго коммутаторов,объединенные вторые входы управления первого и второго коммутаторов и вход сброса первого блока интегрирования соединены с соответствующим выходом блока управления 11).

Йедостатком известного устройства является низкая точность работы устройства.

Целью изобретения является повышение точности.

Поставленная цель достигается 60 тем, что в источник калиброванных напряжений введены последовательно включенные задатчик кода спорного напряжения и второй преобразователь кода во временной интервал, а выход последнего подключен к второму вхо= ду матричного коммутатора.

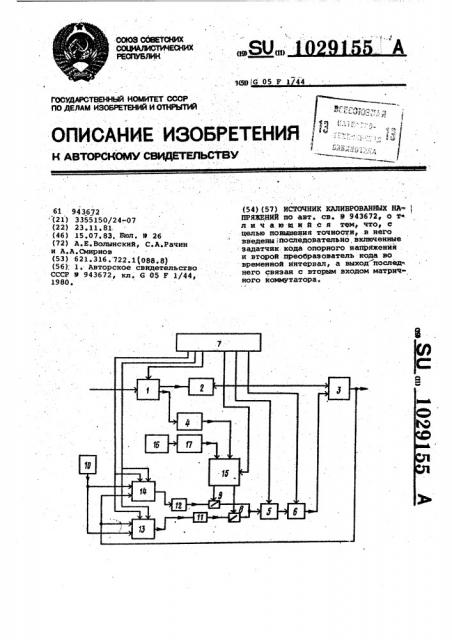

На чертеже приведена структурная схема источника калиброванных напряжений.

Источник калиброванных напряжений содержит последовательно включенные регистр памяти 1, преобразователь код — напряжение 2 и аналоговый сумматор 3, первый преобразователь кода во временной интервал 4, вход которого подключен к второму выходу регистра памяти 1, последовательно включенные первый и второй блоки интегрирования 5 и 6, блок управления 7, первый и второй ключевые элементы 8 и 9, блок опорного напряжения 10, первый и второй преобразователи напряжения в ток 11 и 12, первый и второй коммутаторы 13 и 14, матричный коммутатор 15, последовательно включенные задатчик кода опорного напряжения 16 и второй преобразователь кода во временной интер-,. вал 17, 11ричем вход блока интегрирования 5 через ключевой элемент 8 связан с выходом преобразователя 11, а через ключевой элемент 9 — с выходом преобразователя 12, выход блог ка интегрирования 6 соединен с вторым входом аналогового сумматора 3, первый вход коммутатора 13 и второй вход коммутатора 14 соединены с выходом аналогового сумматора 3, второй вход коммутатора 13 и первый вход коммутатора 14 соединены с выходом блока опорного напряжения 10, выходы коммутаторов 13 и 14 связаны соответственно с входами преобразователей 11 и 12, объединенные первые входы управления коммутаторов

13 и 14 и объединенные вторые входы управления данных коммутаторов подключены к соответствующим выходам блока управления 7, выходы преобразователей 4 и 17 подключены соответственно к первому и второму входам матричного коммутатора 15, первый и второй выходы матричного коммутатора 15 связаны соответственно с входами управления ключевых элементов 8 и 9, а входы управления регистра памяти l,блока интегрирования 6 и матричного коммутатора 15,а также вход сброса блока интегрирования 5 соединен с соответствуюшими выходами блока управления 7.

Устройство работает следуюшим образом.

По команде блока 7 входной код переписывается в регистр 1, при этом на выходе преобразователя 2 устанавливается пропорциональное данному коду напряжение Е . Выходное напряжение сумматора 3 в произвольный момент времени определяется выражением

u»,„Æ= 0„Å„, о 0-), О) 1029155

Процесс установления выходного напряжения устройства носит итерационный характер и осуществляется в течение и циклов, а определение бло ком 5 в каждом цикле алгебраической суммы результатов интегрирования опорного и выходного сигналов занимает два такта, во время каждого из которых интегрируется алгебраическая сумма двух импульсных сигналов. Один 1з из указанных сигналов представляет собой последовательность, состоящую из 2 токовых импульсов амплитуВ да которых пропорциональная опорно- 2О му напряжению Е,а длительность равна - где T> — длительность интерР вала, пропорциональная входному коду регистра 1, а второй сигнал 25 г также является последовательностью из -- токовых импульсов, равномерВ

К но Расставленных внутри интервала фиксированной длительно"ти Т!2, амплитуда этих импульсов пропорциональ- 30 на выходному напряжению 1 стройства (),„(1„-1),i=1,n, а длительность обеспечивается преобразователем 17, Т Т равной =- — N<> в соответствии с коП дом задатчика N = — представляю ..

Оп Е,цф, щим отношение. реального опорного напряжения (например напряжения кон-. кретного опорного стабилитрона)i к его номинальному значению. Перед началом первого такта i-ro цикла 40 блок 7 производит сброс блока 5 и далее подключает входы преобразователей 11 и 12 через коммутаторы

13 и 14 к выходам соответственно блоков 3 и 10; после установления на выходах преобразователей соот, ветствующих токов, 3„„=. $ U(, ).— 1) и

J „= 5 Е, гдето„и, — коэффйциенты передачи преобразователей 11 и 12, блок 7 чеРез матричный коммУтатоР 50

15 подключает выХоды преобразователей 17 и 4 к управляющим входам ключевых элементов 8 и 9. В результате указанных операций на управляющий вход элемента 8 поступает последовательность временных интервалов длительности Т ((на управляющий вход элемента 9 — последовательность интервалов длительностьюТ /Р и на выходе блока 5 вырабатывается пилообразное напряжение как отклик 60 на алгебраическую сумму токовых импульсов, формируемых из выходных сигналов преобразователей. результат данного интегрирования фиксируется в блоке 5, а во втором такте блок 1

0 — =-Е

Тх Т

@ )(у у 7 См 7 где U (t) — напряжение на выходе блока б; л „ 1) - коэффициенты передачи сумматора 3 по соответствующим входам.

5 обеспечивает через коммутаторы 13 и

14 подключение входов преобразователей 11 и 12 соответственно к выходам блоков 10 и 3 и далее по окончании переходных процессов установления выходных токов преобразователей

11 и 12 3(а=9Е иЗ Фэ 0 Р.-1) переключает матрйчный коммутатор 15 в состояние, противоположное исходному.

При этом элемент 8 периодически под. .:,. ключает выход преобразователя 11 к входу блока 5 на времяТ(ф,а элемент

9 периодически подключает выход преобразователя 12 к входу блока 5 на время Т7(1 . Формируеьый блоком 5 пилообразный выходной сигнал алгебраи чески суммируется с результатом ин тегрирования в первом такте,К концу второго .такта цикла напряжение на выходе блока 5 . «а Т РТУ Ц Т ЕР » г" СВ т -» с е „с, 5q+5c ( (ll (g ti- 3t+Erg), (2) де С - емкость интегрирующего кон-. ден"атора блока 5. концу цикла выходное напряжение блока б достигает величины о

Щ1 3=0;ф- 1+ О„t 3, (з) где Т- постоянная времени интегрирования блока б, а на выходе сумматора 3 в соответствии с (1) формируется выходной сигнал устройства

»ix« = 1 "а.(4t " =Uüûõt î3

4i7o %+В

" ЬМХ 1- 3Т + E7„), . (4) где О „ о =Я„Е ц о — исходное значен ние сиги ала н а выходе суммато- ра 3 °

Аналогично прототипу требуем выI 2ТЗТО .Й+6я. полнения условия l+ — «О — .,с и тогда, как можно показать, выходное напряжение устройства сходится в течение нескольких циклов к установившемуся значению

В предлагаемом устройстве, как и в прототипе, благодаря одновремен-, ному интегрированию алгебраической суммы двух токовых сигналов, представляющих опорное и выходное напряжение, уменьшается заряд интегрирующего конденсатора. и, следовательно, снижено влияние эффекта абсорбции на линейность выходной характеристики устройства; аналогично про1029155(Составитель С.Чернышева

Редактор А.Гулько Техред A.Áàáèíåö

КорректоР А. Повх

Заказ .4978/46 Тираж 874

ВНИИПИ Государственного комитета. СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 тотипу выходное напряжение устройства не зависит также от крутизны преобразования напряжений в соответствующие токи и определяется лишь опорным напряжением и отношением длительностей временных интервалов, т.е. предлагаемое устройство не ухудшает ни линейности, ни масштаба прототипа.

Однако, как следует из изложенного, предлагаемое устройство, в 10 отличие от прототипа, обеспечивает номинальную градуировочную характеристику и позволяет избавиться от нестабильного масштабного преобраэов. вателя в блоке опорного напряжения.

Последнее .дает воэможность повысить точность устройства в целом, а также исключить иэ его состава дорого-. стояцее прецизионное изделие (например резистивный делитель, вй™олненный по печатной технологии) и снизить себестоимость источника .калиброванных напряжений.