Интегратор

Иллюстрации

Показать всеРеферат

ИНТЕГРАТОР, содержащий сперапионный усилитель, выход которого является, выходом интегратора и через интегрирующий конденсатор соещшен со входом операшюнного усилителя, первую группу ключей, первый вывод одного из KovGpmx. соединен с выходом, а вторсЛ Через масштабный резистор цепи ной связи со входом опербшионного усилителя , другие ключи первой группы соединены последовательно с маштабным резистором цепи задания начальных условий и входными масштабными резисторами , а управляющие входы ключей пер-, вой группы подключены к соотве1ствующ му управляющему входу интегратора, отличающийся тем, что, с : целью повышения точности интегрирования, в него введены вторая группа ключей, инверто{ 9и и шунтирующие резисторы, соединенные параллельно с соответствующим ключом второй группы и включенные между общими взыводами масштабных резисторов и ключей перьой и шиной яулоэого потенциала, управляющие входы ключей второй группы через ветст)гюаше инверторы соединены с соот : ветствуклцим управляющим входом интег- , erafaae выводы ключей, кроме первого КЛЮ1Ш, первой группы являются соответствующими информационными входами интегратора, а второй вывод маошта &{ого резистора цепи задания начальных условий и вторые вывсщы входных масштабных резисторов подключены ко ВХОДУ операционного усилителя. tC а

А ае а33

СОЮЗ СОВЕТСКИХ

СОЮВЛЮП

РЕСПУБЛИК

606 (л 7/186

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Ю сС

ОС

,еьЦ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И OYHPbfTMA (21) 3348002/18 24

; (22) 23.10.81 (46) 15.07.83. Бюл. -34 26 (72) В. Г. Беляков и В. М. Тимонин (53) 681.335 (088.8) (56) 1. Морозов В. П. и др. Интегра тор и блок сложения-хранения гибридной .вычислительной системы BC-100. Сборник. Гибридная вычислительная система:

ГВС-100. М., Институт щюбаем управ ления, -1974, с. 65-71.

2. Патент CIA l4 3476924, кл. 235-.183, опубцик. 1970.

3. Тетежбаум И..М. и Шнейдер Ю. Р.

400 схем для ABM .Д., Энергия, 1978 ° с. 24 (щютотип). (54) (57} ИНТЕГРАТОР, содержаний операционный усилитель, выход которого является. выходом интегратора и через интегрируюший конденсатор соединен со: входом аперапионного усилителя, первую группу.ключей, первый вывод одного из

: которых соединен с выходом, а второй через масштабный резистор цепи обрат» ной связи со входом операционного усилителя, другие ключи первой группы соединены последовательно с маштабным резистором цепи задания начальных условий и вкодными масштабными резисто рами, а управлякмцие входы ключей первой группы подкпючены к соответствующ му управлякицему входу интегратора, отличающийс ятем, что, с

:целью повыиення точности интегрирования, в него введены вторая группа ключей, инверторн . и шунтирукипие резисторы, соединенные параллельно с соответствуюшим ключом второй группы и включенные между обиами выводамк масштабных ре» зисторов и ключей первой группы к uatной нулевого потенциала, управляккцие входы кличей второй группы через соот д ветстэующие инверторы соединены с cocm- e ратора, вторив выводы «лючей, кроме первого ключа, первой группы являются информапионнымк вхо: дами интегратора, а второй вывод масштабного резистора пепи задания начальных условий и вторые выводы- входных масштабных резисторов подключены ко входу опередионного усилителя.

1 1029

Изобретение относится к устройствам вычислительной техники и ватоматики.

В частности, предлагаемый интегратор предназначен для использования в аналоговых вычислительных машинах. 5

Известны интеграторы с интегрирующи ми и запоминающими конденсаторами в цепи обратной связи операционного усилителя и управпением режимами посредс твом электронных ключей, последова- 30 тельно соединенных с входным масштаб- ным резистором, которые используются в аналоговых. машинах с периодизацией решения Р1 J и 2).

Недостаток таких интеграторов за- f5 ключается в невысокой точности интегри- рования, обусловленной протеканием токов. утечки иэ цепи управления электронных ключей и переносом заряда через параэитные элементы иэ цепи управления 20 и коммутации на интегрирующий конденсатор»

Наиболее близким к предлагаемому по технической сущности является интегратор, содержащий операционный усили«25 тель, интегрирующий конденсатор, включенный в цепь оЪратной связи операционного усилителя, входные масштабные резисторы, резисторы для задания начальных условий, подключенные ко входу one- g0 рационного усилителя, ключи, коммути,"рующие входной масштабный резистор и общую цепь соединения резисторов для задания начальных условий с инвертирующим входом операционного усилителя t, 3J 35

При интегрировании входных сигналов в режимах одноразового и MHQFoKpRTHOI o пуска и останова (интегрирования с накоплением информации) на конечный результат интегрирования заметно влияют погрешности, обусловленные переносом заряда через паразитные элементы иэ цепи управления и коммутации на интегрирующий конденсатор, и токами утечки ключей . на вход операционного усилителя. Величина этих погрешностей зависит от величины емкости, интегрирующего конденсаI тора, амплитуды входного и управляющего сигналов, а также величины токов утечек управляющих ключей..

Бель иэооретения - повышение точнос-, ти интегрирования входных сигналов.

Указанная цель достигается тем, что в интегратор, содержащий операционный усилитель, выход которого является вы.ходом интегратора и через интегрируъяций конденсатор соединен со входом операционного усилителя, первую группу кшо187, 3 чей, первый вывод одного из которых соединен с выходом, s иторой через мас штабиый резистор цепи обратной связи со входом операцйонного усилителя, другие ключи первой группы соединены последовательно с маштабным резистором цепи задания начальных условий и входными масштабными реэисгорами, а управляющие входы ключей первой группы подключены к соответствующему входу ин« тегратора, введены вторая группа ключей, инвврторы и шунтирующие резисторы, соединенные параллельно соответствующим ключом второй группы и включенные между общими выводами масштабных резисторов и ключей первой группы и шиной нулевого потенциала, управляющие входы ключей второй группы через соответствующие инверторы соединены с соответствующим управляющим входом интегратора, вторые выводы ключей, кроме первого ключа, первой группы ключей являются . соответствующими информационными вхо -лами интегратора, а второй вывоа мас/ штабного резистора цепи зацания йекль ных условий и вторые выводы входных масштабных резисторов подключены ко входу операционного усилителя.

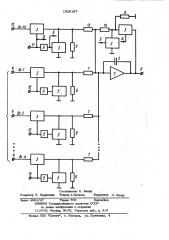

На чертеже изображена структурная схема интегратора.

Интегратор содержит операционйый усилитель 1, интегрирующий конденсатор 2, ключи 3 первой группы ключей, информационные входы 4 интегратора, ключи 5 второй группы ключей, шунтирующие резисторы б,входные масцттабные резисторы 7, выход операционного усилителя 8, инверторы 9 цепи управления ключами, управляющие входы 10 и

11 интегратора, вход 12 задания началь-, ных условий, масштабные резисторы ж:дания начальных условий 13 и обратной связи 14.

Интегрируимций конденсатор 2 включен в цепь обратной связи онерационного усилителя. Первые выводы ключей 3 со-! единены с входами 4 интегратора и входом 12 задания начальных условий. Клю чи 5 второй группы ключей эашунтированы резисторами 6. Первые выводы ключей

5 соединены с шиной нулевого потенциа ла, а вторые выводы - с вторыми выводами ключей 3 и соответственно через масштабный резистор 7 и масштабный резистор 13 цепи эаденил начальных ус- ловий со входом операционного усилителя 1,, выход 8 операционного усйлителя 1, яв- ляющийся выходом интегратора соединен

3 1029 с первым выводом одного из ключей 3 первой группы ключей. Управляюаае вхо ды ключей 3 и 5 включенй в про жво фазе через инверторы 9. Входы ипверюо

10 и 15.

Интегратор содержйт несколько (И.) .. входов 4. Рассмотрим работу схемы по одному . ювду.

Интегратор работает следуюаам об- - 6 разом е

При интегрировании входного сигнала, последний через входной аналоговый. ключ

3 поступает на входной резистор 7 и вызывает протекание тока через. интвгрнруиъ 15 ший конденсатор 2. При этом токе утеч ки от цепи управления ключей 3 и 5, и дополнительный сигнал, обусловленный переносом заряда через «паразитные» составляюшие емкостей из цепей управ- пения и коммутации аналоговых ключей на интегрируюший конденсатор, шунти- руются низкоомными входными цепями и сопротивлением заьп нутого ключа 3.

Аналоговый ключ 5 в режиме интегрирования разомкнут. В режиме хранения информации аналоговый ключ 3 размыка ется, а аналоговый ключ 5 замыкается, и это приводит к тому, что токи утечки от цепи управления и дополнительный ЗО паразитный сигнал из цепей управления и коммутации аналоговых ключей щунти» руются на шину нулевого потенциала низ ким сопротивлением замкнутого аналого вого ключа 5. З5

В режиме "Исходное состояние в цепи задания начальных условий по входу

12 3 открыты <а ключи 5 закры . ты, и интегрирукпций конденсатор 2 за ряжается инвертором начальных условий до 3 влкчиныф равной минус U Эх НУб При интегрировании и хранении информации. . в цепи задания начальных условий клю, чи 5 открыты, а ключи 3 закрыты. Ра" ота ключей схемы в цепи задания на ю

1S7 4 чальщж условий аналогична работе клю. чей по входам 4. Во время переходного дропвсса, когда ключи 3 и 5 неполностью

: замкнуты, токи утечки и царазтные со: етавляюпие сигнала из цепей управления

: и коммутации шунтируются на шину нулевого потенцила через доцолнитепьный резистор 6.

Поэтому перенос заряда через паражтюае элементы ключей на интегрируюший каищенсатор и токи утечки клкяей

-sa вход операционного усилителя будут минимальны и не повлияют на конечный результат интегрирования..В щюдлагаемом устройстве за счет введения неболыаого числа дополниквш ных элементов и установки на входе cxe« . точность «ак в режиме одноразового, так и в режиме многокражого цусима и оста( формации) путем уменьшения погрешностей, обусловленных переносом заряда через паразитные элементы из цепи управления и коммутации на интегрируюший конденсатор-и токами утечки ключей на вход операционного усилителя.

Испытывается макет блока БИ-41. ,Рез лыаты испытаний цока@юают, что в (Жиме миогократно1 о пуска и останова

{интегрированная с накоплением информа пии) величины погрешности интегрирования для-разных3(С-пеночек находятся на уров-.

:;не погрешностей блока БИ-31, работаюmего в режиме одноразового интегрирования. Лучший базовый обьект интегра . тор- с периодизацией решенйя (блок БИ-31), входящий в состав серийно вы пускаемой аппаратуры АВК-32, АВК-33 не пойволяет получить величину погрешsocm s режимах интегрирования с накоплением информации для разных С пеночек на уровне погринностей в рэжиме одноразового интегрирования.

1029187

Составитель С. Белан .

Редактор Т, Парфенова Техред А.Бабинеп КорректоР О. Билак"

Заказ 4981/47 Тираж 706 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушскаи наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4