Запоминающее устройство

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

3(58 G 11 С 11/00

ОПИСАНИЕ ИЗОБРЕТЕНИ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPbiTHA (21 ) 3354682/18-24 (22) 23.11.81 (46 ),15..07.83. Бюл. В 26 (72) В.К. Конопелько (71 ) Минский радиотехнический институт (53) 621. 327. 6(088. 8 ) (56 ) 1. Авторское свидетельство СССР

Р 746741, кл. G 11 С 11/00, 1978.

2. Авторское свидетельство СССР по заявке СССР Р 3248689/24 кл. G 11 С 11/00, 1981 (прототип). (54 )(57 ); ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, . содержащее, накопитель, первая группа входов которого является адресными входами первой группы устройства, входы второй группы накопителя соединены с выходами первой группы блока элементов И и со.входами первой группы блока усилителей считывания,.входы второй группы которого соединены с выходами вто-. рой группы блока элементов И и с выходами накопителя, выходы блока усилителей считывания соединены. со входами элемента ИЛИ н входами первой группы блока мажоритарных элементов, входы второй rgynma которого являются адресными входами второй группы устройства, à вы ходы соединены со входами селектора, выходы которого соединены с первым входом первого коымутатора, второй вход которого соединен с выходом элемента ИЛИ, а выход является информационным выходом устройства, дешифратор, первая группа входов которого является адрес,SU„„1029228 А ными входами третьей группы устрой ства, первый, второй н третий управляющие входы блока элементов И, являются первым, вторым, третьим упразлякшнми входамн устройства, третий вход первого коввюутатора соединен е первым управляющим входом блока элементов И, о т л и ч аю щ е е с я тем, что, с целью повышения надежности устройства, .оно содержит блок формирователей четности, второй коммутатор, элемент

И, инвертор, блок адресных формирователей, входы первой и второй -. групп которого соединены с выходамн дешифратора, входы второй группы которого соединены с выходамн второго коммутатора, управляющий вход которого соединен с первым управляющим входом блока адресных формирователей и выходом инвертора, вход которого соединен с первым входом элемента И и является

Ф четвертьаа упразляжщнм входом устройства, зьисод элемента И соединен с четвертым входом nepsoro коьеаутатора, а второй вход соединен с первым вх<щом второго коммутатора и язляетея первым старшим адресным входом устройства, второй вход второго коммутатора является вторым стадиям адресным входом устройства, второй вход блока адресных фор.мирователей является пятым управ- ляющим входом устройства, входы блока формирователей четности соединены с входами второй группы устройства, а выходы соединены со входаэаи блока элементов И.

1029228

Изобретение относится к вычислительной технике и может быть использовано при изготовлении больших

° интегральных схем запоминающих устройств с произвольной выборкой и матричной организацией (ЗУПВ).

Известны ЗУПВ с матричной организацией, которые содержат матрицу элементов памяти, схемы логики обра" ления и коррекции, дополнительные элементы памяти Р13.

Недостатком этих устройств является низкая надежность из-за коррекции только однократных ошибок в слове и необходимости введения дополнительных элементов памяти и сложности схем коррекции.

Наиболее близким к изобретению по технической сущности и схемному решению является запоминающее устройство, содержащее дешифратор адреса, блок считывания, шины управления и записи считывания, элементы И, ИЛИ, накопитель и позволяющее повысить надежность запоминающего устройства за.счет коррекции дефектов элементов памяти 2) .

Недостатком устройства является низкая надежность устройства изза возможности возникновения оши-бок в различных частях накопителя.

Цель изобретения — повышение надежности устройства за счет обеспечения воэможности использования запоминающего устройства с дефектами в различных частях накопителя.

Поставленная цель достигается тем, что запоминающее устройство, содержащее накопитель, первая группа входов которого является адресными входами первой группы устройства, входы второй группы накопителя соединены с выходами первой груп-, пы блока элементов И и со входами первой группы блока усилителей считывания, входы второй группы которого соединены с выходами второй группы блока элементов И и с выходами накопителя, выходы блока усилителей считывания соединены с со входами элемента ИЛИ и входами первой группы блока мажоритарных элементов, входы, второй группы которого являются адресными входаьм второй группы устройства, а выходы соединены со входами селектора, выходы которого соединены с первым входом первого кою утатора, второй вход которого соединен с выходом элемента ИЛИ, а выход asляется информационным выходом устройства, дешифратор, первая группа входов, которого является адресными входами третьей группы устройства, первый, второй и третий управляющие входы блока элементов И являются первым, вторым, третьим управФ

Ф ляющим входом устройства, третий вход первого коммутатора соединен с первым управляющим входом блока элементов И, дополнительно содержит блок формирователей четности второй коьв утатор, элемент И, инвертор, блок адресных формирователей, входы первой и второй групп которого соединены с выходами дешифратора, входы второй группы которого соединены с выходами второго коммутатора, управляющий вход которого соединен с первым управляющим входом блока адресных формирователей и выходом инвертора, вход

35 которого соединен.c первым входом элемента И и является четвертым управляющим входом устройства, выход элемента И соединен с четвертым входом первого коммутатора, а второй вход соединен с первым входом второго коммутатора и является первым старшим адресным входом устройства, второй вход второго сумматора является вторым старшим адресньм входом устройства, второй вход блока адресных формирователей является пятым управляющим входом устройства, входы блока формирователей четности соединены с входами второй группы устройства, а выходы

-З0,соединены со входами блока элементов И.

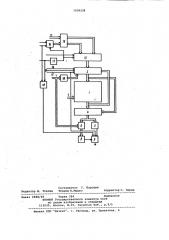

На чертеже представлена функциональная схема запоминающего устройства.

Запоминающее устройство содержит накопитель 1, первая-группа входов которого является адресными вхо" дами 2 устройства первой группы, входы второй группы накопителя 1

40 соединены с выходами первой группы блока элементов И 3 и со входами первой группы блока усилителей считывания 4, входы второй группы которого соединены с выходами второй группы блока элементов И 3 и с выходами накопителя 1, выходы блока усилителей считывания 4 соединены со входами элемента ИЛИ 5 и входами первой группы блока мажоритарных элементов 6, входы второй группы которого являются адресными входа-, ми второй группы 7 устройства, а выходы соединены со входами селектора 3, выход которого соединены с первым входом первого коммутатора 9, втброй вход icomporo соединен с вы ходом элемента ИЛИ 5 и выход является информационным выходом устройства, дешифратор 10, первая группа входов которого является адресными входами третьей группы 11 уст- ройства, первый, второй и третий управляющие входы блока элементов И 3 являются первым 12, вторым 13 и третьим 14 управляющим входами устройства, третий вход первого ком1029228 мутатора 9 соединен с первым 12 управлг.ощим входом блока элементов

И 3, блок адресных формирователей

15, входы первой и второй групп которого соединены с выходами дешифратора 10, входы второй группы которого соединены с выходами второго коммутатора 16, управляющий вход которого соединен с первым управляющим входом блока адресных формирователей 15 и выходом инвертора 16

17; вход которого соединен с первым входом элемента И 18 и является четвертым управляющим входом устройства, выход элемента И 18 соединен с четвертым входом первого коммутатора 9, а второй вход соединен с первым входом второго коммутатора и является первым старшим адресным входом устройства, второй вход второго коммутатора 16 явля- 2@ ется вторым старшим адресным входом устройства, второй вход блока адресных формирователей 15 является пятым управляющим входом устройства, выходы блока формирователей четности 19 соединены с входами второй группы 7 устройства, а выходы соединены со входами блока .элементоэ И 3.

Устройство работает следующим образом. 36

В случае, когда накопитель полностью исправен или исправны три его четверти, или половина его накопителя, то. работа происходит обычным образом. > 35i В случае, когда в накопителе исправна только одна четверть, а в остальных трех нодматрицах имеется не более одного отказавшего элемента памяти из трех одновременно щ опрашиваемых элементов памяти для каждого слова, работа устройства происходит следующим образом.

На пятый управляющий вход устройства подается единичный сигнал,. на входы 7 - сигналы, которые указывают какая из подматриц исправна. Тогда в режиме записи информации при подаче сигналов на шины разрешения записи 14, записи 13, управления 12 в соответствии с сигналом на шинах 2 и сигналом на старшем адресном входе устройства на входах 11 дешифратора 10 происходит запись информации в опрашиваемых блоком адресных формирователей элементах памяти. При этом, если на старшем адресном входе имеется ну-левой сигнал, то опрашивается элемент памяти из исправной нодматрицы. Если на этом входе будет единичный сигнал, то опрашивается одновременно три элемента памяти (по одному из дефектных подматриц) по адресу определяемому с выходов дешифратора 10, поскольку при этом. в формирователях четности 19 происходит инвертирования сигнала со входов 7. Тогда сработают соответствующие формирователи из блока 15 и произойдет запись информации.

В режиме считывания сигналы по шинам 13 и 14 отсутствуют. При этом если на старшем адресном сигнале единичный сигнал,,то онрашиваются элементы памяти из дефектных подматриц. Информация, считываемая и трех дефектных подматриц, поступает на входы мажоритарных элементов б и на элементы ИЛИ 5. На одном из выходов мажоритарных элементов памяти появится правильный сиг- нал. С помощью селектора 8 и коммутатора-9 осуществляется выдача его на выход устройства..

В случае, когда в матрице памяти нет полностью исправной подматрицы, но имеется как минимум трн подматрицы, в которых содержится .не более одного отказавшего .элемента памяти нэ трех одновременно опрашинаемас, работа устройства происходит аналогично описанному, только на входы 7 подаются сигналы, котоуле указывают, какие из подматриц яе иснольэуются.

Жакюа образом возможно использование устрбйства с дефектными элементами, что свидетельствует о повышении надежности устройства.

1029228

Составитель Г. Бородин

Редактор М. Товтин Техред К.Мыцьо Корректор С. Черни

Заказ 4988/49 Тираж 594 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открйтий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4