Запоминающее устройство с коррекцией информации

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

ОИ Л%

РЕСПУБЛИК (1Е (И) (50 G 11 С 29/00

ГОСУДРРСТМЙНВЙ HOIAHYKT. ОССРI_#_ Ì Й .В ВЮ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ вЂ” н A97dpocNY Вюмюивсйаь

4 с (21) 3292224/18-24. (22) 25. 05. 81 (46) 15.07.83. Бюл. 9 26 (72) О.А. Алекаеев (53 3 681. 327 (088. 8 )

{56 ) i. Авторское свидетельство СССР

В 492935, кл. 8 11 .С 29/00, 1972.

2. Вопросы радиоэлектроники.

Серия ЭЬТ, вып. б, 1969, с. 45-53 (прототип). (54 )(57) ЗАПОМИНАЮЩИМИ УСТРОЙСТВО С

КОРРЕКЦИБИ- ИНФОИФЦКИ, содержащее ,блок памяти адресов де4ектных эле ментов памяти и регистр адреса, входы которых объюа йе@ы и являются адреснымн входамн устройства, а выкоды соединены со. вкодавав дема- ратора адреса, раэрядйые блоки памяти и .накевмтелЬ, нрвчем входы на. копителя и адресмйе евно первогоразрядного блока памяти соединены с выкодамн демифратора адреса, о тл и ч а в щ е е с я тем, что, с целью упрощения устройства, в нем адресные инны каждого разр щного блока ламятн, соединенные с дефектиыми элементамн намятй данного раэрядного блока памяти, подключены к адресньэ4 иииимФ свнвйаик раэрждмык блмжов цдмт% соединенным с де4ек-тными элементамн лаветн данных Раэряднык блоков памяти.

1029229

Составитель . В. Рудаков

Редактор И. Товтин Техред К Мыцьо Корректор С., Черни

Заказ 4988/49 Тираж 594 Пщфзн сяое

ВЯИИПИ Государственного комитета СССР по делам изобретений к открытий

113035, Москва, Ж-35, Раужкая каб., д.4/5

Филиал ппп "патент", г . Ужгород, ул. проеитная, 4

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устрой° ствах.

Известно запоминающее устрой-. ство с коррекцией информации, содержащее основной и дополнительный накопители, регистры адреса и чис° ла, дешифратор и блок коррекции $1).

Недостатком этого устройства является сложность и громоздкость блока коррекции.

Наиболее близким техническим ре- шением к изобретению является запоминающее устройство с коррекцией информации, содержащее. основной и дополнительный многоразрядные накопителиg.собранные из матричных мо дулей, блок хранения кодов дефектных адресов уцравляющий дешнф ратором адресов, подключенным к адресным входам накопителей, регистр числа, соединенные с кнформацион нымк входами накопителей и регистр адреса, включенный на вход дешифратора 2)э

Однако случайный характер расп-. ределения дефектных элементов.памяти в объеме основного накопителя требУет бОльшоГО Объема блока хранения кодов дефектных слов и большой емкости дополнительного накопителя, разрядность которого ке завкснт от колкчества дефектов в блокируемом слове, прн этом исправные элементы блоккруемых слов исключается кз работы.

Это устройство также является сложным к громоздким.

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем, что s эапомккаецем устройстве с коррекцией кк4юрмации, содержащем блек намети адресов дефекткых ячеек памяти к регистр адреса, входы которых объединены и являютая адресными входами устройства, а выходы соедккюйы «х) входамк,хФ» аифратора адреса, разрядке блоки памяти к накопитель, кричем входы какощетеля к адресные шккы первого разрядного блока памяти соединены с вьаюдами дешкфратора адреса, адресалые шины каждого разрядного блока памяти, соединенные с дефектными элементами памяти данного разрядного блока памяти, подключены к адресным шинам разрядных блоков памяти, соединенным с дефектными элементами памяти данных разрядных блоков памяти.

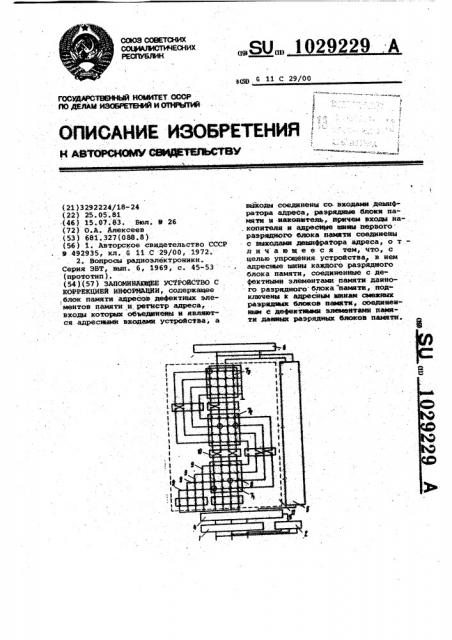

На чертеже изображена функциональная схема запоминающего устройства с коррекцией информации.

Устройство содержит регистр 1 адреса, блок 2 памяти адресов дефектных ячеек памяти, имеющий выход 3, дешифратор 4 адреса, нако35 питель 5, регистр 6 числа, разрядные блоки 7 -7 памяти (для прк1 мера на чертеже изображены трн магнитных блока 7 — 7 памяти, каждый из которых содержит 16 дефектных элементов 8 памяти, выполненных на ферритовых сердечниках). С элементамн 8 памяти связаны адресные шины 9. Соединение адресных шин 9. блоков 7 — 7 осуществляется

25 конструктивно например при помощи соединительных узлов 16. Блоки 7, †. Q и соединительные узлы

10 образуют накопитель 11.

Устройство работает следующим образоме

Ярк обращении к ячейке памяти, не содержащей дефектных элементов 8. памяти, па адресу из регистра 1 через дешифратор 4 выбкраетоя ячейка памяти в накопителе 11 к ее со35 держимое поступает в регистр б.

Прк обращении к ячейке памяти, содержащей дефектные элементы 8 памяти (на чертеже отмечены кружкамн) ° блок 2 переадресует через деаыфраЕ тор 4 обращение к соответствующей ячейке памяти накопителя 5.

Технико экоиомкчес4сое. щюкмуще ство описанного устройства перед прототипом заключается в его простоте, Упрощение достигается за счет тохо, что дефектные элементы памяти объедиииются в ячейки памяти с максимальным числом дефектных элементов памяти, что уменьшает число дефектных ячеек памяти, 5© т.е. уменьшает объем накопителя

-5, и следовательно, упрощает все устройство.