Цифро-аналоговый преобразователь

Иллюстрации

Показать всеРеферат

ЦИФРО-АНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ , содержащий источник опорного напряжения, регистр, вход которого соединен с входной шиной, блок управпе ния, преобразователь кода в напряжение, выход которого через последовательно включенные аттенюатор и усилитель соединен с выходной шиной, отличающийся тем, что, с целью упрощения и расшгфения функциональных возможное-, тей в него введены постоянное запомвнающее устройство, мультиплескор, интегратор и коммутатор, первый и второй входы которого соединены соответственно с выходами уснпитепяИ источника опориого напряжения, а выход через ингеграт с первым входом преобразователя кода в напряжение, второй вход которого пощсточен к выходу мультиплексора, первый и второй входы которого соединены соот ветственно с выходами постоянного запоминающего устройства и регистра , причем (Л первый и второй выходы блока утфавпевня подключены к третьим входам мультиплексора и коммутатора соответственно. О ю CD 4 Р 00

„„SU„„1029408

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧ ЕСНИХ

РЕСПУБЛИН уды H 03 К 13/02

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

J ,с

1 о

l p

ОПИСАНИЕ ИЗОБРЕТЕНИЯ - - -"/

H ABTOPCH0MY СВИДЕТЕПЬСТБУ

;(21} 3323562/18-21

Ф

° °

° а а (22) 23.07. 81 (46) 15.07.83, Бюл. ¹ 26 (72) 10,А. Медведев, В.Т. Басий и 10.В. Сташкив (53) 681.325 (088,8) (56) 1. 111ило В.Л. Линейке интегральные схемы в радиоэлектроннй аппаратуре.

М„"Сов. радио, 1979 с. 344 рис.8.27., 2. Микроэлектронные цифро-аналоговые и аналого-цифровые преобразователи информапии. Под ред. В.Б. Смолова, Л., Энергия", 1976, с. 197, рис.7 - 9(прототип) . (54) (57) ХХИФРО-АНАЛОГОВ Ы Й ПРЕОБРАЗОВАТЕЛЬ, содержащий источник опорного напряжения, регистр, вход которого соединен с входной шиной, блок управле., 1 ния, преобразователь кода в напряжение, выход которого через последовательно включенные аттенюатор и усилитель соединен с выходной шиной, о т л И ч а ю» шийся тем, что, с целью упрощения и расширения функциональных возможнос = тей в него введены постоянное запоминакяцее устройство, мультиплескор, интегратор и коммутатор, первый и второй входы которого соединены соответственно с выходами усилителя и источника опорного напряжения, а выход через интеграторс первым входом преобразователя кода в напряжение, второй вход которого подключен к выходу мультиплексора, первый и второй входы которого соединены соот .. ветственно с выходами постоянного запо- д минающего устройства и регистра, причем первый и второй выходы блока управления подключены к третьим входам мультиплексора к коммутатора cooraercraeaao. (»

1029408 2

Изобретение относится к информацион но-измерительной технике и может быть использовано в технике телевизионных-измерений.

Известен цифро-аналоговый преобразо-. ватель (UAII), содержащий преобразователь код — ток, источник опорного напряжения и усилитель (1 ) .

Недостатком данного устройства является значительная погрешность преобразова- 10 ния,- обусловленная невысокой точностью параметров резистора в обратной связи усилителя относительно резисторов в матрице преобразователя код — ток, Известен также ПАП, содержащий ис- 15 точняк опорного напряжения, регистр, вход которого соединен с входной шиной, блок управления, преобразователь кода в напряжение, выход которого, через последовательно включенные аттенюатор и усилитель/0 соединен с выходной шиной (23 .

Недостаток известного ILAH - слож-.. ность функциональной схемы И ограниченные функциональные воэможности, не позволяющие менять масштаб выходного сит нала при постоянном напряжении на выходе источника опорного напряжения.

Цель изобретения — упрощение и расширение функциональных возможностей устройства. 30

Поставленная цель достигается тем, что в цифро-аналоговый преобразователь, содержащий источник опорного напряжения, регистр, вход которого соединен с вход35 ной шиной, блок управления, преобразователь кода в напряжение, выход которого через последовательно включенные аттенюатор и усилитель соединен с выходной шиной, введены постоянное запомицающее 4 устройство, мультиплексор, интегратор и коммутатор, первый и второй входы которого соединены соответственно с выхода ми усилителя и источника опорного напряжения, а выход через интегратор — с пер45 вым входом преобразователя кода в напряжение, второй вход которого подключен к выходу мультиплексора. Первый и второй входы мультиплексора соединены соответственно с выходами постоянного запоминающего устройства и регистра, причем первый и второй выходы блока управления п9дключены к третыпм входам мультиплексора и коммутатора соответственно, 55

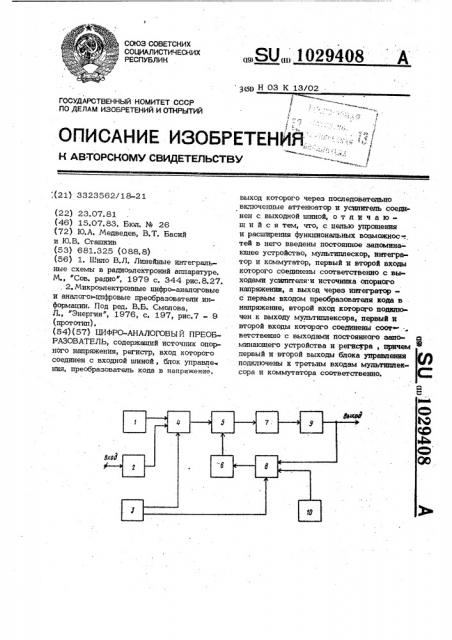

На чертеже представлена блок-схема цифро-аналогового преобразователя.

Цифро-аналоговый преобразователь со» держит постоянное запоминающее устройство 1, регистр 2, блок 3 управления, мультиплексор 4, преобразователь 5 кода в напряжение (ПКН), интегратор.6, аттенюатор 7, коммутатор 8, усилитель 9, источник 10 опорного напряжения.

Цифро-аналоговый преобразователь работает в двух режимах:

1. Режим коррекции погрешностей коэффициента передачи последовательно соединенных преобразователя 5 кода в напряжение, аттешоатора 7 и усилителя 9.

2. Режим работы — преобразование кодов, поступающих на вход цифро-аналогового преобразователя, в напряжение, форми° руемое на его выходе.

В реале коррекции погрешностей цифровой эквивалент источника 10 опорного напряжения (параллельный двоичный код, формируемый в постоянном запоминающем устройстве 1 и равный с точностью цены единицы младшего разряда выходному напряжению источника 10 опорного напряже-. ния) через мультиплексор 4 поступает на цифровой вход преобразователя 5 кода в напряжение На выходе преобраэователя5 кода в напряжение появляется импульс напряжения, противоположный по знаку напряжению источника 10 опорного напряжения, с точностью, определяемой коэффициентом передачи преобразователя 5 кода в напряжение. Аттенюатор 7 ослабляет выходное напряжение преобразователя 5 кода в напряжение до необходимой величины, выходное напряжение аттенюатора 7 инвертируется усилителем 9. С выхода усилителя 9 сигнал поступает на выходную шину цифро-аналогового преобразователя. и на вход коммутатора 8, на второй вход которого поступает выходное напряжение источника 10 опорного напряжения.

Коммутатор 8 под воздействием сигналов с блока 3 управления задает соотношение напряжений с выходов усилителя 9 и источника 10 опорного напряжения поступакзцих на интегратор 8, следукацим образом.

Пусть, например, выходное напряжение источника 10 опорного напряжения составляет -8В, а ослабление аттенюатора 78 раз, тогда на выходе усилителя 9 в режиме коррекции формируется напряжение +1В (без учета погрешностей коэффициента передачи блоков 5,7,9). Длительности импульсов, вырабатываемых блоком 3 управления, относятся соответственно как 1: 8. Управление коммутатором 8 производится таким образом, что напряжение с выхода усилителя 9 (1В) подается на вход интегратора 6 в течение 8 еда8 4 в диапазоне рабочих температур 1045 С.

В режиме работы коммутатор 8 отклю чает напряжение с выходов усилителя 9 и источника 10 опорного напряжения от входа интегратора 6, который обеспечивает хранение накопленного напряжения на время работы.

Мультиплексор 4 отключает от цифрового вхоца преобразователя 5 коаа в напряжение выход постоянного зацоминакзцего устройства 1 и подключает выход регист.— р г.

Использование новых элементов пос тоянного запоминаюшего устройства, муль типлексора, интегратора и коммутатора позволяет значительно уменьшить погрешность цифро-аналогового преобразования и преобразований, вызванных необходимостью сопряжения выходного напряжения ПАП, и цены единицы младшего разряда с диапазоном и полярностью измеряемого сигнаа в рабочем диапазоне температур.

3, 102940 ниц времени, и напряжение с выхода источника 10 опорного напряжения (-8В)в течение единицы времени. При отсутствии погрешностей в преобразованиях сигнала в блоках 5,7,9 выходное напряжение

5 интегратора 6 после коррекции погрешнос- . тей останется таким же, как и до Коррехции. При наличии указанных погрешностей выходное напряжение интегратора 6 после коррекции погрешностей останется таким же, как и до коррекции. При наличии укаэанных погрешностей выходное напряжение интегратора 6 будет изменяться таким образом, что погрешности будут компенсироваться за счет применения опорного напряжения ПКН 5, вырабатываемого интегратором 6. Точность коррекции при медленных измерениях погрешностей преобразования в блоках .5,7,9 будет ограьп чиваться только стабильностью напряжения смешения операционного усилителя интегратора 6 и выходного напряжения источника 10 опорного напряжения полной шкалы л

Редактор С. Лисина ТехредМ.Коштура! Корректор Ю.Макаренко, Заказ 5001i58 Тираж 936 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., и. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4