Устройство для сопряжения

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ , содержащее блок ввода, информационный и установочный входл которого являются входаг и устройства, первый выход которого соединен с первым управляющим выходсда блока ввода , второй управляющий выход которого соединен с первьзми входами первого коммутатора, буферной памяти и блока управления, первый и второй выходы которого соединены с тактовыми входами блока ввода, первый информационный выход которого соединен с вторым входом первого коммутатора, выход которого соединен с первым входом второго коммутатора, выход которого соединен с входом буферной памяти, третий вход которой соединен с вторым инфо ационнь 1 выходом блока ввода, генератор, выход которого соединен с вторьм входе блока управления и первьвл входом регистра сдвига, выход которого через суг/алатор соединен с вторым выходом устройства, вторюй вход регистра сдвига соединен с третьим выходсм блока управления, входом распределителя и первым входом первого счетчика, выход которого соединен с вторь 1 входом второго коммутатора , третий вход которого соединен с четвертым выходом блока управления и вторым входом первого счетчика, первый, второй и третий выходы распределителя соединены соответственно с входом сумматора, первым входе второго счетчика и третьим входом блока управления, пятый и третий выходы которого соединены соответственно с третьим входом первого коммутатора и вторым входом второго счетчика, выход которого соединен с четверть входом первого коммутатора, шестой и седьмой выхогил блока управления соединены с четвертью и пятьвл входами буферной памяти, отличающеес я тем, что/ с целью упрощения S устройства и повышения коэффициента использования оборудования, в него сл введены блок формирования команд за- , держек и регистр, причем выход буфер- .ной памяти через регистр соединен с третьим входе регистра сдвига и первьэ входом блока формирования команд Зсщёржек, выход которого соединен с четвертым входом регистра сдвига и четвертым входом управления , восьмой выход которого соединен с входсяи регистра и вторым оо о входом блока формирования команд задержек, третий и четвертый входа которого соединены соответственно с третьим выходом управления блока CD управления и третьим выходом распределителя . 2. Устройство по п.1, отличающееся тем, что блок форми рования команд задержек содержит счетчик г два триггера, три элемента И, причем выход блока соединен с информациэнным входом счетчика и первым 3XORCM первого элемента Н, второй : ход которого соединен с вторым входом блока, третий вход которого соединен через второй элемент И с первыми входами счетчика и пер-аого триггера, вторые входы которых

союз советских социдлистичесних

РЕСПУБЛИК..SU„„1030791 А В G 06 F 3/04

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГосудАРствекний комитет щи

re делиа изоБретений и открытий (21 j 3388809/18-24 (22) 24 ° 02. 82 (46) 23. 07. 83. Бюл. Р 27 (72) P Ñ. Лачинов (71) Институт океанологии им. П.П.Ыир шова AH СССР . (53) 681.3(088.8) (56) 1. Авторское свидетельство СССР

Р 734759, кл. G 06 Р 3/04, 1977, 2. HP 912008 ТЧ lNTKRPACE КТТ

Jnstallatich and service mannal.

Printed: Jan. 1976, Hewlett Packard

Company,11О0ОЫо1йе Road, USA(прототип) .

{54)(57) 1. УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ, содержащее блок ввода, информационный и установочный входы которого являются входами устройства, первый выход которого соединен с первым управляющим выходом блока ввода, второй управляющий выход которого соединен с первыми входами первого коммутатора, буферной памяти и блока управления, первый и второй выходы которого соединены с тактовыми входами блока ввода,.первый информационный выход которого соединен с вторым входом первого коммутатора, выход которого соединен с первым входом второго коммутатора, выход которого соединен с вторым входом буферной памяти, третий вход которой соединен с вторым информационным выходом блока ввода, генератор, выход которого соединен с вторьж входом блока управления и первым входом регистра сдвига, выход которого через сумматор соединен с вторым выходом устройства, второй вход регистра сдвига соединен с третьим выходом блока управления, входом распределителя и первым входом первого счетчика, выход которого соединен с вторым входом второго коммутатора, третий вход которого соединен с четвертым выходом блока управления и вторым входом первого счетчика, первый, второй и третий выходы распределителя соединены соответственно с входом сумматора, первым входом второго счетчика и третьим входом блока управления, пятый и третий выходы которого соединены соответственно с третьим входом первого коммутатора и вторым вход и второго счетчика, выход которого соединен с четвертым входом первого коммутатора, шестой и седьмой выходы блока управления соединены с четвертым и пятым входами буферной памяти, о т л и ч а ю щ е ес я тем, что, с целью упрощения устройства и повышения коэффициента ® использования оборудования, в него введены блок формирования команд за держек и регистр, причем выход буфер ной памяти через регистр соединен с третьим входом регистра сдвига и первым входом блока Формирования команд задержек, выход которого соединен с четвертым входом регистра сдвига и четвертым входом блока управления, восьмой выход которого соединен с входом регистра и вторым г входом блока формирования команд задержек, третий и четвертый входы которого соединены соответственно с третьим выходом управления блока управления и третьим выходом распре- С© делителя. ггюаибй

2. Устройство по п.1, о т л и ч а ю щ е е с я тем, что блок форми. рования команд задержек содержит счетчик, два триггера, три элемента, Ф

И, причем первый выход блока соединен с информационным входом счетчика и первым входом первого элемента И, второй . ход которого соединен с вторым входом блока, третий вход которого соединен через второй элемент

И с первыми входами счетчика и пер-вого триггера, вторые входы которых

1030791 соединены с выходом второго триггера и через третий элемент И с третьим входом счетчика, выход которого соединен с первым входом второго триггера., второй вход которого че1

Изобретение относится к вычислительной технике и может быть исполь-" зовано для сопряжения эычислйтельной машины с абонентским пультом,, например дисплеем.

Известно устройство, содержащее блок ввода, блок управления, счетчи. ки, регистр сдвига, генератор, коммутаторы, блок синхронизации(1).

Недостатком устройства является значительный объем оборудования и сложность организации при решении задачи отображения.

Наиболее близким к изобретению по технической сущности является устройство, содержащее блок ввода, информационный и установочный входы которого являются входами устройства первый выход которого соединен с первым управляющим выходом блока ввода, второй управляющий выход которого соединен с первыми входами первого коммутатора, буферной памяти и блока управления, первый и второй выходы которого соединены с тактовыми входами блока ввода, первый информационный выход которого соединен с вторым входом первого коммутатора, выход которого соединен с первым входом второго коммутатора, выход которого соединен с вторым входом буферной памяти, третий вход которой соединен с вторым информационным входом блока ввода, генератор, выход которого соединен с вторым управляющим входом блока управления и первым входом регистра сдвига, выход которого через сумматор соединен с вторым выходом устройства, второй вход регистра сдвига соединен с третьим выходом блока управления, входом распределителя и первым входом первого счетчика, выход которого соединен с четвертым выходом блока управления, и вторым входом первого счетчика, первый, второй и третий выходы распределителя соединены со-. ответственно с входом сумматора, первым входом второго счетчика и третьим входом блока управления, пятый и третий выходы которого соединены соответственно с третьим входом nephoro коммутатора и вторым входом второго счетчика, выход кото рого соединен с четвертым входом рез первый элемент И соединен с чет» вертим входом блока н входом второго элемента И, выход первого триггера соединен с выходом блока и входом третьего элемента И.

2 первого коммутатора, шестой и седьмой выходы блока управления соединены с четвертым и пятым входами буферной памяти f2).

5 Недостатком известного устройства является требование большого объема буферной памяти, что усложняет устройство и снижает его эффективность. .Целью изобретения является упро® щение устройства и повышение коэффициента использования оборудования.

Поставленная цель достигается тем, что в устройство, содержащее блок ввода, информационный и установочный входы которого являются входами устройства, первый выход которого соединен с первым управляющим выходом блока ввода, второй управляющий выход которого соединен с первыми входами первого коммутатора, буферной памяти и блока управления, первый и второй выходы которого соединены с тактовыми входами блока ввода, первый информационный выход которого соединен с вторым входом первого коммутатора, выход которого соединен с первым входом второго коммутатора, выход которого соединен с вторым входом буферной памяти, третий вход которой соединен с вторым

Зо информационным выходом блока ввода, генератор, выход которого соединен с вторым входом блока управления и первым входом регистра сдвига, выход которого через сумматор соединен с

35 вторьж выходом устройства, второй вход регистра сдвига соединен с третьим выходом блока управления, входом распределителя и перэм входом первого счетчика, выход которого

gg соединен с вторим входом второго коммутатора, третий вход которого соединен с четвертым выходом блока управления и вторым входом первого счетчика, первый, второй и третий выходы распределителя соединены соответственно с входом сумматора, пер вым входом второго счетчика и третьим входом блока управления, пятый и третий выходы которого соединены соответстэенно с третьим входом пер5О эого коммутатора и вторам входом второго счетчика, выход которого,соединен с четвертым входом перврго коммутатора, шестой и седьмой выходы

1030791 блока управления соединены с четвертым и пятым входами буферной памяти, введены блок формирования команд задержек и регистр, причем выход буферной памяти через регистр соединен с третьим входом регистра сдвига и первым входом блока формирования команд задержек, выход которого соединен с четвертым входом регистра сдвига и четвертьм входом блока управления, восьмой выход которого соеди- Ю нен с входом регистра и вторым входом блока формирования команд задержек,. третий и четвертый входы которого соединены соответственно с третьим выходом блока управления и третьим 15 выходом распределителя.

Кроме того, блок формирования команд задержек содержит счетчик, два триггера, три элемента И, причем первый выход блока соединен с инфор- 2О мационным входом счетчика и первым входом первого элемента И, второй вход которого соединен с вторым входом блока, третий вход которого соединен через второй элемент И с первыми входами счетчика и первого триггера, вторые входы которых соединены с выходом второго триггера и через третий элемент И с третьим входом счетчика, выход которого соединен с первым входом второго триггера, второй вход которого через первый элемент И соединен с.четвертым входом блока и входом второго элемента И, выход первого триггера соединен с выходом блока и входом третье- Зэ го элемента И.

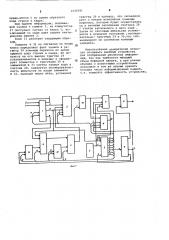

На фиг. 1 приведена блок-схема устройства; на фиг. 2 — структура блока ввода; на фиг. 3 и 4 - структуры блоков управления и формирова- Щ ния команд задержек.

Устройство содержит блок 1 ввода, блок 2 управления, буферную память

3, коммутаторы 4 и 5, распределитель

6, регистр 7 сдвига, генератор 8, сумматор 9„ регистр 10, блок 11 формирования команд задержек, счетчики 12 и 13.

Блок 1 содержит регистр 14, триггеры 15 и 16, дешифраторы 17 и 18, © элементы И 19, ИЛИ 20, счетчик 21, коммутатор 22.

Блок 2 содержит делитель 23 частоты, триггеры 24 и 25, коммутаторы

26 и 27.

Блок 11 содержит счетчик 28, триг- геры 29 и 30, элементы И 31-33.

Устройство работает следующим образом.

Блок 1 под управлением блока 2 обеспечивает ввод информации от ЭВИ Ю в буферную память 3 по адресу, определяемому кодом на выходе блока 1.

Основной тактовый ю пульс от блока

2 поступает на распределитель 6, вырабатывающий последовательность щ строчных и кадровых синхросигналов в телевизионном стандарте, а также сигнал начала кадра. Информация с буферной памяти Э передается в регистр 10, откуда поступает в регистр

7 сдвига и блок 11, и если считанный код не является командой переноса, то его передача в регистр 7 разрешается. B случае поступления команд переноса запись кода в регистр 7 запрещена, а под управлением сигналов блока 2 и распределителя 6 будет сформирована задержха в тактировании блоком 2 памяти 3, пронорциоиальная численному значению кода команды переноса. При этом обнуляется регистр 7. Чтение кодовых слов из памяти 3 осуществляется под управлением счетчика 13, который устанавливается в ноль под действием кадрового гасящего импульса с распределителя 6, а заполняется счетчик 13 импульсами с блока 2. Коммутатор 4 под.— ключается к блоку 1 только во время приема им кодовых слов. Поэтому для регенерации информации в памяти 3 используется счетчик 12 и коммутатор

5. Информация с регистра 7 передается в сумматор, где накапливается и затем передается на средства отображения.

Елок 1 работает следующим образом.

При записи в регистр 14 кодового слова на триггер 15 подается логическая единица, и по тактовому импульсу от блока 2 он вырабатывает сигнал на дешиФрацию команд, подготавливая триггер 16 и дешифратор 17.

Если принятый код относится к группе незаноминаемых команд, то на выходе элемента ИЛИ вырабатывается сигнал установки регистра 14 в исходное состояние. В процессе выработки этого сигнала осуществляется дешифрация команд дешифратором 18, который вырабатывает сигналы трех типов на счетчик 21 через коммутатор 22;

Триггер 16 при записи неэапоминаемых команд не переключается. При записи запоминаемых команд сигнал установки в исходное состояния на выходе элемента ИЛИ 20 вырабатывается только после прохождения цнкла записи, что обеспечивается переключением триггера 16 и срабатыванием элемента Н 19 по сигналу с блока 2.

Блок 2 работает следующим образом

Делитель 23 делит частоту юспульсов с генератора 8 и формирует новую последовательность импульсов, которая с помощью триггеров 24 и 25 и коммутатора 26 передается на различные выходы блока. При этом во время действия команд переноса сигнал от блока 11 и триггери 24 и 25 удерживается в единичном состоянии при помощи коммутатора 27. Такое же действие оказывает сигнал с выхода рас1030791 прЕделителя 6 во время обратного хода строки и кадра.

При приеме информации, подлежащей записи в память 3, на коммутатор

27 поступает сигнал от блока 1, исключающий на один цикл запрет тактирования памяти 3.

Блок 11 работает следующим образом.

Элемент И 31 по сигналам на входе блока определяет факт записи в регистр 10 команды переноса во время прямого хода строки и кадра. По импульсу на его выходе триггер 29 устанавливается в единицу и сформирует совместно с триггером 30 и элементом И 33 сигнал записи кода в счетчик 28. Сдвинутая последовательность импульсов на входе элемента

И 32, проходя через неГо, установит триггер 30 в единицу, что сигнализирует о начале исполнения команды переноса, которая будет осуществлять. ся в течение заполнения счетчика 28 с учетом записанного в него кода

Затем по тактовым импульсам установятся в исходное состояние (последовательно) триггеры 29 и 30,что сигнализирует об окончании команды задержки.

1О

Использование изобретения позволит создавать дешевые устройства для отображения различной информации, так как требуется меньший объем буферной памяти, а при равных объемах с известными устройствами позволяет в том же объеме хранить большее число информационных кадров, т.е. повысить эффективность устройства.

1030791

1030791

Составитель Р. Лачинов

Редактор О.Юрковецкая Техред 4,Тепер КорректоР Т. Митров ич

Заказ 5213/48 Тираж 706 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретении и открытий

113035, Яосква, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г, ужгород. ул. Проектная, 4