Устройство для геометрических преобразований изображений объектов

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО ДЛЯ ГЕОМЕТРИЧЕСКИХ ПРЕОБРАЗОВАНИЙ ИЗОБРАЖЕНИЙ ОБЪЕКТОВ, содержащее распределитель импульсов, соединенный с блоком памяти , с арифметическим блоком, подключенным к блоку памяти, и с регистром , другие входы которого соединены с шифратором и с блокс 4 памяти , а выход подключен к дешифратору и к блоку памяти, отличаю11цее с я тем, что, с целью повьшенйя быстродействия устройства оно содержит матрицу логических узлов, входы которых соединены с распределителем импульсов и с дешифраторе, а выходы подключены к шифратору. i 00 О. 00

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ РЕСПУБЛИК

Э(Я) G 06 К 9/36

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3427464/18-24 (22) 15.04.82 (46) 23 ° 07.83. Бюл. 9 27 (72) С.И.Хмельник Г.М.Аронов и М.И.Хмельник (71) Ордена Октябрьской Революции всесоюзный государственный проектноиэыскательский и научно-исследовательский институт "Энергосетьпроект" (53) 681.327.12(088 8) ! (56) 1. Патент CUR 9 3967243, кл. 340-146.3, опублик. 1976.

2. Патент CttlA 9 4021777, кл. 340-146.3, опублик. 1977.(прототип).

„„SU„„1030816 A (54)(57)1 УСТРОЙСТВО ДЛЯ ГЕОМЕТРИЧЕСКИХ ПРЕОБРАЗОВАНИЙ ИЗОБРАЖЕНИЙ

ОБЪЕКТОВ, содержащее распределитель импульсов, соединенный с блоком памяти, с арифметическим блоком, подключенным к блоку памяти, и с регистром, другие входы которого соединены с шифратором и,с блоком памяти, а выход подключен к дешифратору и к блоку памяти, о т л и ч а ю щ ее с я тем, что, с целью повьааения быстродействия устройства, оно содержит матрицу логических узлов, входы которых соединены с распределителем импульсов и с дешифратором, а выходы подключены к шифратору.

1030816

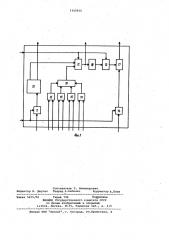

2.. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что, каждый логический узел матрицы содержит группу элементов И, входы которых являются первой группой входов логического узла, а выходы соединены с входом первого элемента ИЛИ, и последовательно подключенные первый элемент И, входы которого являются второй группой входов логического узла, триггер, один выход которого является первым выходом логического узла, второй элемент И, второй вход которого соединен с выходом первого

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам для преобразования изображений объектов.

Известно устройство для преобразования изсбражений объектов, содержащее блок считывания, соединенный с блоком памяти, подключенным к вычислительному блоку, логический блок, блок управления и элементы

И и ИЛИ (1).

Однако такое устройство имеет недостаточно высокую точность.

Наиболее близким к изобретению является устройство для преобразования изображений объектов, содержащее распределитель импульсов, соединенный с блоком памяти, арифметическим блоком и с регистром, шифратор,соединенный с регистром, дешифратор, логический блок, подключенный к распределителю импульсов 2 °

Недостаток известного устройства недостаточно высокое быстродействие.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство, содержащее распределитель импульсов, соединенный с блоком памяти, с арифметическим блоком, подключенным к блоку памяти, и с регистром, другие входы которого соединены с шифратором и с блоком памяти, а выход подключен к дешифратору и блоку памяти, введена матрица логических узлов, входы которых соединены с распределителем импульсов и дешифратором, а выходы подключены к шифратору. Причем каждый логический узел содержит группу элементов

И, входы которых являются первой . группой входов логического узла, а выходы соединены с входом первого элемента ИЛИ, и последовательно подключенные первый элемент И, входы которого являются второй группой элемента ИЛИ, третий вход является первым входом логического узла, а выход является вторым выходом логического узла, элемент НЕ, третий элемент И, другой вход которого является первым входом логического узла, и второй элемент ИЛИ, другой вход которого соединен с выходом четвертого элемента И, входы которого являются третьей группой входов логического узла, а выход второго элемента ИЛИ является третьим выходом логического узла. входов логического узла, триггер, один выход которого является первым зходом логического узла, второй элемент И, второй вход которого сое5 динен с выходом первого элемента

ИЛИ, третий вход является первым входом логического узла, а выход является вторым выходом логического узла; элемент НЕ, третий элемент И, fp другой вход которого является первым

)зходом логического узла, и второй элемент ИЛИ, другой вход которого соединен с выходом четвертого элемента И, входы которого являются треть15 ей группой входов. логического узла, а выход второго элемента ИЛИ является третьим выходом логического узла.

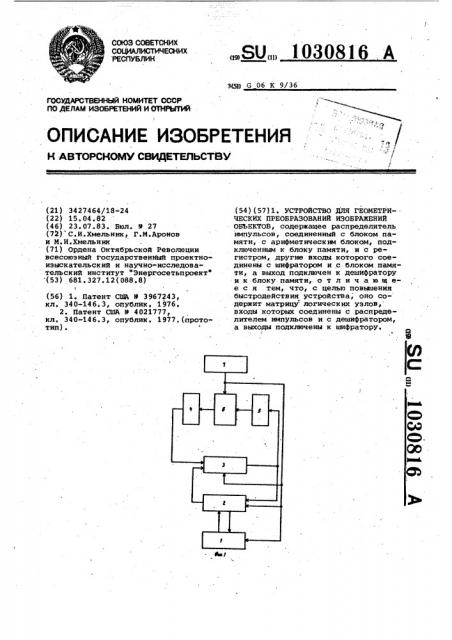

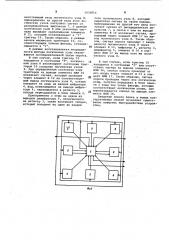

На фиг. 1 представлена блок-схема устройства; на фиг. 2 и 3 — конструктивное выполнение блока восстановления непрерывности геометрических фигур.

Устройство содержит арифметический блок 1, блок 2 памяти, регистр 3, шифратор 4, дешифратор 5, блок б восстановления непрерывности геометрических фигур и распределитель 7 импульсов.

При этом блок б содержит матрицу логических узлов 8 и 9 (фиг, 2), З0 включающих триггер 10, первый 11, :второй 12, третий 13 и четвертый 14 элементы Й, группу 15 элементов И, C первый 16 и второй 17 элементы ИЛИ и элемент НЕ 18.

Устройство работает следующим образом.

В блоке 2 хранится множество кодов точек фигуры, а все триггеры 10 блока б находятся в состоянии "0".

40 В режиме записи код каждой точки передается из блока 2 в регистр 3.

Дешифратор 5, нагруженный на этот регистр, вырабатывает на одном из своих выходов сигнал, который посту45 пает в блок б, где попадает на соот1030816 ветствующий вход логического узла 8.

Одновременно на другой вход всех ло-. гических узлов поступает сигнал от распределителя ычпульсов 7. В данном логическом узле 8 оба указанных сигнала вызывают срабатывание элемента

И 11, который устанавливает в "1" триггер 10. Таким образом, в режиме записи множество триггеров 10, соответствующих точкам фигуры, устанавливается в "1" ° !О

В режиме восстановления непрерывности фигуры логические узлы связываются последовательной цепью опроса.

В том случае, если триггер 10 находится в состоянии "0", логичес- j5 кий узел 8 анализирует состояние триггеров 10 соседних логических узлов

9. При определенном состоянии этих триггеров на выходе элемента ИЛИ 16 возникает сигнал, который проходит через элемент .И 12 на соответствующий выход логического узла 8, откуда попадает на один из входов шифратора

4. Ход,появляющийся на выходе шифра- тора 4, записывается в регистр 3, откуда пересылается.в блок памяти 2.

Одновременно с этим на одном из выходов дешифратора 5, нагруженного на регистр 3, также возникает сигнал, который попадает на один из входов того логического узла 8, который выработал сигнал на своем выходе.

Одновременно на другой его вход поступает сигнал.ат распределителя импульсов 7, в связи с чем на выходе элемента И 14 .возникает сигнал, проходящий через элемент ИЛИ 17 на выход логического узла 8. Таким образом, сигнал опроса проходит с входа данного логического узла 8 через элемент И 12, шифратор 4, регистр 3, дешифратор 5, элемент И 14 и элемент ИЛИ 17 на выход того же логического узла 8.

В том случае, если триггер 10, находится в состоянии "1" или отсутствует сигнал на выходе элемента

ИЛИ 16, сигнал опроса проходит от его входа через элемент И 13 и элемент ИЛИ 17. Таким образом, сигнал опроса проходит через все логические узлы, попутно передавая в блок памяти 2 коды тех точек фигуры, .которые соответствуют логическим узлам, где вырабатывается сигнал на выходе элемента ИЛИ 16.

Введение нового блока и новых кон,структивных связей позволяет существенно повысить быстродействие устройства.

1030816

Составитель Т. Ничипорович, Редактор Н, Джуган Техред А.Бабинец Корректор д.Повн

Заказ 5215/50 . Тираж 706 Подписное, ВНИИПИ Пэсударственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

ФЮ В

Филиал ППП "Патент", r. ужгород, ул.Проектная, 4