Система передачи информации

Иллюстрации

Показать всеРеферат

СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ по авт. св. № 788420, о т л и ч а ющ g я с я тем, что, с целью уменьшения времени занятости канала на передачу синхросигналов, в нее введены последовательно соединенные вычислительный блок, блокформирования периода синхронизации, блок памяти и элемент ИЛИ, к второму входу которого и к первому входу вычислительного блока подключен выход вычи тающего блока, при этом выход элемента ИЛИ подключен к входу дополнительного блока формирования синхросигнала , второй выход которого подключен к второму входу блока формирования периода синхронизации, а пер;вый выход дополнительного блока формирования синхросигнала подключен к второму входу вычислительного блока, к третьему входу которого подключен второй выход блока памяти. СО с 00 о со 00 00 0Ut.1 18 pLf 17

СОЮЗ СОВЕТСНИХ

СОЦИАЛИС1"ИЧЕСНИ)(РЕСПУБЛИК ае св

3(5п Н 04 1 17/00; Н 04 Х 7/430

ОПИСАН Е ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛА 4 ИЗО НИЙ V ОТН) ЫТИЙ (61) 788420 (21) 3346665/18-09 (22) 13.10.81 (46) 23.07.83. Бюл. Р 27 (72) П.П. Богданов, В.В. Головко и В.И. Емельянов (53) 621.394.662(088.8) (56) 1. Авторское свидетельство СССР

Р 788420, кл. Н 04 L 17/00, H 04 L 7/00, 1980 (прототип)., (54)(57) СИС1ЕИА ПЕРЕДАЧИ ИНФОРИАЦИИ по авт..св. Р 788420, о т л и ч а ющ а я с я тем, что, с целью уменьшения времени занятости канала на передачу синхросигналов, в нее введены последовательно соединенные вычислительный блок, блок формирования периода синхронизации, блок памяти и элемент ИЛИ, к второму входу которого и к первому входу вычислительного блока подключен выход вычи тающего блока, при этом выход элемента ИЛИ подключен к входу дополнительного блока формирования синхросигнала, второй выход которого подключен к второму входу блока формирования периода синхронизации, а первый выход дополнительного блока формирования синхросигнала подключен к, второму входу вычислительного блока, к третьему входу которого подключен второй выход блока памяти.

С2

1030988

Изобретение относится к радиотех- нике, может использоваться для передачи сигналов синхронизации совместно с информационными сообщениями в системах навигации, связи, управления движением объектов.

По основному авт. св. Р 788420 известна система передачи информации, содержащая на передающей стороне блок . формирования синхросигнала, последовательно соединенные блок формирова- 10 ния информационного сигнала, смеситель и блок передачи группового сигнала, а также коммутатор, сигнальный вход которого соединен с выходом блока формирования синхросигнала, вы- 5 ход соединен с вторым входом смесителя, выход блока передачи группового сигнала через прямой канал связи подключен на приемной стороне к объединенным входам блока декодирования информационного сигнала и блока выделения синхросигнала, на приемной стороне система содержит также два блока .измерения рассогласования и последовательно соединенные вычитающий блок 25 дополнительный блок формирования синхросигнала и передатчик синхросигнала. К первым входам блоков измерения рассогласования подключены соответствующие выходы блока выделения синхросигнала, выходы блоков измерения рассогласования соединены с соответствующими входами вычитающего блока,,а выход дополнительного блока формирования синхросигнала соединен с вторыми входами блоков из- 35

) мерения рассогласования.

Выход передатчика синхросигнала через обратный канал связи подключен на передающей стороне к управляющему входу коммутатора и третьему входу40 смесителя 1)..

Однако известная система характеризуется большим временем занятости канала связи на передачу синхросигналов из-за необходимости проведения 45 сеансов контрольных измерений расхождения фаз синхросигнала.

Цель изобретения — уменьшение времени занятости канала связи на нередачу синхросигналов.

Для этого систему передачи инфор-, мации, содержащую на передающей стороне блок формирования синхросигнала и последовательно соединенные блок

Формирования. информационного сигнала, сМеситель и блок передачи группового 55 сигнала, выход которого подключен к вхсЩу прямого канала связи, и на приемной стороне - объединенные по входу блок декодирования информационного сигнала и блок выделения 60 сннхроснгнала, и подключенные к выходу прямого канала связи, а также передатчик синхросигнала по обратному каналу связи, кроме того на передающей стороне система содержит ком- 65 мутатор, к сигнальному входу которого подключен выход блока формирования синхросигнала, а выход коммутатора подключен к другому входу смесителя, к третьему входу которого и к управляющему входу коммутатора подключен выход обратного канала связи, а на приемной стороне — два блока измерения рассогласования и последовательно соединенные вычитающий блок и дополнительный блок формирования синхросигнала, при этом выход блока выделения- синхросигнала через первый и второй блоки измерения рассогласования подключены к соответствующим входам вычитающего блока, а выход до. полнительного блока формирования синхросигнала подключен к входу передатчика синхросигнала по обратному каналу связи и к другим входам первого и второго блоков измерения рас- . согласования, введены последовательно соединенные вычислительный блок, блок формирования периода синхронизации, блок памяти и элемент ИЛИ, к второму входу которого и к первому входу вычислительного блока подключен выход вычитающего блока, при этом выход элемента ИЛИ подключен к входу дополнительного блока формирования синхросигнала, второй выход которого подключен к второму входу блока формирования периода синхронизации, а первый выход дополнительного блока формирования синхросигнала подключен к второму входу вычислительного блока, к третьему входу которого подклю чен второй выход блока памяти.

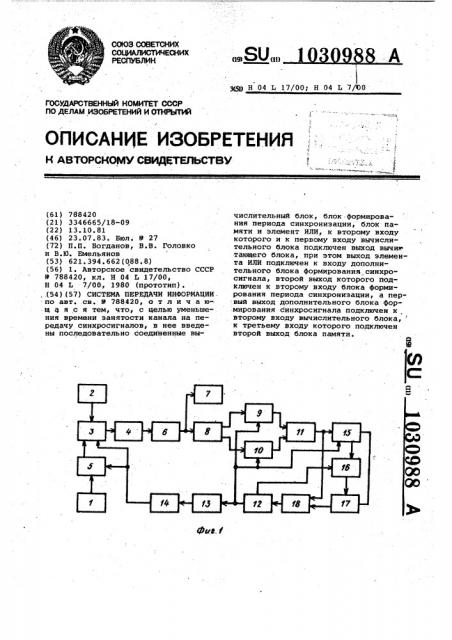

На фиг. 1 представлена структурная схема предлагаемой системы передачи информации; на фиг. 2 - временные диаграммы функционирования системы при передаче синхросигналов.

Система передачи. информации содержит на передающей стороне блок 1 формирования синхросигнала, блок 2 формирования информационного сигнала, смеситель 3, блок 4 передачи группового сигнала, коммутатор 5, прямой канал б связи, блок 7 декоди рования информационного сигнала, блок 8 выделения синхросигнала, на приемной стороне — два блока 9 и 10 измерения рассогласования, вычитающий блок 11 дополнительный блок 12 формирования синхросигнала, передатчик

13 синхросигнала, обратный канал 14 связи, вычислительный блок 15, блок

16 формирования периода синхронизации, блок 17 памяти элемент ИЛИ 18.

Система работает следующим образом.

На приемной и передающей сторонах в блоках 1 и 12 формирования синхросигнала от сигналов задающих генераторов формируется ряд синхросигна« лов, необходимых для работы системы, в том числе, например, сигналы с

1030988 периодом Т «. Непосредственно после передается сигнал от приемной сторо включения аппаратуры системы в рабо- ны. Длительность интервала Т опредету между этими послвдовательностями ляется предварительно на основании синхросигналов может быть произволь априорных данных о характеристиках ный сдвиг по фазе N (фиг. 2g,Д). задающих генераторов в блоках 1 и 12 . Для начальной синхрснизации при- = 5 Формирования синхросигнала на пере емной и передающей сторон сигнал с,дающей и приемной сторонах с помощью выхода дополнительного блока 12 фори мкрования синхросигнала через пера- выражения Т= Г /(- †) где Г

/ « датчик 13 синхросигнала iй(и обРатный otl

ДОЛ канал 14 связи от приемной стороны .- 10 д У е з ачение РасхождениЯ Фаз передается на п реда сторону, синхросигналов на передающей и приемгде .поступает с задержкой 2 1, вызван- ной сторонах в cHCTeMet-(†) - -нпркь д+ «f ной временем распространения сигна- о н, P рное значение относительной разностий вход смесителя 3 и одновременно 15 тЦ«ч «стот генеРатоРов. После повзона „равляющий вход ко „утатора 5 Рени . тех операЦий1 что и ПРи началь разрешая прохождение сигнала с выной сйнхронизации сто он в в итхода блока 1 Формирования синхросигющем блоке 11 пол ается нала на второй вход смесителя 3. С чение расхождения фаэ синхросигналов выхода смесителя 3 оба синхросигнала 20 фиг. 22) в составе группового снг- 20 тельном блоке 12 фоРмиРованиЯ синнала блока 4 передачи по прямому каналу 6 связи поступают с задержкой «: последовательности сикх осигналов на вход блока 8 выделениЯ синхросиг- ный блок

4 этот сигнал поступает в вычислительнала на приемной стороне (фиг. 2д) .

Первый из выделенных синхросигнапов та в мен

25 значение С а так же значение моменпост ает на п рвый в од и рвого та времени проведения синхронизац блока 9 измерения рассогласования, Посл >Toto в на второй - на первый вход второго

После этого в вычислительном бло»

6JTQKB 10 H3bfGpBHHH Расс гласования

ЗО относительной разности частот генена вторые входы которых подается так-"" же сигнал с выхода дополнительного раторов блоков формирования синх ф р ро ания синхроблока 12 формирования синхросигнала игналов -, / =(Ч -«, ) (Q-4к) и зна

1 1 на приемной стороне. Полученные в Г /р H к. блоках 9 и 10 измерения рассогласова- кн н у синхронизации пРиемной стороны

= Г и -- . Полученное значение трепередаются в вычитающий блок 11> где буемого периода синхронизации T c выхода вычислительного блока 15 пония фаз синхросигналов на приемной дается на управляющий вход блока 16 и передающей сторонах б = б — 6 /д=,",, О "формирования периода синхронизации, (Фиг. 2з). Этот сигнал через элемент на сигнальный вход которого поступаИЛИ 18 подается на управляющий вход ет сигнал с другого выхода допоаяидополнительного блока 12 формирова- «тельного блока 12 формирования синния синхросигнала, где производится хросигнала. Сформированный в блоке 16 д ф р руемой последовательности 5 формирования периода. синхронизации сигналов на величину, после чего фазы синхросигналов на перед щей-к сигнал Тб а™ даетсЯ на вход бло. приемной сторонах совпдают.,ка 17 " lRTt i в КОтором предварить.. но записано значение допустимого рас-

Одновременно сигнал с выхода вы-. хождения Фаз синхросигнала Ю раз-

*оп i читающего блока 11 поступает в вы- решая прохождение хранимой в нем инчислительный блок 15„ где регистрк- формации (значения « ) через эле«щп

° ðóeTcÿ в виде значения начального : мент ИЛИ 18 на управляющий вход дорасхождения фаз сигналов Гн 0 (не- полнительного блока 12 формирования зависимо от величины сигнала). Зна- скнхросигнала. Поскольку значение чение момента времени проведения допустимого расхождения Фаз синхроначальной синхронизации приемной к сигналов дои хранитсЯ в блоке 17 папередающей сторон Ч,н также регистрк- мяти в течение всего времени работы .Руется в вычислительном блоке 15 по - потребителя системы (приемной сторосигналу с выхода дополнительного бло- ны), то прк поступлении каждого очека 12 формирования синхросигнала. 60 Редного сигнала с выхода блока 16

Через интервал времени Т с выхода, формиронания периода синхронизации дополнительного блока 12 формирова- в дополнительном блоке 12 формирования синхросигнала через передатчик ния скнхроскгнала осуществляется

13 синхросигнала и обратный канал 14 сдвиг формируемой последовательсвязи на передающую сторону опять 6 ностй сигналов, к расхождение фаз

1030988

Составитель С. Осмоловский

Редакто1 A. Шишкина .ТехредМ.Тенер Корректор A Тяско

Тираж 677 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 5235/58

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 синхросигналов на приемной и переда ющей сторонах все время выдерживается в заданных пределах.

Использование двух отдельных блоков 9 и 10 измерения рассогласования на приемной стороне позволяет применить в их качестве простейшие счетчики временных интервалов. Вычитающий блок 11 представляет собой .,арифметическое устройство, производящее единичную операцию над двумя 10 числами. Вычислительный блок 15 является арифметически-логическим устройством, обеспечивающим выполнение основных операцийг причем чисел (значений расхождения фаз, моментов вре- 15 мени, а также величиныЧ:доп ); обну" ление числа, соответствующего первому из поступивших значений расхождения фаэ; арифметические операции над числами выдача результатов вычислений.

Вычитающий блок 11 и вычислительный блок 15 легко реализуются на стандартных элементах цифровой техники в виде отдельных устройств или могут быть объединены на основе единого микропроцессорного устройства.

Блок 16 формирования периода синхронизации может быть выполнен на основе делителя с переменныч коэффициентом деления, например счетчика с начальной установкой кода. Блок 17 памяти также может быть выполнен в различных вариантах, например на основе регистра сдвига, или являться состав- ной частью микропроцессорного устройства.

Таким образом, в системе передачи информации передача синхросигнала по радиоканалу только два раза в начальный период работы потребителя (приемной стороны), за счет чего увеличивается автономность работы потребителя и практически полностью исключается занятость каналов на пеI редачу сигналов синхронизации.