Цифровой частотный демодулятор

Иллюстрации

Показать всеРеферат

1. ЦИФРОВОЙ ЧАСТОТНЫЙ ДЕМОДУЛЯТОР , содержащий выходной триггер и последовательно соединенные усилите ль -6 граничите ль и блок вЁаделения нуль-переходов сигнала, к второму входу которого подключен выход формирователя Тактовых импульсов, о тл ичающийся тем, что, с целью повышения помехоустойчивости, в негчэ введены распределитель импульсов и последовательно соединенные блок формирования цифрового сигнала, блок памяти и вы 1ислительный блок, выход которого подключен к первому входу выходного триггера, при этом дополнительные выходы формирователя тактовых импульсов соединены с пе1рвым входом блока формирования цифрового сигнала, второй вход которого соединей с выходом блока выделения нульпереходов сигнала и с входом распре:делителя импульсов, выходы которого подключены к вторьм входгкм блока паг мяти, вычислительного блокаи выходного триггера. . 2.Устройство по п. 1, о т л и чающееся , тем, что.блок формирования цифрового сигнала состоит из последовательно соединенных измерительногчэ счетчика и элемента бу:фернОЙ памяти, выход которого является выходом блока формирования цифрового сигнала, входами которого являются входы измерительного счетчика один из которых соединен с вторалм входом элемента буферной памяти. 3,Устройство по п. 1, о т л и ч: ai ю щ е ее я тем, что блок формирования цифрового сигнала состоит из последовательно соединенных измерительного , счетчика, регистра к интерполятора , выход которого является выходом блока формирования цифрового О сигнала, входами которого являются входы измерительного счетчика, один 00 о из которых соединен с вторым входом ;регистра.. :О :0

(19) 01) СОЛВВЮ Н

РЕСПУБЛИК

95)) H 04 Ь 27 14

1 в ;„л

М ABTOPCHQNV СВИДЕТЕЛЬСТВУ

ГАСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21). 3348565/18-09 (22) 21.10.81 (46) 23.07.83. Бюл. М 27 (72) Ю.Г. Бурейшин, В.Б. Малинкин, П.Г. Фрнцлер и В.П. Шувалов (7l.) Новосибирский электротехнический институт связи нм. Н.Д. Псурцева (53) 621.394.62(088.8) (56) 1. Патент CUR 9 3908169, кл. 325-320, 1975.

2. Шляпоберский В.И. Основы техники передачи дискретных сообщений. М., Связь, 1973, с. 213 (прототип) ° (54)(57) 1. ЦИФРОВОЙ ЧАСТОТНЫЙ ДЕМОДУЛЯТОР, содержащий выходной триггер и последовательно соединенные усилитель-ограничитель н блок вЫделения нуль-переходов сигнала, к второму входу которого подключен выход формирователя тактовых импульсов, о т л ич а ю шийся тем, что, с целью повышения помехоустойчивости, в него введены распределитель импульсов и последовательно соединенные блок фор" мирования цифрового сигнала, блок памяти и вычислительный блок, выход которого .подключен к первому входу выходного триггера, при этом дополнительные выходы формирователя так- товых импульсов соединены с первым входом блока формирования цифрового сигнала, второй вход которого соединен с выходом блока выделения нульпереходов сигнала и с входом распределителя импульсов, выходы которого подключены к вторьы входам блока па-. мяти, вычислительного блока- н выходного триггера.

2. Устройство по п. 1, о т л ич а ю щ е е с я.тем, что.блок формирования цифрового сигнала состоит из последовательно соединенных из. мерительного счетчика и элемента бу.ферной памяти, выход которого является выходом блока формирования циф рового сигнала, входами которого являются входы измерительного счетчика,а один из которых соединен с вторым входом элемента .буферной памяти.

3. Устройство. по и. 1, о т л ич а ю щ е е с я тем, что блок .формирования цифрового сигнала состоит из последовательно соединенных .измери- ф . тельного счетчика, регистра и интерполятора, выход которого является выходом блока формирования цифрового сигнала, входами которого являются входы измерительного счетчика, один .из которых соединен с вторым входом

:регистра.

1030991 но соединенных измерительного счет- „

Изобретение .относится к техник передачи данных и может использоваться s устройствах преобразования сигналов с частотной модуляцией.

Известен частотный демодулятор, конструктивно выполненный в виде измерительного счетчика, входы которого соединены с блоком выделения нуль« переходов частотно-модулированного

I (ЧМ) сигнала и задающим .генератором, а выходы соединены с блоками йоследующей обработки и классификации 1,).

Однако частотный демодулятор имеет недостаточную помехоустойчивость вследствие малой величины разности длительностей полупериодов характеристических частот.

Наиболее близким техническим решением к изобретению является цифровой частотный демодулятор, содержащий выходной триггер и последователь-29 но соединенные усилитель-ограничитель и блок выделения нуль-переходов сигнала, к второму входу которого подключен выход формирователя тактовых импульсов f2). 25

Однако известный цифровой частотный демодулятор имеет низкую помехоустойчивость.

Цель изобретения - повышение помехоустойчивости. 30

Для этого в цифровой частотный де. модулятор, содержащий выходной триггер и последовательно соединенные усилитель-ограничитель и блок выделения нуль-переходов сигнала к втоI

35 рому входу которого подключен выход формирователя тактовых импульсов, введены распределитель импульсов и последовательно соединенные блок формирования цифрового сигнала, блок памяти и вычислительный блок, выход 40 которого подключен к первому входу выходного триггера, при этом дополнительные выходы формирователя так. товых импульсов соединены с первым входом блока формирования цифрового 45 сигнала, второй вход которого соединен с выходом блока выделения нульпереходов сигнала и с входом распре..делителя импульсов, выходы которого .подключены к вторым входам блока па- 5(} мяти, вычислительного блока и выход-1 ного триггера.

При этом блок формирования цифрового сигнала состоит из последовательно соединенных измерительного счет чика и элемента буферной памяти, выход которого является выходом блока

Формирования цифрового сигнала, входами которого являются входы измери тельного счетчика, один из которых 60 соединен с вторым входом элемента буферной памяти.

Причем блок формирования цифрового сигнала состоит из последоватвльчика, регистра и интерполятора, выход которого является выходом блока формирования цифрового сигнала, входами которого являются входы измеритель ногоо счетчика, один из которых соединен с вторым входом регистра.

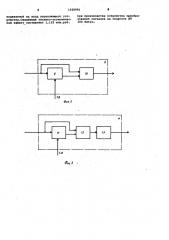

На фиг. 1 представлена структурная электрическая схема предложенного цифрового частотного демодулятора; на фиг. 2 и 3 — варианты выполнения блока формирования цифрового сигнала; на фиг. 4 — эпюры напряжений, поясняющие работу демодулятора.

Цифровой частотый демодулятор содержит усилитель-ограничитель 1. блок 2 выделения нуль-переходов сигнала, формирователь 3 тактовых импульсов, блок 4 формирования цифрового сигнала, блок 5 памяти, вычислительный блок 6, выходной триггер 7, распределитель 8 импульсов. Блок формирования цифрового сигнала в первом варианте исполнения (фиг. 2) состоит из измерительного счетчика 9 и элемента 10 буферной памяти. Блок формирования цифрового сигнала ва втором варианте исполнения (фиг. 3) состоит из измерительного счетчика 11 регистра 12 и интерполятора 13.

Цифровой частотный демодулятор работает следующим образом.

Принятый ЧМ-сигнал (фиг. 46) с выхода полосового фильтра (не показан) поступает на усилитель-ограничитель 1, который преобразует входной сигнал и последовательность прямо» угольных импульсов переменной длитель. ности (фиг. 45). Блок 2 выделения нуль-переходов сигнала формирует в моменты пересечения входным сигналом нулевого уровня короткие импульсы. (фиг. 4Z) и подает их в блок 4. На фиг. 4д представлен характер изменения во времени чисел, формируемых на выходе блока 4 в случае, когда он выполнен в виде измерительного счетчика 9, соединенного с элементом 10 буферной памяти (фиг. 2). В этом случае измерительный счетчик подсчетом числа импульсов тактовой частоты на интервале полупериода формирует число, характеризующее значение частоты на данном полупериоде. Очередной импульс с блока 2 выделения нуль-переходов сигнала записывает полученное число в триггеры элемента 10 буферной памяти и устанавливает измерительный счетчик в исходное состояние.

Следующий импульс. нуль-.,перехода изменяет состояние элемента 10, т.е. число на выходе. блока 4 пропорционально входной частоте, и так с приходом каждого импульса блока 2 выделения нуль-переходов сигнала.

В случае, когда блок 4 выполнен в виде последовательно соединенных измерительного счетчика ll (фиг. 3), 1030991 регистра 12 и интерполятора 13, формирование чисел, пропорциональных входной-частоте, отличается от рассмотренного случая тем, что два или более-числа, характериэующих значения частоты на интервалах полупериодов, записывают из измерительного счетчи-. ка 11 в регистр 12, с которого указанные числа подают на интерполятор

13. Интерполятор, используя поданные на его вход значения чисел, рассчи- 10 тывает значения чисел в промежуточных . точках, что позволяет более точно воспроизвести закон изменения частоты на входе демодулятора. Этот случай пояснен на интервале Ту (фиг}4ф, l5 бронная линия). Поступающие с блока 2 . выделения нуль-переходов сигнала им" пульсы сдвигают числа в регистре 12, а интерполятор 13 формирует на выходе числа, характеризующие значения час- 20 тоты входного сигнала.

Блок 5 памяти периодически (с периодом To) производит: отсчеты чисел

И4 с выхода блока 4 и запоминает их.

Отсчеты чисел И„(фиг. 48) записывают в блок 5 таким образом, чтобы в нем всегда хранилось И+1 текущее значение частоты (числа И;) . Значения Тр

-и М определяют из соотношений

Из принципа работы демодулятора также следует, что он может быть реализован полностью на цифровых ин тегральных схемах. При смене харакI теристических частот демодулятор пе рестраивают изменением тактовой частоты, подаваемой на тактовый вход блока 4, пропорционально входной частоте. При изменении скорости передачи демодулятор. может быть перестроен на соответствующую длительность посылки изменением периода Т, т.е. изменением тактовой частоты, подаваемой на распределитель 8. Неточность получения значений указанных частот может быть скомпенсирована изменением числового значения порога. Отмеченi

: ная простота перестройки позволяет широко использовать предложенный демодулятор.

1+И

2, " „,.м к"к "no) }." 1=1-Х

Таким образом, положительный эффект заключается в том, что при ве-. роятности ошибки Р = 10, отношение

-4, сигнал/шум в предлагаемом устройства по.сравнению с известным уменьшилось на 12 дБ, величина краевых искажений уменьшилась на 8%, перестройка иэ одного режима работы в другой произ" водится изменением тактовой частоты, То B 100 Д } (1) 30 (И+1) Т0 = - (2)

1 где В - скорость передачи (Бод); д — допустимая величина кРаевых 35 искажений, Ъ.

Из соотношения (2) следует, что в блоке 5 хранятся текущие отсчеты значений частоты, взятые на временном интервале,: равном длительности едийичного элемента.

Вычислительный блок 6, управляемый сигналами с распределителя 8, периодически (с периодом ТО) рассчитывает сумму М+1 отсчета значений частоты и вычитает числовое значение порога. 45

Результаты расчета (фиг. 4Ж) определяются соотношением где значения коэффициентов С,(в частном случае для простоты устройства берут равными 1, тогда числовое значение порога и р- (М+1) Ис, причем

Ис — среднее арифметическое чисел, формируемых блоком 4 в случае верхней и нижней характериотических частот ЧМ сигнала.

Знак рассчитанного значения М Щ подают на выходной триггер 7,. который распределителем 8 переключается в одно из устойчивых состояний, характеризующих принятую позицию сигнала на 1-м интервале То (фиг. 4 ) .

Из рассмотрения принципа работы предложенного цифрового частотного демодулятора следует .что снимаемые с выхода выходного триггера восстановленные посылки могут по ллительности отличаться от переданных посылок на величину Тр которая может быть взята достаточно малой. Этим определяется малая величина краевых искажений предложенного демодулятора.

Сигнал, подаваемый с выхода полосового фильтра на вход уаилителяограничителя, подвержен воздействию помехи. Однако, в большинстве интересных для практики случаев, помеха, воздействуя на ЧИ сигнал на входе фильтра, приводит только к перераспределению длительностей полупериодов на его выходе, не изменяя существенно среднее значение частоты на интервале, равном длительности переходного процесса. В предложенном демодуляторе принятая позиция сигнала определяется на интервале каждого отсче та входной частоты как среднее эначе» ,ние отсчетов входной частоты, взятых

)на временном интервале, равном дли тельности единичного элемента (посылки}.1 ри этом полезная(информаци;онная)составляющая сигнала суммируат.

-ся линейно, а .отдельные составляющие помех усредняются, так как имеют

:различные знаки (суммируются слуЧайно). В результате увеличивается помехоустойчивость предложенного демодулятора.

1030991 подаваемой на вход управлякщего уст«, ройства.Ожидаемый технико-экономичес кий эффект составляет 1, 125 млн.руб. при проиэводстве устройства гщеобра ,зования сигналов на скорость до

300.,бит/с

1030991

St&) Sy(<) Редактор А. Шишкина

Составитель A. Москевич

Техред Т.Маточка Корректор М. Демчик

Заказ 5235/58 Тираж 677 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и.открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород ул. ПроеКтная, 4

Е (i)