Устройство для приема избыточной информации

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО ДЛЯ ПРИЕМА ИЗБЫТОЧНОЙ ИНФОРМАЦИИ, содержащее приемник, вход которого является входом устройства, выход приемника соединен с входом буферного блока памяти, первые выходы которого соединены с входами формирователя двоичных кодовых комбинаций единичного веса; второй выход через пороговый селектор - с входом двоичного регистра и непосредственно с первым входом блока сравнения, первый выход и второй вход которого соединены соответственно с первыми входом и выходом блока регистров памяти, вторые вход и выход блока регистров памяти соединены соответственно с выходом декодера и выходом устройства, о т личающеееся тем, что, с целью упрощения устройства, в него введены преобразователь информационных сигналов и элемент ИЛИ, выход которого соединен с входом декодера , выход двоичного регистра и выход формирователя двоичных кодовых комбинаций единичного веса соединены соответственно с информационным и управляющим входами преобразователя информационных сигналов, выходы которого соединены соответственно с первым и вторым входами элемента ИЛИ, третий выход которого подключен к i выходу порогового селектора. 2. Устройство по п. Г, а т л и W чающееся тем, что преобразователь информационных сигналов выполнен на триггере, ключах и инверторе , выходы триггера соединены с управляющими входами ключей, выход первого ключа через инвертор и выход второго ключа непосредственно ;ое- , динены соответственно с первым и со вторым входами преобразователя инфорtsD мационных сигналов, информационные 4 входы ключей и вход триггера соедине ны соответственно с информационным и управляющим входами преобразователя информационных сигналов. .

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУбЛИК

З(Я) G 08 С 19/28. ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

3»

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

l1O ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3416517/18-24 (22) 01.02.82 (46) 30.07.83. Бюл. 1г 28 (72) Ю.П. Зубков, А.М. Лягин, С.В.Науменко, В.Ф. Онищенко, A.Ï. Толстолуцкий, Ю.И. Бессараб, Н.С. Сакулин и А.С ° Смирнов (53) 621 ° 318 (088.8) (56) 1. Авторское свидетельство СССР

N 824263, кл, G 08 С 19/28, 1979.

2. Авторское свидетельство СССР по заявке и 3250882/18-24, кл. G 08 С 19/28, 1981(прототип). (54)(57) 1. УСТРОЙСТВО ДЛЯ ПРИЕМА

ИЗБЫТОЧНОЙ ИНФОРМАЦИИ, содержащее приемник, вход которого является входом устройства, выход приемника соединен с входом буферного блока памяти, первые выходы которого соединены с входами формирователя двоичных кодовых комбинаций единичного веса, второй выход через пороговый селектор - с входом двоичного регистра и непосредственно с первым входом блока сравнения, первый вы од и второй вход которого соединены соответственно с первыми входом и выходом блока регистров памяти, вторые вход и выход блока регистров памяти соединены соответственно с выходом

„„30„„1032470 4 декодера и выходом устройства, о т " л и ч а ю щ е е е с я тем, что, с целью упрощения устройства, в него введены преобразователь информационных сигналов и элемент ИЛИ, выход которого соединен с входом декодера, выход двоичного регистра и выход формирователя двоичных кодовых комбинаций единичного веса соединеHbl соответственно с информационным и управляющим входами преобразователя информационных сигналов, выходы которого соединены соответственно с первым и вторым входами элемента ИЛИ, третий выход которого подключен к выходу порогового селектора. а ф

2. Устройство по и. 1, о т л и ч а ю щ е е с я тем, что преобразователь информационных сигналов вы" полнен на триггере, ключах и инверторе, выходы триггера соединены с управляющими входами ключай, выход первого ключа через инвертор и выход р„а второго ключа непосредственно соединены соответственно с первым и вторым входами преобразователя информационных сигналов, информационные входы ключей и вход триггера соедине- ны соответственно с информационным и управляющим входами преобразователя информационных сигналов.

4 l032

Изобретение относится к электросвязи, а именно к приемным устройствам дискретных систем связи, использующих составные сигналы с избыточностью, формируемые на основе двоичных помехоустойчивых кодов.

Известно устройство для приема избыточной информации, содержащее приемник, пороговые селекторы, дека- щ дер, блоки буферной памяти, блоки регистров памяти, сумматор, блок вычитания, усилитель и блок управления выдачей информации Pf ) .

Достоинством этого устройства является возможность практической реализации оптимального приема в целом, I

Недостаток устройства - сильное

20 влияние параметров отдельных блоков устройства на качество приема избыточной информации.

Наиболее близким к предлагаемому по технической сущности является устройство для. приема дискретной информации, содержащее приемник информации, вход которого подключен к входу Устройства, выход - к входу буферного блока памяти, первый выход буферного блока памяти соединен с

ЗО

:первым входом блока управления выдачей информации и через пороговый селектор - с первым входом декодера и .входом первого блока регистра памяти, выход которого соединен с первым вхо-З5 дом сумматора по модулю два, выход декодера соединен с первым входом второго блока регистров памяти, первый выход и второй вход которого соединены соответственно с вторым входом 4О и выходом блока. управления выдачей информации, второй выход блока регистров соединен с выходом устройства, причем выход третьего блока регистров памяти соединен С вторым входом 5 декодера, вторые выходы буферного блока памяти соединены через решающий блок с вторыми входами сумматора по модулю два, выходы которого сое динены с входами третьего блока ре- 50 гистрав памяти (2 .

Известное устройство обеспечивает высокую помехоустойчивость приема составных сигналов с избыточностью„ так как реализует прием сигналов . 55 в целом, используя при этом только элементы дискретной техники. Оно поЭволяет обрабатывать сложные сигналы, формируемые на основе и недвоичных избыточных кодов.

Данное устройство реализует способ декодирования в целом по методу соседней зоны, характерной особенностью которого является формирование двух двоичных кодовых комбина" ций:первая определяет грубую оценку сложного избыточного сигнала, а вторая (единичного веса ) соответствует наиболее вероятному вектору ошибки. Операция исправления ошибок в известном устройстве заключается в параллельном поразрядном суммироваяии указанных двоичных кодовых комбинаций с помощью блока сумматоров по модулю два. Ее результат определяет вторую грубую оценку избыточного сигнала, которая запоминается во втором двоичном регистре.

В известном устройстве нерационально используются блок сумматоров по модулю два и второй двоичный регистр.

Наличие функционально пассивных блоков блока сумматоров по модулю два второго двоичного регистра обуславливает неоправданную сложность известного устройства, снижает его технологичность, экономичность и надежность функционирования, а в конечном счете и помехоустойчивость приема сигналов с избыточностью.

Цель изобретения - упрощение устройства путем исключения функционально пассивных блоков.

Указанная цель достигается тем, что в устройство для приема избыточной информации, содержащее приемник, вход которого является входом устройства, выход приемника соединен с входом буферного блока памяти, первые выходы которого соединены с входами формирователя двоичных кодовых комбинаций единичного веса, второй выход через пороговый селектор - с входом двоичного регистра и непосредственно с первым входом блока сравнения, первый выход и второй вход которого соединены соотг-ветственно с первым входом и выходом блока регистров памяти, вторые вход и выход блока регистров памяти соединены соответственно с выходом декодера и выходом устройства, введены преобразователь информационнь.х сигналов и элемент ИЛИ, выход которого соединен с входом декодера, выход двоичного

1032470 4 регистра и выход формирователя двоичных кодовых комбинаций единичного веса соединены соответственно с информационным и управляющим входами преобразователя информационных сигналов, выходы которого соединены соответственно с первым и вторым входами элемента HJlH третий выход которого подключен к выходу порогового селектора. !0

Кроме того, преобразователь информационных сигналов выполнен на триггере, ключах и инверторе, выходы триггера соединены с управляющими входами ключей, выход первого ключа через инвертор и выход второго ключа непосредственно соединены соответст венно с первым и вторым выходами преобразователя информационных сигналов, информационные входы ключей и вход триггера соединены соответствен-но с информационным и управляющим входами преобразователя информационных сигналов.

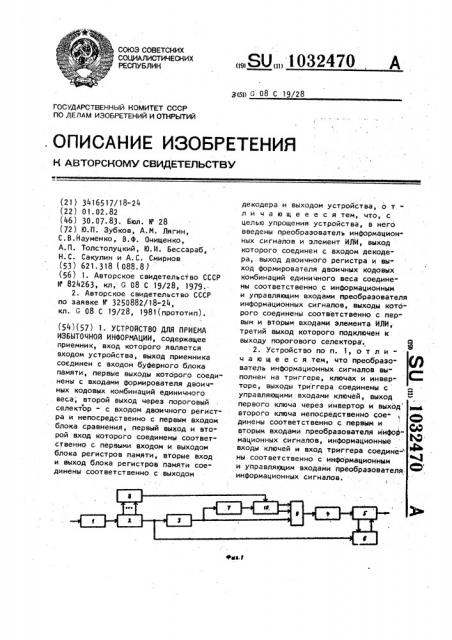

На фиг. 1 представлена структурная схема предлагаемого устройства на фиг. 2 - функциональная схема логического блока.

Устройство для приема избыточной информации содержит следующие блоки: приемник 1 (демодулятор ), осуществляющий преобразование входного составного сигнала с избыточностью в выходной аналоговый составной избыточный сигнал. Режим его функцио нирования определяется используемыми элементарными канальными сигналами (т.е. видом модуляции ) и способом их обработки (когерентный, некогерентный и т.д.);

40 буферный блок 2 памяти, в котором запоминается составной аналоговый сигнал с избыточностью. Считываться из данного блока укаэанный сигнал может многократно (с регенерацией ), пороговый селектор 3, представляющий собой нелинейный однопороговый блок, в котором величина порога определяется характеристиками. канала и выставляется оператором вручную, - декодер 4, отождествляющий входные двоичные кодовые комбинации полного безизбыточного кода с выходными разрешенными кодовыми комбинациями избыточного кода 55

- блок 5 регистров памяти, в котором запоминаются две разрешенные кодовые комбинации„ блок б сравнения. С его помощью определяется та из двух разрешенных кодовых комбинаций, хранящихся в блоке 5, которая в наибольшей степе" ни соответствует входному сигналу.

По команде из блока 6 в блок 5 двоичных регистров памяти выдает на выход устройства ту или другую разрешенную кодовую комбинацию (или ее информационные символы для разделимых кодов, или соответствующую комбинацию двоичного полного хода ); — двоичный регистр 7. В него за- писывается и хранится заданное время двоичная кодовая комбинация - первая грубая оценка избыточного сигнала! формирователь 8 двоичных кодовых комбинаций единичного веса, состоящий из генератора линейно изменяющегося напряжения, элементов Сравнения, элемента ИЛИ и двоичного регистра.

Данный формирователь определяет минимальный разностный сигнал. Его номер соответствует номеру единичного разряда выходной двоичной комбинации единичного веса; — элемент ИЛИ 9 служит для согласования выходов логического блока и порогового селектора с входом декодера; преобразователь 10 информационных сигналов, состоящий иэ ключей

11 и 12, триггера 13 и инвертора (элемент НЕ )!4, На его информационный вход последовательно подается двоичная кодовая комбинация - первая грубая оценка избыточного сигнала.

На его управляющий вход из формирователя 8 поступает двоичная комбинация единичного веса, причем синхронно с комбинацией по информационному входу. Для всех нулевых управляющих сигналов соответствующие информационные сигналы блока без изменения проходят на его выход. Единичный управ» лякнций сигнал изменяет соответствующий информационный сигнал на противоположный, инвертированный сигнал выдают по отдельному выходу.

Сущность работы устройства заключается в следующем.

На выходе порогового селектора в результате нелинейной обработки.из совокупности входных разностных аналоговых сигналов формируют совокупност ь си гналов (символов ), я вляющуюся первой грубой оценкой избыточного сигнала. Из аналогового разностного сложного сигнала с помощью решающегс! блока формируют также двоичную кодо- вую комбинацию единичного веса, отображающую вектор наиболее вероятной ошибки. Номер единичного символа в этой комбинации соответствует номеру ошибочного символа в комбинации первой грубом оценки с определенной вероятностью, что учитывается алгоритмами функционирования известного и предлагаемого устройств. Комбинация ®0 ошибки хранится а выходном регистре решающего блока, а первая грубая оценка хранится в первом двоичном регистре до тех пор, пока в декодер@ осуществляется декодирование комбина- 15 ции первой грубой оценки, По оконча" нии этого процесса из указанных регистров последовательно через логический блок считываются двоичные комбинации. На выход логического щ блока проходят без изменения асе двоичные символы комбинации первой грубой оценки за исключением одного символа, которому соответствует единичный символ комбинации, считыаае- 25 ной из выходного регистра решающего блока.

Предлагаемый алгоритм не требует использования второго двоичного регистра, а вместо сложного блока сумматоров по модулю два применяют простой логический блок; Остальные операции такие же как и в известном устройстве, Устройство для отработки избыточной

35 информации работает следующим образом.

Составной сигнал с избыточностью из канала связи поступает в лриемник 4

40 где преобразуется в выходную совокупность разностных элементарных аналоговых величин Х =- (Хт, Х, Х, ...,Х ), где h - количество элементарных сигналов в составном избыточном сигнале или количестso двоичных

45 символов в комбинации избыточного кода. Эта аналоговая комбинация Х запоминается а буферном блоке 2 памяти. Далее аналоговые сигналы X.

1 поступают на вход порогового селекто-5О ра 3, который преобразует их в двоичные сигналы (символы ) У;/; = 1„п/.

Двоичные сигналы У„. подаются в двоичный регистр 7 и на вход декодера 4, который отождествляет двоичную кодовую комбинацию У (У, У2, У, У„ ) с ближайшей выходной разрешен" .ной двоичной кодовой комбинацией У;

3Td комбйнация э аписы аает ся и хранит cR( а блоке 5 регистров памяти.

Из буферного блока 2 памяти аналоговые разностные сигналы также параллельно считываются в формирователь

8, в котором определяется наименьший иэ аналоговых сигналов. На выходе формирователя 8 формируется двоичная кодовая комбинация, в которой единичный символ находится в разряде с тем же номером, что и наименьший аналоговый символ. Другие (r — 1) разрядовнулеаые. Эта двоичная кодовая комбинация единичного веса запоминается в выход@зм двоичном регистре формирователя 8.

После того, как процесс декодирования а декодере 4 заканчивается из двоичного регистра 7 и регистра формирователя 8 в преобразователь

10 подаются синхронные двоичные кодовые комбинации. На выходе преобразователя 10 формируется вторая грубая оценка (двоичная кодовая комбинация ) избыточного сигнала. Эта комбинация отличается от комбинации, первой грубой оценки в разряде, номер которого совпадает с номером наименьшего .по амплитуде аналогового символа, Процесс преобразования первой оценки ао вторую следующий. С выхода двоичного регистра 7 комбинация последовательно поступает на информационные входы ключей 11 и 12. Управляются ключи двоичными символами, поступающими с выхода (последовательно ) решающего блока на вход триггера 13.

Если на вход триггера 13 поступает нулевой сигнал, то открыт ключ 11.

Если на вход триггера подается единичный сигнал, то ключ 11 закрывается, ключ 12 открывается и соответствующий информационный сигнал, изме" няясь на противоположный, с помощью инвертора 14 поступает на выход преобразователя 10. Выходные сигналы логического блока через элемент ИЛИ

9 поступают. на вход декодера 4, в котором отождествляются с разрешенной двоичной кодовой комбинацией.

Эта комбинация запоминается в блоке

5 регистров памяти, В блок 6 сравнения поступают точ:ная оценка избыточного сигнала Х, считываемая из блока 2, и двоичные разрешенные кодовые комбинации У

1 и У . В блоке 6 определяется: какая иэ двух разрешенных комбинаций больше

10324уо

Фиг.2

Составитель Н. Бочарова

Редактор А. Ворович Техред М;Надь Корректор О. Билак

Заказ 5404/53 Тираж 618 Подписное .ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

7 соответствует сигналу точной оценки

Х. Эта комбинация по управляющему сигналу, вырабатываемому в блоке 6, считывается из блока 5 на выходе уCTpOHCTB8. 5

Таким образом, в предлагаемом устройстве без сложного блока сумматоров по модулю два, а также второго двоичного регистра удалось реализовать прием составных избыточных сигналов в целом.

Новый алгоритм также пригоден для обработки- составных сигналов с избыточностью, формируемых и на основе недвоичных избыточных кодов.

f5

Предлагаемое устройство для обработки избыточной информации обладает более высокими технико-экономическими показателями по сравнению с известным устройством. 20

Техническое преимущест во изобретения по сравнению с базовым объектом заключается в отсутствии блока сумматоров по модулю два и двоичного регистра. 25

Положительный эффект, который может быть получен в результате использования предлагаемого изобретения по сравнению с известным устройством, состоит в упрощении алгоритма функцид" нирования всего устройства, а также в улучшении его технологичности, повышении экономичности и надежности.

Косвенно ориентировочный выигрыш в ячейках памяти может быть определен следующим образом.

Пусть в блоках 2, 7 - 10 известного устройства содержится no h двоичных ячеек. В предлагаемом устройстве в блоках 9 и 10 такого количества ячеек памяти нет. Следовательно, ориентировочный выигрыш равен

5 403, 2

tl что свидетельствует о более простой конструкции нового устройства по сравнению с известным.